# SECURING COMPUTATIONS WITH GPUS

| Jun Duan                  |                |             |

|---------------------------|----------------|-------------|

|                           |                |             |

|                           |                |             |

|                           |                |             |

|                           |                |             |

|                           |                |             |

| APPROVED I                | BY SUPERVISORY | Y COMMITTEE |

|                           |                |             |

| Kevin W. Ham              | nlen, Chair    |             |

| Kevin W. Ham  Gopal Gupta | nlen, Chair    |             |

| Gopal Gupta               |                |             |

|                           |                |             |

Copyright © 2021

Jun Duan

All rights reserved

## SECURING COMPUTATIONS WITH GPUS

by

JUN DUAN, BS, MS

## DISSERTATION

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

# DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

THE UNIVERSITY OF TEXAS AT DALLAS  $$\operatorname{May}\ 2021$

## ACKNOWLEDGMENTS

First, the author feels forever grateful to his advisor, Dr. Kevin W. Hamlen, for all the guidance, inspiration and support through the whole program. The professor's wisdom enlightens the author in so many ways. He detangles situations and offers him perspicuous explanations no matter how baffling they are. His logical thinking inspires the author to reason on facts elegantly when he approaches problems. His persistence and passion for his work encourages the author to do the same in the future. His light sense of humour makes every meeting with him relaxing and pleasant. The author is really blessed to have been working with him. Without any of those, he would not achieve this academic accomplishment.

The author is very thankful to the other two co-authors of the past publications in the PhD degree program. His teammate Benjamin Ferrell is a sincere friend of the author's and always treats projects in earnest. The professor Dr. Kang Zhang is thoughtful and warm-hearted. He gives insightfull opinions and patiently discusses every detail with the author in the work. The author also thanks the members of the supervising committee of his dissertation: Dr. Gopal Gupta, Dr. Murat Kantarcioglu, and Dr. Shuang Hao for their time to review his dissertation and attend his exams. He is also grateful to Dr. Bhavani Thuraisingham, Ms. Rhonda Walls, and Mr. Douglas Hyde for all the assistance on administrative affairs in the program.

He thanks all the great friends and colleagues whom he knows through the program: Wenhao Wang, Huseyin Ulusoy, Xiaoyang Xu, Erman Pattuk, Shamila Wickramasuriya, Masoud Ghaffarinia, Gilmore Lundquist, Erick Bauman, Imrul Anindya, Yasmeen Alufaisan, Frederico Araujo, Meera Sridhar, Harichandan Roy, and Dakota James Fisher. This journey would not be this wonderful without them.

The author, foremost, expresses his deep gratitude to his family. They share every predicament which they endure and every moment of joy which they celebrate. Without their support, the author could not reach the goals of his life.

The research work herein is supported in part by ONR award N00014-17-1-2995, NSF award #1513704, #1054629, AFOSR award FA9550-14-1-0173, an NSF I/UCRC award from Lockheed Martin, and an endowment from the Eugene McDermott Foundation. The author thanks all the above-mentioned funders for their support through the program. Any opinions or recommendations expressed are those of the author and not necessarily of the above supporters.

Last but not least, the author thanks The University of Texas at Dallas and Department of Computer Science very much for offering him this invaluable opportunity and perfect environment to study and live here and make him an amazing experience at the last stop of his student life.

April 2021

SECURING COMPUTATIONS WITH GPUS

Jun Duan, PhD

The University of Texas at Dallas, 2021

Supervising Professor: Kevin W. Hamlen, Chair

Many modern computers have two diverse computing models baked-in: CPUs and GPUs.

The diversity of these computing models arises from their historically disparate purposes:

Early CPU designs focused on rapidly executing sequences of scalar operations, whereas

GPU designs have focused on computing matrices (e.g., of pixels) through highly parallel

computation. This dissertation proposes that this natural computational diversity has a

secondary benefit that has gone underutilized: the potential to harden computations on both

CPUs and GPUs against cyberattacks, and to elevate assurance of computational correctness,

safety, and security through simultaneous CPU-GPU computation.

To explore this thesis, the dissertation first addresses the challenge of bringing machine-

checked formal methods assurances and tools to the domain of GPU architectures and

computations. A prototype framework for formal, machine-checked validation of GPU

pseudo-assembly code algorithms using the Coq proof assistant is therefore presented and

discussed. The framework is the first to afford GPU programmers a reliable means of formally

machine-validating high-assurance GPU computations without trusting any specific source-

to-assembly compilation toolchain. A formal operational semantics for the PTX pseudo-

assembly language is expressed as inductive, dependent Coq types, facilitating development

of proofs and proof tactics that refer directly to compiled PTX object code.

vii

Secondly, a method of detecting malicious intrusions and runtime faults in software is proposed, which replicates untrusted computations onto the diverse but often co-located instruction architectures implemented by CPUs and GPUs. Divergence between the replicated computations signals an intrusion or fault. A prototype implementation for Java demonstrates that the approach is realizable in practice, and can successfully detect exploitation of Java VM and runtime system vulnerabilities even when the vulnerabilities are not known in advance to defenders. It is shown that GPU parallelism can be leveraged to rapidly validate CPU computations that would otherwise exhibit unacceptable performance if executed on GPU alone.

Finally, GPU-based security is explored at the application level through the introduction of a computational methodology for reorienting, repositioning, and merging camera positions within a region under surveillance, so as to optimally cover all features of interest without overburdening human or machine analysts with an overabundance of video information. This streamlines many video monitoring applications, which are often hampered by the difficulty of manually identifying the few specific locations or frames relevant to a particular inquiry from a vast sea of scenes or recorded video clips. The approach ameliorates this problem by considering geographic information to select ideal locations and orientations of camera positions to fully cover the span without losing key visual details.

# TABLE OF CONTENTS

| ACKNO  | OWLED   | OGMENTS                                   | V    |

|--------|---------|-------------------------------------------|------|

| ABSTR  | ACT     |                                           | vii  |

| LIST O | F FIGU  | JRES                                      | ciii |

| LIST O | F TAB   | LES                                       | κiv  |

| СНАРТ  | ER 1    | INTRODUCTION                              | 1    |

| 1.1    | Forma   | l Validation & GPUs                       | 1    |

| 1.2    | Pros &  | Cons of Machine-validating GPU Assemblies | 3    |

| 1.3    | N-vari  | ant Systems                               | 4    |

| 1.4    | Execu   | tion Divergence between CPUs and GPUs     | 5    |

| 1.5    | Survei  | llance & Camera Positioning               | 6    |

| 1.6    | Insight | t into our work                           | 7    |

|        | 1.6.1   | CUDA au Coq                               | 7    |

|        | 1.6.2   | J-Gang                                    | 7    |

|        | 1.6.3   | VisualVital                               | 8    |

|        | 1.6.4   | Roadmap                                   | 9    |

| СНАРТ  | TER 2   | CUDA AU COQ                               | 10   |

| 2.1    | Overvi  | iew                                       | 10   |

| 2.2    | Backgr  | round                                     | 12   |

| 2.3    | Techni  | ical Approach                             | 13   |

|        | 2.3.1   | Data Types                                | 13   |

|        | 2.3.2   | Memory                                    | 13   |

|        | 2.3.3   | Registers                                 | 15   |

|        | 2.3.4   |                                           | 16   |

|        | 2.3.5   | Operands                                  | 16   |

|        | 2.3.6   | Instructions                              | 17   |

|        | 2.3.7   | Threads                                   | 17   |

|        | 2.3.8   | Warps                                     | 18   |

|        | 2.3.9   | Blocks                                    | 19   |

|       | 2.3.10 | Grids                         | 21 |

|-------|--------|-------------------------------|----|

| 2.4   | Examp  | ole Validation Results        | 21 |

|       | 2.4.1  | Context Lifting               | 22 |

|       | 2.4.2  | Proof Procedure               | 24 |

|       | 2.4.3  | Non-deterministic Execution   | 30 |

| 2.5   | Summ   | ary                           | 33 |

| СНАРТ | ER 3   | J-GANG                        | 34 |

| 3.1   | Overvi | ew                            | 34 |

| 3.2   | System | n Design                      | 35 |

|       | 3.2.1  | Divergence Between Executions | 35 |

|       | 3.2.2  | Model & TCB                   | 38 |

|       | 3.2.3  | GPU Feature Limitations       | 40 |

|       | 3.2.4  | Validation Modes              | 41 |

|       | 3.2.5  | Checkpointing                 | 41 |

|       | 3.2.6  | Translation                   | 43 |

|       | 3.2.7  | Verification Time Complexity  | 44 |

| 3.3   | Implen | mentation                     | 46 |

|       | 3.3.1  | Source Language Limitations   | 48 |

|       | 3.3.2  | Bytecode Analysis             | 49 |

|       | 3.3.3  | Primitives & References       | 50 |

|       | 3.3.4  | State Consistency             | 50 |

|       | 3.3.5  | GPU-based Verification        | 51 |

|       | 3.3.6  | Code Pruning                  | 52 |

| 3.4   | Evalua | ation                         | 55 |

|       | 3.4.1  | Running Efficiency            | 55 |

|       | 3.4.2  | Verification and Correctness  | 58 |

| 3.5   | Summ   | ary                           | 61 |

| СНАРТ | ER 4   | VISUALVITAL                   | 63 |

| 4 1   | Overvi | PW                            | 63 |

|    | 4.2  | Introd  | uction                      | 63 |

|----|------|---------|-----------------------------|----|

|    | 4.3  | Notion  | ns & Models                 | 65 |

|    |      | 4.3.1   | Observation Model           | 65 |

|    |      | 4.3.2   | Weight Model                | 66 |

|    |      | 4.3.3   | Camera Projection Model     | 67 |

|    |      | 4.3.4   | Problem Formulation         | 69 |

|    | 4.4  | Algori  | thm Design                  | 70 |

|    |      | 4.4.1   | Lossless Weight Set         | 70 |

|    |      | 4.4.2   | Points Constricted Set      | 72 |

|    | 4.5  | Simula  | ation                       | 76 |

|    |      | 4.5.1   | Experiment Setup            | 76 |

|    |      | 4.5.2   | Performance                 | 77 |

|    |      | 4.5.3   | Analysis                    | 79 |

|    |      | 4.5.4   | Time Complexity             | 80 |

|    | 4.6  | Summ    | ary                         | 80 |

| СН | APT  | ER 5    | RELATED WORK                | 82 |

|    | 5.1  | Execut  | tion Variance               | 82 |

|    | 5.2  | Hetero  | ogeneous Computing          | 83 |

|    | 5.3  | Verific | ation                       | 84 |

|    | 5.4  | Datafle | ow Analysis                 | 85 |

|    | 5.5  | Correc  | etness in GPGPU             | 85 |

|    | 5.6  | Data I  | Race & Divergence           | 87 |

|    | 5.7  | Visual  | Models                      | 88 |

|    | 5.8  | Virtua  | l Reality                   | 89 |

|    | 5.9  | Algori  | thms on Tracking & Coverage | 90 |

|    | 5.10 | Mappi   | ng Services                 | 91 |

| СН | APT  | ER 6    | CONCLUSION                  | 93 |

| ΑP | PEN  | DIX I   | MODELS AND PROOFS           | 95 |

|    | Δ 1  | PTY N   | Model in Chapter 2          | 05 |

| A.2    | SDV Rules for lock steps in Chapter 2                 | 102 |

|--------|-------------------------------------------------------|-----|

| A.3    | Proof of Theorem 1 in Chapter 4                       | 106 |

| A.4    | The optimal position for a single camera in Chapter 4 | 107 |

| BIBLIO | GRAPHY                                                | 110 |

| BIOGRA | APHICAL SKETCH                                        | 122 |

| CURRIC | CULUM VITAE                                           |     |

# LIST OF FIGURES

| 2.1 | Warp Small-Step Semantics                                                                                                                           | 20  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Warp Sync Function                                                                                                                                  | 21  |

| 2.3 | Thread Block Small-Step Semantics                                                                                                                   | 21  |

| 2.4 | Grid Small-Step Semantics                                                                                                                           | 22  |

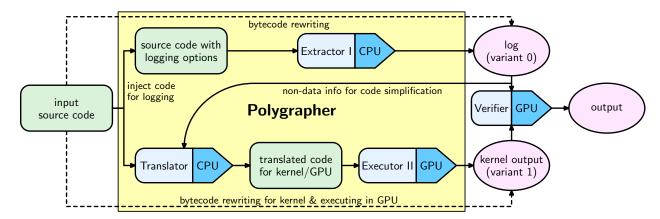

| 3.1 | J-Gang Architecture                                                                                                                                 | 38  |

| 3.2 | Semantic transparency                                                                                                                               | 39  |

| 3.3 | Translation of Java source to CPU×GPU code                                                                                                          | 43  |

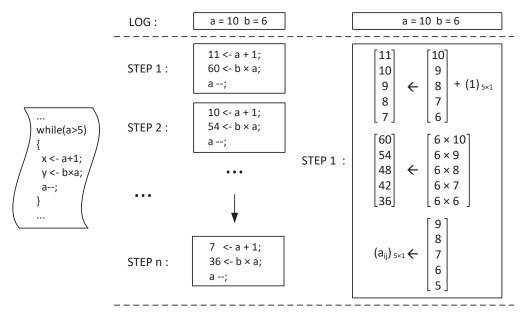

| 3.4 | J-GANG computations for CPU (left) vs. GPU (right)                                                                                                  | 45  |

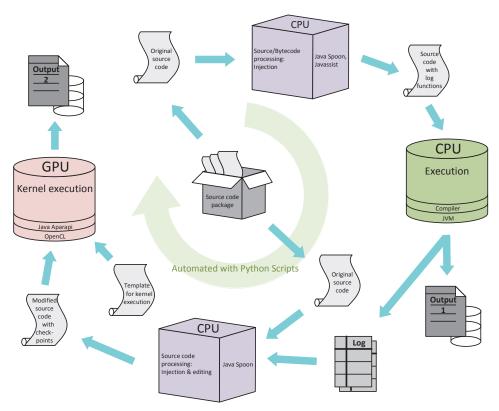

| 3.5 | Procedure of variants generation and execution                                                                                                      | 46  |

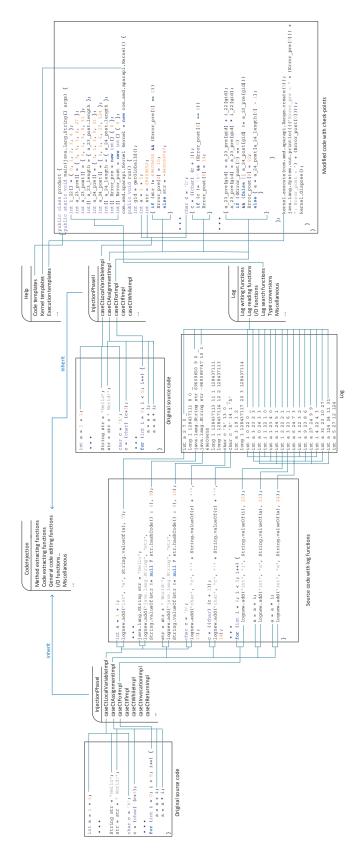

| 3.6 | Code and checkpoints generation procedure                                                                                                           | 47  |

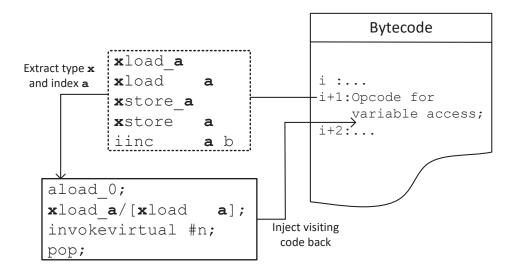

| 3.7 | Bytecode injection to dynamically visit a variable                                                                                                  | 49  |

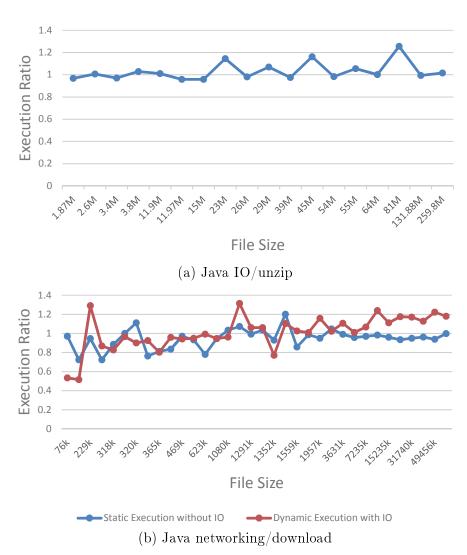

| 3.8 | Experimental results with utility applications as input                                                                                             | 53  |

| 3.8 | Experimental results with utility applications as input (cont.)                                                                                     | 54  |

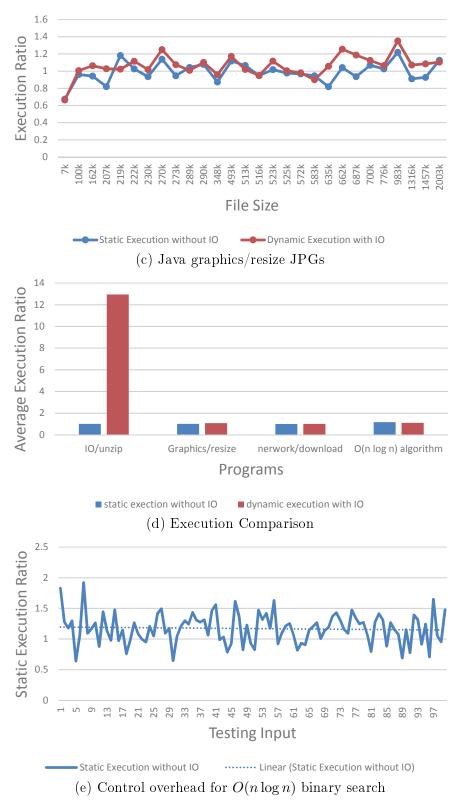

| 4.1 | Complete presentation for an observation and related notions (a) Basic observation (b) Simplified observation with projections                      | 66  |

| 4.2 | Accumulation for the calculus step                                                                                                                  | 68  |

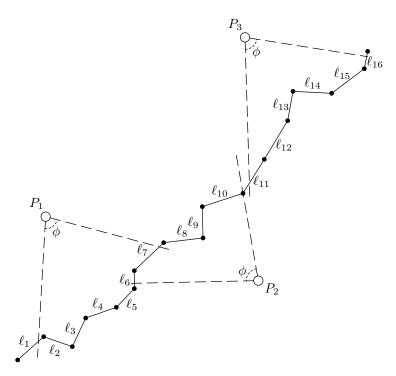

| 4.3 | Camera $c$ observes poly-line $L$ at different positions $P_1, P_2, P_3 \ldots \ldots$                                                              | 69  |

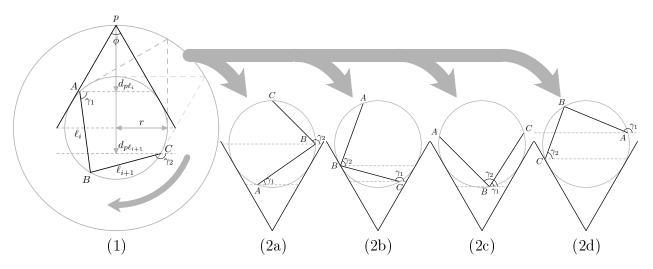

| 4.4 | (1) All possible situations of camera view, and (2) four different angle relations between $\gamma_1$ and $\gamma_2$                                | 71  |

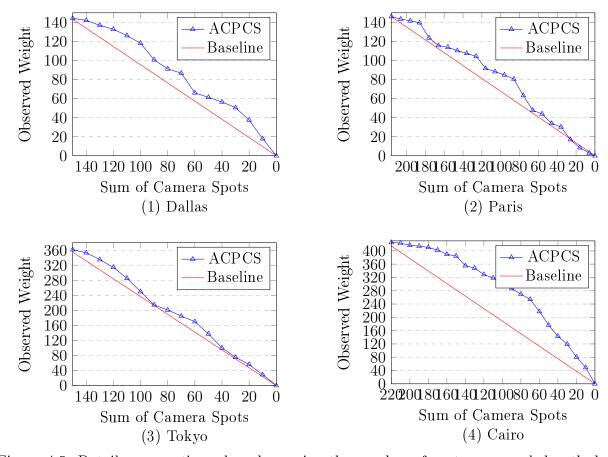

| 4.5 | Detail-preservation when decreasing the number of spots on sampled path data from four different cities (Dallas, Paris, Tokyo, Cairo)               | 78  |

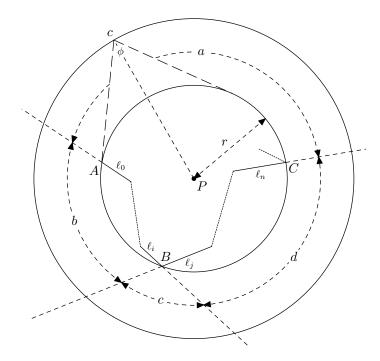

| A.1 | The orbit boundaries of camera $c$ when $c$ moving along the circle $\bigcirc p'$ . It is for calculating the local extramum of the observed weight | 107 |

# LIST OF TABLES

| 3.1 | Performance evaluation of Java algorithms using J-GANG. Partial granularity |    |

|-----|-----------------------------------------------------------------------------|----|

|     | omits verifying trusted API methods                                         | 53 |

| 3.2 | Tested bugs                                                                 | 59 |

| 4.1 | Routes Information                                                          | 77 |

#### CHAPTER 1

#### INTRODUCTION

This chapter introduces the prevalent viewpoints and current problems in the related research fields, and positions this dissertation within that landscape. It first considers the status of formal Verification & Validation (V&V) research with respect to GPUs, arguing that there is a paucity of such work for formal GPU computation verification. It then introduces the classic concept of n-variant systems for computer security, and posits that CPU-GPU computational diversity offer exceptional promise as a practical foundation for realizing n-variant assurances in modern computing systems. Finally, research problems around camera surveillance are shown as possible applications in CPU and GPU hybrid scenes. The chapter concludes with some insights of the author's work and an overview of the remainder of the dissertation.

#### 1.1 Formal Validation & GPUs

Machine-checked formal verification of software has become the gold standard for developing high-assurance algorithms and implementations. In contrast to unit testing or fuzzing, which can only verify that software in a particular operating environment behaves correctly on a particular (usually finite) set of inputs, formal methods approaches build formal mathematical proofs that establish that the software obeys specified correctness, safety, and security properties for *every* possible environment and input within the (usually infinite) domain admitted by the specification. Unlike manual code reviews, these proofs are checked fully automatically within a mechanized proof environment whose soundness has been verified down to the foundations of mathematics. And unlike model-based verification, the proofs concern the actual software implementation rather than an idealized model of it.

These contrasts are particularly salient when verifying security properties, since cyber criminals have a well established record of success at identifying dangerous inputs that testing

missed, differences between the testing environment and the deployment environment that can be exploited to compromise software, obscure code vulnerabilities that human reviewers overlooked, and inconsistencies between actual software implementations and the models that attempt to approximate them. As a result, formal methods approaches offer significantly higher assurance than these alternatives.

The price of formal methods is typically the much greater effort and expertise required relative to less rigorous approaches. However, the rise of program-proof co-development environments, such as the Coq proof assistant (Bertot and Castéran, 2004), has made machine-validation of larger software systems much more feasible than in previous decades. For instance, in recent years Coq has been used to verify correctness of a full C compiler (Boldo et al., 2013), prove update consistency of software-defined networks (Reitblatt et al., 2012), model significant subsets of both the Intel x86 and the ARMv8 architectures (Flur et al., 2016; Kennedy et al., 2013), validate a machine language certifier for Google's Native Client architecture (Morrisett et al., 2012), and develop the F\* language for secure distributed programming (Swamy et al., 2011), among many other successful applications.

The rise of GPU architectures as general-purpose computing platforms has made it increasingly desirable to make such validation approaches available for GPU algorithms and their implementations, toward developing high-assurance, GPU-based software. Many general-purpose GPU (GPGPU) programming tasks can benefit from such assurance; for example, GPUs are already being leveraged to more efficiently realize cryptography (Yamanouchi, 2007), scan for viruses (Seamans and Alexander, 2007), perform financial computations (Grauer-Gray et al., 2013), spot network intrusions (Alshawabkeh et al., 2010), and even detect underwater seismic faults (Deschizeaux and Blanc, 2007). Unforeseen flaws in these computations could have severe ramifications for users and the general public. Since highly parallelized architectures are notoriously difficult for humans to reason about, it is especially important to develop machine-validation approaches for analyzing the correctness of such software.

## 1.2 Pros & Cons of Machine-validating GPU Assemblies

#### prosandcons

Motivated by this need, we have developed the first encoding of a GPU pseudo-assembly language operational semantics in Coq, and used it to machine-validate some correctness properties of small GPU programs. Our prototype framework targets Nvidia's CUDA platform (though we anticipate that our general approach is extensible to other GPU architectures). In particular, our semantics model a Single Instruction, Multiple Threads (SIMT) architecture with warps, thread blocks, and grids.

In order to minimize the trusted computing base (TCB) of our validation framework, and to offer developers maximum flexibility, theorems and proofs in our framework operate at the level of Parallel Thread eXecution (PTX) pseudo-assembly language computations rather than source code programs. This frees software developers to implement their high-assurance algorithms in any available source language, and use any compilation tools, provided that the tools ultimately yield PTX programs as output.

The downside of this choice, of course, is that proofs must reason at a significantly lower level than source code, and can therefore require extra effort to formulate. We believe this is nevertheless a wise design decision in the long term, because foundational support for PTX can eventually be scaled up to higher levels of abstraction via future development of Coq theories and tactics that modularize and automate much of the proof work for common source idioms. Similar trade-offs have motivated prior work on modeling ISAs of other low-level architectures in Coq (e.g., (Atkey, 2007; Flur et al., 2016; Kennedy et al., 2013)).

As an example of this sort of scaling, a major success of our work is the formulation and validation of the first mechanized proof that CUDA's memory synchronization model ensures transparency of the thread scheduler. In particular, correctness of a computation under the assumption of a deterministic scheduler always implies correctness under a non-deterministic scheduler. This result greatly simplifies proofs of PTX code correctness by eliminating and

abstracting away the non-deterministic scheduler from the sources of parallelism that proofs must consider.

### 1.3 N-variant Systems

While formal methods offers the highest possible assurance that a given software implementation satisfies a given formal specification, many software systems lack any formal (i.e., machine-readable) specification. Their intended functionalities are expressed informally as natural language descriptions, whose imprecision is regularly exploited by adversaries to carry out cyberattacks. Securing this significant body of software therefore necessarily entails less rigorous protections. However, even without a formal specification of correctness, it is often possible to formally specify *inconsistency* of arbitrary software systems, which is a root of many vulnerabilities and critical failures.

N-variant systems (Cox et al., 2006) detect intrusions and other runtime anomalies in software by deploying diverse replicas of the software and monitoring their parallel execution for inconsistencies, which manifest as computational divergences. Divergence between the computations indicates that one or more replicas have exercised functionalities that were unintended by the program's developers, and that were therefore not replicated consistently across all the copies. The n-variant approach has been used for detecting memory corruption vulnerabilities in C/C++ programs (Volckaert et al., 2017), monitoring user-space processes (Salamat et al., 2009), defending data corruption attacks (Nguyen-Tuong et al., 2008), and securing embedded systems (Alkabani and Koushanfar, 2008).

Unfortunately, one major barrier to the realization of effective n-variant systems in practice has been the high difficulty and cost associated with creating and maintaining software copies that are appropriately diverse (not replicating bugs or vulnerabilities), yet consistent (preserving all desired program features). Achieving this can entail employing multiple in-

dependent software development teams, which can potentially multiply the cost and time associated with the project by a factor of n (Avižienis, 1985).

This high cost of independent, manual cultivation of diversity has led to a search for automated software diversity. For example, compilers have been proposed as natural diversity-introduction vehicles (Jackson et al., 2011), since they enjoy a range of options when translating source programs to distributable object code, including various possible object code and process memory layouts. However, many large classes of software attacks exploit low-level details that are fundamental to the target hardware architecture, and that are therefore difficult for compilers to meaningfully diversify. For example, Address Space Layout Randomization (ASLR) defenses, which randomize section base addresses in process memory at load-time, have proven vulnerable to derandomization attacks (Shacham et al., 2004) that exploit the prevalence of relative-address instruction operands in CISC instruction sets to learn the randomized addresses. Similarly, return-oriented programming (Shacham, 2007) and counterfeit object-oriented programming attacks (Schuster et al., 2015) abuse the semantics of return and call instructions, which is difficult to avoid when compiling to architectures with those instruction semantics.

## 1.4 Execution Divergence between CPUs and GPUs

The research in this dissertation is inspired by the observation that modern computing systems increasingly have two very different yet powerful instruction architectures available to them: CPU and GPU. This potential source of computational diversity has gone relatively unutilized as an opportunity to detect malicious software intrusions through n-variant computation. To explore this opportunity, we introduce Java Gpu-Assisted N-variant Guardian (J-GANG), a system that replicates Java computations onto CPU-GPU hybrid architectures and runs them concurrently in order to detect divergence-causing intrusions.

GPU computing models differ substantially from typical CPU computing models. This diversity offers many attractive opportunities for robust intrusion detection, but is also a source of significant technical challenges. For example, GPU architectures often suffer poor performance on computations with few threads; their advantages are only seen on computations with hundreds or thousands of simple but independent workloads. However, most CPU computations offer only limited parallelism on the order of a few threads. This makes running CPU computations in a brute-force fashion on GPUs impractical; it risks bottlenecking the system by lagging the GPU variant hopelessly behind the CPU variant, reducing both to a crawl.

To address these challenges, our research proposes a novel "trust but verify" n-variant architecture wherein GPU computations enjoy increasing parallelism opportunities the farther they lag behind CPU computations. This offers the former a means to keep pace with even the most serial workloads, allowing the framework to secure a broad domain of realistic computations without introducing unacceptable performance overhead.

## 1.5 Surveillance & Camera Positioning

Visual surveillance and camera positioning is a prime example of security-sensitive GPU computation in practice. This dissertation considers GPU computational security within the context of physical security by presenting a secure algorithm for positioning and orienting a limited number of video monitoring devices so as to maximize the information gain on the status of a pre-mapped route. The approach accommodates contexts in which both cameras and objects are mobile, and considers several applications, including VR scene generation, optimizing traffic monitoring to minimize coverage loss, audiovisual fingerprinting, and automatic scene detection.

## 1.6 Insight into our work

## 1.6.1 CUDA au Coq

Our work, CUDA au Coq (Ferrell et al., 2019), complements related works on GPU software debugging through unit testing (Holey et al., 2013; Zheng et al., 2011) or heuristic static analysis of source code (Coutinho et al., 2011) by offering a higher level of assurance than these traditional approaches can provide, but at the cost of (possibly significant) extra validation effort. That is, we anticipate that a typical development workflow for high-assurance GPU software should first employ these heuristic debugging techniques to identify and fix any demonstrable flaws, and then proceed to apply formal methods machine-validation to obtain complete proofs of correctness. Our work is an alternative to any runtime or hybrid fault detection approaches (Li et al., 2014; Zheng et al., 2011), since it imposes no runtime overhead (all validation is strictly static), and yields a priori guarantees that span the universe of all possible execution traces for verified code.

#### 1.6.2 J-Gang

Our approach, J-Gang (Duan et al., 2019), therefore instead adopts an asynchronized model in which the CPU variant runs at full speed, logging its results at selected program *check-points* in the form of JVM state snapshots. A sequence  $(\sigma_0, \ldots, \sigma_k)$  of such snapshots can be replicated and validated by a GPU using k concurrent workers, each of which validates the  $(\sigma_i, \sigma_{i+1})$  portion of the computation by starting at state  $\sigma_i$  as a pre-condition and confirming that it reaches state  $\sigma_{i+1}$  as a post-condition  $(\forall i \in 0..k-1)$ . The computation is correct only if all these fragments pass validation. This allows the GPU to catch up to the CPU computation in spurts—the more it lags behind, the more opportunity for parallelism arises, since it can greedily consume more snapshots and validate them concurrently.

The high dissimilarity between GPU and CPU models of Java computation state allow J-GANG to detect many important vulnerability classes. For example, attacks that exploit

memory corruption vulnerabilities to hijack return addresses on the stack have a different effect upon GPU computations, since the GPU model has no explicit call stack with in-memory return addresses to corrupt. Moreover, our detection approach conservatively assumes that all exploited vulnerabilities are unknown to defenders (zero-days). No explicit knowledge of vulnerabilities is used to avoid preserving them in the GPU replica; divergences arise purely from the natural dissimilarity between the two instruction architectures.

#### 1.6.3 VisualVital

Unlike prior work on related problems (see Chapter 5), our goal in the VisualVital (Duan et al., 2017) project is to retain and maximize overall information related to world status, not to specialize for a particular, known detail or event. For instance, prior work on traffic monitoring has demonstrated the effectiveness of probe vehicles and smart-phones for helping users avoid specific, known problem states (e.g., traffic congestion) (Astarita et al., 2014; Hoh et al., 2012); and Virtual trip lines (Hoh et al., 2008) can help travelers choose effective routes. But such approaches are not as applicable to identifying and analyzing arbitrary event details in which the user's interest cannot be predicted in advance (e.g., terrorist attack details whose relevance only become evident afterward). Our problem also generalizes beyond traffic scenarios.

Specifically, we consider the problem of observing a route (consisting of many segments, each with differing relevant details labeled) with a limited number of camera positions, so as to maximize the overall details observed by selecting optimal positions for the cameras. Each camera must fit in the model from the real world—the level of detail observed by each camera is inversely related to its geometric distance from the object. To maximize the overall information, we invent a method to first maximize local details with sufficient positions, and then gradually merge the selected positions to decease the camera count until it meets a desired target threshold.

## 1.6.4 Roadmap

The reminder of this dissertation is arranged as follows. Chapter 2 presents CUDA au Coq, the framework for machine-validating GPU assembly programs. Chapter 3 presents J-Gang, the *n*-variant framework of verification for Java source code on CPU and GPU hybrid platform. Chapter 4 presents VisualVital, the observation model for multiple sections of scenes. Chapter 5 lists all the related work. Chapter 6 concludes. At last, Appendix shows in details about the source code of Coq for the CUDA au Coq project, including the code and proofs of the PTX model, and explanation and proofs of the observation model for the VisualVital project.

### CHAPTER 2

## $CUDA AU COQ^{1}$

#### 2.1 Overview

Motivated by the importance of the correctness of software with parallel features and the extreme difficulties it poses for human reasoning without automated assistance, this chapter presents the GPU computation model encoded in Coq proof system and the procedures of validating parallel programs by machine. Nvidia's CUDA platform is selected as the target architecture, and we here limit our attention to the SIMT architecture, including SIMD. Architectures with mixed parallel features, such as Multiple Instruction, Multiple DATA (MIMD) or (Simultaneous Multithreading) SMT, are reserved for future work.

To build the model in Coq, the layer structures of CUDA's parallel computation, such as warps, thread blocks, and grids, are defined and rules of computation are dependently created and proved. The correctness of the model is listed in the contributions and shown in following sections. CUDA'S Intermediate Representation (IR), PTX, offers a unification of high-level languages running above it, so performing verification at the PTX level minimizes the Trusted Computing Base (TCB) of the system. The framework hence accommodates any high-level language that CUDA supports; code developers need only supply the low-level (compiled) code to check the correctness through this model. Our goal in this project is to offer a semi-automated framework whereby a human expert can write machine-checked proofs of PTX code properties. Automation of the proof search effort is the subject of related research.

Our prototype implementation in Coq includes 350 SLOC for the PTX model, 300 SLOC for theorems, and 140 SLOC of Ltacs. It is beneficial for our model to be as small as

<sup>&</sup>lt;sup>1</sup>The material in this chapter was originally published as: Benjamin Ferrell, Jun Duan, and Kevin W. Hamlen, "CUDA au Coq: A Framework for Machine-validating GPU Assembly Programs," In *Proceedings* of the 26th Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 474–479, March 2019.

possible in order to minimize the TCB. However, there is no limit necessitated on the number of theorems, as these only strengthen the implementation and shorten proofs without contributing to the TCB.

In summary, our contributions are as follows:

- We present the first machine-checkable formal validation framework for a GPU architecture, using the Coq proof assistant.

- Our framework formalizes Nvidia's CUDA architecture and the PTX pseudo-assembly instruction set as Coq inductive types and definitions, for formal deductive reasoning in Coq's interactive proof environment.

- The formalization supports all major forms of CUDA parallelism, including threads, warps, thread blocks, and grids. (Non-standardized, implementation-defined characteristics of the architecture are intentionally not modeled, so that proofs must establish correctness independently from architectural idiosyncrasies that may be unreliable across GPUs.)

- We proved and machine-validated a theorem establishing that CUDA's memory synchronization model successfully makes thread scheduling details transparent to PTX programs. Thus, correctness proofs can consider a simplified architectural model in which the scheduler is deterministic.

- Example theorems and proofs demonstrate how our prototype can be applied successfully to small but realistic GPU programs.

We proceed as follows: Section 2.2 begins with background material on the CUDA architecture that undergirds our approach to the formalization. Our formalized PTX semantics are presented in Section 2.3. Example theorems and proofs that demonstrate the utility of our formalization follow in Section 2.4. Section 2.5 summarize the chapter.

## 2.2 Background

Our semantics are based on PTX, which is an intermediate assembly language either produced from compiling CUDA C/C++ code or manual encoding. As a common instruction set with well-documented semantics, PTX insulates developers from the constantly evolving details of each new GPU hardware release. It is the lowest intermediate representation that abstracts away from GPU-specific details that cannot be relied upon for forward compatibility.

At run-time, the intermediate assembly language is further compiled by the device driver down to the appropriate machine code, which is then executed on the device. Since our focus is on PTX, we are not concerned with the CUDA to PTX compilation process, but we do trust the final PTX to machine code compilation process. PTX is well documented (nVIDIA, 2015) so our goal is to formalize its execution semantics in Coq in a clean, succinct fashion conducive to writing tractable proofs.

At a high level, CUDA GPUs systematically execute millions of threads to accomplish a task. The number of threads spawned is defined by two user-configurable parameters, grid\_size and block\_size, which are 3-dimensional vectors. When a job is dispatched to the GPU, a grid\_size array of thread blocks are spawned with each thread block containing a block\_size array of threads.

Thread blocks are scheduled to execute on various streaming multiprocessors (SMs). A GPU typically contains multiple SMs, which are each composed of one or more CUDA cores (ALUs), Load/Store units, and special function units. When a block is scheduled on an SM, threads are grouped into warps (sets of 32 threads) and scheduled for execution. Each time a warp executes an instruction, all threads do so in lock-step.

GPU memory is also hierarchically structured. At the top level are *global* and *constant* memory, to which all threads have access. SMs have a section of cache-like memory called

shared memory, to which all threads in the same thread block have quick access. At the bottom level are local and register memory, which each thread has in a private section.

## 2.3 Technical Approach

To describe our formal PTX model, we start from the bottom and work upward. It includes data types, registers, special registers, operands, memory, instructions, threads, warps, blocks, and grids. For this prototype, we currently support succinct PTX functions and try to add more to make the concept more complete. First we introduce abstract definitions with basic types of the Coq system. For a complete definition of our model in Coq, see the appendix.

## 2.3.1 Data Types

As the most basic units for this model, we model PTX types dty within Coq as a sum type consisting of unsigned integers (UI), signed integers (SI) and byte data (B), each parameterized by a bit width w.

$$w: \mathbb{N}$$

$$dty: \{UI, SI, BD\} \times \mathbb{N}$$

An ID *id* is a label to uniquely mark a storing unit or differentiate operational modules in the system.

$$id: \{\mathrm{Id}\} \times \mathbb{N}$$

## 2.3.2 Memory

In order to properly capture how GPU memory semantically operates, there are a couple of elements to consider.

First, GPU memory is made up of different sections, or *state-spaces* (ss), each of which have a specific purpose. Due to its accessibility for threads and some restrictions, some memory can be manipulated by only one specific thread, some can be shared by the threads inside the same block, some can be only readable, and the others have well-defined features for more purposes. We will focus on three types state-spaces for memory: global, const, and shared.

**global** memory can be read or written by all threads, and there is no hardware synchronization mechanism restricting accesses.

**const** memory is read-only and shared by all threads.

**shared** memory can be read or written by all threads in the same block, and hardware synchronization is performed through memory barriers.

To match each type with an address, we model memory addresses addr as location-accessability pairs.

$$bid: \mathbb{N} \times \mathbb{N} \times \mathbb{N}$$

$$ss: \{Global, Const, Shared\} \times bid$$

$$addr: ss \times \mathbb{N}$$

Second, many memory transactions are performed during execution without any explicit order, possibly introducing memory synchronization errors.

Taking into consideration these two items, we define memory  $\mu$  to be a mapping from state-space and address to byte and boolean. The boolean value specifies whether a byte is valid or could possibly still be in flight—similar to a valid bit for cache memory.

$$\mu: (ss \times addr) \to (byte \times \mathbb{B})$$

At the launch of a program, only global and constant memory may have data, and their valid bits are set to true. During execution, global memory periodically updates as values are stored. Its valid bits are always false, since the hardware does not guarantee memory synchronization (excepting atomic instructions).

GPUs leverage data-independence to achieve high parallelism, so proper global memory synchronization is often a prerequisite for code correctness. This is a perennial source of GPU algorithm bugs, so our memory formalization is designed to support formal verification of such properties.

Thread intercommunication is possible only in thread blocks with the use of shared memory, which can be synchronized by barriers. A thread block performs some computation and threads begin to arrive at a barrier and wait. Once all threads have reached the barrier, the values stored in shared memory during this time are guaranteed to be valid when execution resumes. To model this, our semantics initially set a value's valid bit to false and switch to true when the entire block has reached the barrier.

## 2.3.3 Registers

PTX code computes with four different data types: unsigned integers, signed integers, floats, and untyped bytes. In this work we only consider unsigned (UI) and signed integers (SI), but our approach can be extended to include all data types.

Threads are allocated a private register file which contains a set PTX registers. A register (reg) holds temporary values during execution, and is uniquely identified by its data type, bit width, and index. We define the register file  $\rho$  to be a mapping from registers to integers.

$$reg: \{UI, SI\} \times \mathbb{N} \times \mathbb{N}$$

$$\rho: reg \to \mathbb{Z}$$

During program execution, not all SIMT threads follow the same path. Threads maintain a set of predicate registers, which optionally prefix any instruction and indicate whether it should be executed or skipped. The case where the predicate is false is semantically equivalent to a Nop. In our implementation, we only consider branch instructions to optionally have prefixed predicates, so we introduce a pseudo-instruction to distinguish these from non-predicated branches. Coupled with the register file is a *predicate state*  $\varphi$ , which maps predicate indexes to boolean values.

$$\varphi: \mathbb{N} \to \mathbb{B}$$

### 2.3.4 Special Registers

Special registers contain static information about the grid configuration and a thread's location (i.e., index). They are unique to GPUs, and are useful when delegating work to each thread. There are four predominant special registers, each a 3-dimensional vector: the thread-index (T), block-index (B), block-size (NT), and grid-size (NB). Every thread has a unique combination of thread-index and block-index, but identical block-size and grid-size.

To model this, our state model includes the following auxiliary function for special registers:

$$dim: \{Dx, Dy, Dz\}$$

$$sreg: \{T, B, NT, NB\} \times dim$$

$$sreg\_aux: tid \rightarrow sreg \rightarrow \mathbb{N} := get\_sreg(tid)$$

## 2.3.5 Operands

The types of instruction operands are are inferred during PTX parsing. We define 4 different types based on the origins of different state spaces to support the compatibility for source and destination operands in our model. Specifically, *Reg. SReg. Imm* and *RegImm* denote register, special register, immediate, and register-immediate operand types, respectively.

Also, there are specific rules to restrict the conversion between different types and source and destination operands of different length.

$$op : reg \uplus sreg \uplus \mathbb{Z} \uplus reg \times \mathbb{Z}$$

#### 2.3.6 Instructions

We next model PTX instructions *instr* within Coq. Instruction parameter types must comply with the syntactic grammar and typing constraints of PTX. Programs running in CUDA can be decompiled into PTX code and translated to fit into our definition.

A program *prg* is modeled as a list of PTX instructions. Operand types within each instruction are checked according to the PTX typing rules translated to Coq. Typing rules for a core subset of instructions are listed in the following definition:

```

Inductive instr :=

| Bop (i:bop) (ty:dty) (d:reg) (a b:op)

| Top (i:top) (ty:dty) (d:reg) (a b c:op)

| Setp (c:cmp) (ty:dty) (p:id) (a b:op)

| Mov (ty:dty) (d:reg) (a:op)

| Ld (stsp:iss) (ty:dty) (d:reg) (a:op)

| St (stsp:iss) (ty:dty) (a:op) (d:reg)

| Bra (tgt:nat)

| PBra (p:id) (tgt:nat)

| Bar | Sync | Nop | Exit.

Definition prg := list instr.

```

#### 2.3.7 Threads

Potentially millions of threads execute on a GPU, so we assign each an enumerated value for unique identification. Proofs do not typically exhaustively enumerate this potentially large

identifier space, of course; the identifiers typically take the form of universally quantified variables in proofs. The identifiers are passed to the auxiliary function in §2.3.4 to obtain the appropriate special registers.

As mentioned in §2.3.3, threads maintain a set of private registers  $\rho$  and predicates  $\varphi$ . Therefore, we define a thread  $\theta$  to be a tuple of these three components.

$$\theta: \mathbb{N} \times \rho \times \varphi$$

In the following semantics, vector  $\vec{t}$  denotes a thread state, including its ID tid, memory state  $\rho$ , and predicate state  $\varphi$ .

## 2.3.8 Warps

A warp is defined as a set of 32 threads, and is the smallest level of granularity to execute on an SM. All threads in a common warp execute the same instruction at the same time (i.e., in lock-step), which is efficient for most instructions except for a predicated branch. With a predicated branch, there is the potential for part of the warp to take the branch and the rest stay behind to execute the next immediate instruction. A warp in this state is called *divergent*, and must now execute the two (or more) paths serially, thereby increasing run-time. At the formal level, we define a warp to be in one of two states: uniform execution of a set of threads or divergent execution of two warps.

```

Inductive warp : Set :=

| Uni (pc:nat) (ts:list thread)

| Div (w1 w2:warp)

```

Hence, warps may form a tree of divergences.

Figure 2.1 lists the small-step semantic rules for warps. The semantics are distinguished by instruction input, which transforms the given warp according to the operational semantics of the instruction. The first 9 rules are fairly straightforward and only apply to uniform

warps. Instructions Bop and Top are arithmetic operations on two and three inputs, respectively. If a warp is divergent and the instruction is not Sync, then the *left*-most warp is executed.

The final case is the most complex due to the synchronization operation. When a warp diverges, it should at some point converge back to a uniform warp through a sync operation (see Figure 2.2). Compilers enforce this because memory barriers can cause undefined execution. In some executions, a warp could diverge with half of it, halting at a barrier while the other half continues to execute and eventually exit. Since all threads must be at the memory barrier in order for it to lift, this situation creates a deadlock and the program hangs or (more likely) crashes. Careful analysis is required to establish that correct code always avoids this situation. Our operational semantic encodings facilitate such reasoning in Coq proofs.

#### 2.3.9 Blocks

Thread blocks are typically defined as sets of threads, but because they are grouped into warps, we formalize them as sets  $\beta$  of warps.

$$\beta: \vec{\omega}$$

Warps are selected by the scheduler to execute an instruction, but the details of the scheduling can vary between GPUs and other contextual factors. Proofs in our framework must therefore establish correctness independently of the scheduling algorithm. Our semantics hence formalize the scheduler non-deterministically.

Looking at Figure 2.3, we have two possible scenarios. In the first scenario, there exists a warp that is not at a memory barrier or has not finished, so it executes its next instruction. Notation  $\beta[\omega'/\omega]$  denotes the capture-avoiding substitution of  $\omega$  with  $\omega'$ , in order to update the block state. The second scenario applies when all warps have reached a memory barrier.

$$\begin{aligned} \overline{\operatorname{Nop}} &\vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t}), \mu \rangle}^{\operatorname{(nop)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho[r \mapsto op(a,b)], \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t}\}}{\operatorname{Bop}\ op\ r\ a\ b \vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t'}), \mu \rangle}^{\operatorname{(hop)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho[r \mapsto op(a,b,c)], \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t}\}}{\operatorname{Top}\ op\ r\ a\ b\ c \vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t'}), \mu \rangle}^{\operatorname{(top)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho[r \mapsto a], \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t}\}}{\operatorname{Mov}\ r\ a \vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t'}), \mu \rangle}^{\operatorname{(mov)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho[r \mapsto \mu(ss,a)], \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t}\}}{\operatorname{Ld}\ ss\ r\ a \vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t'}), \mu \rangle}^{\operatorname{(ld)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho[r \mapsto \mu(ss,a)], \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t}\}}{\operatorname{Ld}\ ss\ r\ a \vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t'}), \mu \rangle}^{\operatorname{(bta)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi(r)) \mid (tid, \rho, \varphi) \in \overrightarrow{t}\} \quad \mu' = \operatorname{update}(\mu, \overrightarrow{v})}{\operatorname{St}\ ss\ a\ r \vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t'}), \mu' \rangle}^{\operatorname{(bra)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi[p \mapsto cmp(a,b]]) \mid (tid, \rho, \varphi) \in \overrightarrow{t}\}}{\operatorname{Setp}\ cmp\ p\ a\ b \vdash \langle (pc, \overrightarrow{t}), \mu \rangle \to_1 \langle (pc+1, \overrightarrow{t'}), \mu \rangle}^{\operatorname{(setp)}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \rho, \varphi) \in \overrightarrow{t} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \varphi) \in \overrightarrow{t'} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \varphi) \in \overrightarrow{t'} \land \varphi_i(p)\}}{\operatorname{Lop}} \\ \frac{\overrightarrow{t'} = \{(tid, \rho, \varphi) \mid (tid, \varphi) \in$$

Figure 2.1: Warp Small-Step Semantics

At this time all shared memory is committed (i.e., all valid bits are set to true), and warp program counters are incremented to continue execution.

$$\operatorname{sync}(\omega) = \begin{cases} (pc+1, \vec{t}), & \text{if } \omega = (pc, \vec{t}) \\ \operatorname{sync}(\omega_2), & \text{if } \omega = ((pc_1, \{\}), \omega_2) \\ \operatorname{sync}(\omega_1), & \text{if } \omega = (\omega_1, (pc_2, \{\})) \\ (pc_1+1, \vec{t_1} \cup \vec{t_2}), & \text{if } \omega = ((pc_1, \vec{t_1}), (pc_2, \vec{t_2})) \\ & \wedge pc_1 = pc_2 \\ (\omega_2, (pc_1, \vec{t_1})), & \text{if } \omega = ((pc_1, \vec{t_1}), \omega_2) \\ (\operatorname{sync}(\omega_1), \omega_2), & \text{otherwise } \omega = (\omega_1, \omega_2) \end{cases}$$

Figure 2.2: Warp Sync Function

$$\frac{\exists \omega \in \beta . \pi(\omega_{pc}) \notin \{\text{Bar, Exit}\}\}}{\pi(\omega_{pc}) \vdash \langle \omega, \mu \rangle \to_{1} \langle \omega', \mu' \rangle} \frac{\pi(\omega_{pc}) \vdash \langle \omega, \mu \rangle \to_{1} \langle \beta[\omega'/\omega], \mu' \rangle}{\pi \vdash \langle \beta, \mu \rangle \to_{1} \langle \beta[\omega'/\omega], \mu' \rangle} (\text{exec}_{b})$$

$$\frac{\forall \omega \in \beta . \pi(\omega_{pc}) = \text{Bar}}{\pi \vdash \langle \beta, \mu \rangle \to_{1} \langle \text{incr\_pc}(\beta), \text{commit}(\mu) \rangle} (\text{lift-bar})$$

Figure 2.3: Thread Block Small-Step Semantics

## 2.3.10 Grids

Grid execution is similar to thread block execution in the sense that thread blocks are nondeterministically chosen for execution. There is no hardware based memory synchronization at this level, so Figure 2.4 includes only one derivation rule. The rule chooses an unfinished thread block to execute and updates the grid with the new thread block state.

We define a thread block to be complete when all warps are at an Exit instruction.

When a grid finishes executing, all thread blocks should be complete.

#### 2.4 Example Validation Results

To demonstrate how our framework facilitates machine-checked validation of GPU software, we walk through the validation of a toy PTX program that sums two vectors. Listing 2.1 is

complete

$$(\pi, \beta) \equiv (\forall \omega \in \beta : \pi(\omega_{pc}) = \text{Exit})$$

$$\frac{\exists \beta \in \gamma . \neg \text{complete}(\pi, \beta)}{\pi \vdash \langle \beta, \mu \rangle \rightarrow_1 \langle \beta', \mu' \rangle} (\text{exec}_g)$$

$$\frac{\pi \vdash \langle \gamma, \mu \rangle \rightarrow_1 \langle \gamma[\beta'/\beta], \mu' \rangle}{\pi \vdash \langle \gamma, \mu \rangle \rightarrow_1 \langle \gamma[\beta'/\beta], \mu' \rangle} (\text{exec}_g)$$

Figure 2.4: Grid Small-Step Semantics

the (almost) verbatim PTX code compiled from sources; our only modification is to rename the parameters in lines 10–13 to something more human-readable, for explanatory purposes.

## 2.4.1 Context Lifting

Listing 2.2 shows our translation of the PTX code to corresponding Coq definitions. At the beginning of all PTX functions is a declaration of the types and quantities of needed registers. We do not necessarily need to translate this to Coq, but for the sake of readability we do so in lines 1–4. Since PTX instructions take operands (not just registers) as input, we use a wrapper to turn all registers into operands (line 6), and prefix the variable with an underscore (e.g. \_r1) to make the distinction. Lines 9–12 load the function arguments into registers. Loads have semantics equivalent to Moves in our framework, so the Coq translation uses Mov instructions.

All threads execute the same code concurrently, but each receives a distinct thread index, which is computed in lines 14–17. Since each thread is tasked with adding elements from a specific index in the vector, at least size threads are spawned, where size is the length of the vector. It could be the case that more than size threads are spawned, so a bounds check is implemented in lines 19–20. As mentioned in §2.3.8, warps can diverge when multiple execution paths exist. In this example there are two paths with a divergence point at line 20. The matching Sync instruction is inserted at line 35 (index 18 in the Coq instruction list).

Listing 2.1: PTX Assembly for Vector Sum

Listing 2.2: Coq PTX Assembly

```

1 reg pred p<2>;

Definition r1 : reg := (UI 32, 1).

2 .reg .u32 %r<9>;

Definition r2 : reg := (UI 32, 2).

3 .reg .u64 %rd<11>;

Definition rd1 : reg := (UI 64, 1).

Definition r1 : op := Reg r1.

Definition add vector : prg := [

9 ld.param.u64 %rd1, [arr A];

Mov rd1 arr A;

10 ld.param.u64 %rd2, [arr B];

Mov rd2 arr B;

11 ld.param.u64 %rd3, [arr C];

Mov rd3 arr C;

12 ld.param.u32 %r2, [size];

Mov r2 size;

14 mov.u32 %r3, %ntid.x;

Mov r3 ntid x;

15 mov.u32 %r4, %ctaid.x;

Mov r4 ctaid x;

16 mov.u32 %r5, %tid.x;

Mov r5 tid x;

17 mad.lo.s32 %r1, %r4, %r3, %r5;

Top MADLO r1 r4 r3 r5;

19 setp.ge.s32 %p1, %r1, %r2;

Setp GE p1 r1 r2;

20 @%p1 bra BB0 2;

PBra p1 18;

21

22 cvta.to.global.u64 %rd4, %rd1;

23 mul.wide.s32 %rd5, %r1, 4;

Bop MULWD rd5 r1 (lmm 4);

24 add.s64 %rd6, %rd4, %rd5;

Bop ADD rd6 rd1 rd5;

25 cvta.to.global.u64 %rd7, %rd2;

26 add.s64 %rd8, %rd7, %rd5;

Bop ADD rd8 rd2 rd5;

27 ld.global.u32 %r6, [%rd8];

Ld Global r6 rd8;

28 ld.global.u32 %r7, [%rd6];

Ld Global r7 rd6;

30 add.s32 %r8, %r6, %r7;

Bop ADD r8 r6 r7;

31 cvta.to.global.u64 %rd9, %rd3;

32 add.s64 %rd10, %rd9, %rd5;

Bop ADD rd10 rd3 rd5;

33 st.global.u32 [%rd10], %r8;

St Global rd10 r8;

34

Sync;

36 BB0 2: ret;

Exit].

```

The translation of lines 22–33 omits the cvta.to instructions because they are implicit in our PTX formalization. Specifically, instruction cvta.to converts a generic address to a specified state-space, but our framework implicitly does this with the 1d and st instructions,

which both require a state-space parameter. The final PTX instruction is ret, which we translate to Exit for this example to end the validation at function completion.

### 2.4.2 Proof Procedure

In Coq we can formally prove and machine-check theorems about the program's behavior on arbitrary inputs, such as termination and correctness of output. Even though this is a simple example, Coq has a rich collection of supporting libraries and theory modules that can be applied to reason about much more complex mathematical properties of larger programs. For example, there is extensive prior work on leveraging Coq to prove properties of cryptographic algorithms (Barthe et al., 2011, 2013; Petcher and Morrisett, 2015). For expository simplicity, we here limit our presentation to proving total correctness of this very simple algorithm.

Listing 2.3: Proving Termination of Vector Sum

```

Definition warp_complete (pi : prg) (w : warp) : bool :=

match pi (get_pc w) with

Some Exit => true

| _ => false

end.

Definition block_complete (pi : prg) (b : block) : bool :=

forallb (warp_complete pi) b.

Definition terminated (pi : prg) (g : grid) : Prop :=

forallb (block_complete pi) g = true.

// *sample parameter configs *)

```

```

Definition kc : kconf := ((1,1,1),(32,1,1)).

Definition g : grid := generate grid kc.

16 Definition mu : mem\_f := ... \ (* initial memory state *)

17

18 Inductive grid t

_{19}:\mathit{prg} \rightarrow \mathit{kconf} \rightarrow \mathit{grid} \times \mathit{mem\_f} \rightarrow \mathit{grid} \times \mathit{mem\_f} \rightarrow \mathbf{Prop} :=

Theorem add vector terminates:

\forall (g': grid) (mu': mem\_f),

n_apply 19 (grid_t add_vector kc) (g,mu) (g',mu') \rightarrow

terminated add vector g'.

26 Proof.

intros g' mu' Happ.

repeat (unroll apply Happ).

28

compute. reflexivity.

30 Qed.

```

Listing 2.3 shows how termination is defined and proved for our toy program. A program's execution is considered terminated (or completed) when all threads have reached the Exit instruction. Definition terminated in the listing checks whether all blocks are complete, which entails confirming whether all warps are complete. We then give a few, but necessary, parameter configurations (kc, g, and mu) to initialize program execution. Finally we define our theorem add\_vector\_terminates by hypothesizing that after 19 small-steps of execution, the program terminates.

Proposition n\_apply is inductively defined in Listing 2.5, which relates the number n of applications of a proposition  $f:A\to A\to Prop$  to an input a:A with an output a':A. At its base case, the number of steps to take is zero, so this is essentially an identity proposition. The inductive case performs one application of f and recursively applies it n-1 more times.

Proving a theorem in Coq typically begins with introducing universally quantified variables (g' and mu') and hypotheses (Happ) into the proof context, as shown. Next, the repeat tactic repeatedly applies a given proof tactic until it fails. The given tactic in this case is unroll\_apply, which is defined in Listing 2.5.

Our unroll\_apply tactic can be thought of as a primitive symbolic execution engine for PTX. It directly applies the operational semantics of PTX to a proof hypothesis through inversion reasoning, which infers a derivation rule's prerequisites from its consequent. In the case of derivation rules that encode operational semantics, this infers the set of new program states that may result from each instruction's execution, thereby symbolically interpreting the instruction within the proof environment.

In detail, unroll\_apply considers the two possible cases of n\_apply: either n=0 (no more steps) or n>0. In both cases we start off with the same three tactics: (1) inversion, (2) subst, and (3) clear. The inversion tactic reasons by the distinctness of constructors and only considers cases that could have been used to form the hypothesis. When n=0, the only case that can be used is AppZero and proposes that the input a and output a' are equivalent. Otherwise, n is positive so AppNext is the only case that applies. Inversion can produce many variable aliases, so we use subst to automatically substitute away any redundant, fresh variable names from the proof context. Finally, we clear the inverted hypothesis from the context once all its effects have been computed and it is no longer needed. Tactic step\_grid applies a similar strategy for symbolic execution of grids; we here omit its definition for brevity.

Moving back to the theorem, our symbolic interpreter ultimately reveals the final states of g' and mu' and encodes them as hypotheses in the proof environment. The compute

tactic reduces terminated add\_vector g' to true = true and we finally apply reflexivity to complete the proof.

Listing 2.4: Proving Correctness of Vector Sum

```

<sup>1</sup> Fixpoint get_array (mu : mem_f) (a : addr) (len width : nat)

: list Z :=

match len with

| O = > []

| S len' => let v := read_mem mu a width in

v :: get array mu (incr addr a) len' width

7 end.

9 Definition add array (a b : list Z) : list Z :=

let add_pair := fun p => match p with (x,y) => x+y end in

map add pair (combine a b).

13 Definition arrA : addr := ...

14 Definition arrB : addr := ...

15 Definition arrC : addr := ...

16 Definition N : nat := numElements.

17

18 Theorem add_vector_correct :

\forall (g': grid) (mu': mem_f) (A B C : list Z),

n apply 19 (grid t add vector kc) (g,mu) (g',mu') \rightarrow

A = get array mu arrA N 32 \rightarrow

21

B = get array mu arr B N 32 \rightarrow

22

```

```

C = get_array mu' arrC N 32 →

add_array A B = C.

Proof.

intros g' mu' A B C Happ HA HB HC.

repeat unroll_apply Happ.

subst. compute. reflexivity.

Qed.

```

Listing 2.4 proves partial correctness—i.e., that the result of the computation is the sum of the two input vectors, if it terminates. Coupled with Listing 2.3, this establishes total correctness of the computation. Vectors A and B come from the initial memory state mu and vector C is from the final memory state mu'. The theorem therefore posits that A + B = C.

The proof begins similarly to Listing 2.3, introducing the variables and hypotheses. Then we can apply our unroll\_apply tactic to obtain the final memory state mu'. After some computation, the symbolic interpreter arrives at the desired symbolic expression for C, proving the correctness property.

Listing 2.5: Proof Automation Tactics for Symbolic Execution of PTX Code

```

Inductive n_apply {A:Type}

\begin{array}{l}

1 \text{ Inductive n_apply } {A:Type} \\

2 : nat \rightarrow (A \rightarrow A \rightarrow \mathbf{Prop}) \rightarrow A \rightarrow A \rightarrow \mathbf{Prop} := \\

3 | AppZero (f : A \rightarrow A \rightarrow \mathbf{Prop}) (a : A) : \\

4 | n_apply 0 f a a \\

5 | AppNext (n : nat) (a a1 a' : A) (f : A \rightarrow A \rightarrow \mathbf{Prop}) \\

6 | (Hf : f a a1) \\

7 | (Happ : n_apply n f a1 a') : \\

8 | n_apply (S n) f a a'.

\end{array}

```

```

10 Ltac step grid H := ...

11

12 Ltac unroll_apply H :=

match type of H with

| n_apply ?n _ _ _ =>

match n with

| O => inversion H; subst; clear H

| _{-} = > let Hgrid := fresh "Hgrid" in

17

let Happ := fresh "Happ" in

18

inversion H as [ | ? ? ? ? ? Hgrid Happ]; subst; clear H;

19

step grid Hgrid

20

end

21

_ => fail

23 end.

```

Both of these proofs demonstrate the power of our automation tactics to reliably facilitate formal reasoning about PTX operation. By expressing the symbolic interpreter as proof tactics, we afford users the ability to quickly and easily reduce computations to symbolic expressions within a Coq proof, and subsequently apply the full power of Coq's mathematical theories to reason about the resulting symbolic expressions. This power comes without any additions to the TCB of the framework, since the tactics merely automate the application of the operational semantics rules; they do not introduce new rules that must be checked for accuracy.

### 2.4.3 Non-deterministic Execution

One of the most difficult aspects of parallel and concurrent programs to reason about is the inter-thread order in which instructions are executed. Explicitly considering all possible executions within proofs is infeasible and unmanageable even for small programs. To ease this burden, we have successfully proved a general theorem showing that the result of a PTX computation is always independent of the order in which the threads of a warp execute. It therefore suffices to only consider a sequential thread execution order within proofs. We here outline this theorem and its proof.

Listing 2.6: Non-deterministic Map

```

1 Inductive nth ri {A:Type}

_2: nat \rightarrow list A \rightarrow A \rightarrow list A \rightarrow \mathbf{Prop} :=

3 RI Oat:

nth ri 0 (a::t) a t

RI_S n t t' x a

(Hn: nth rintat'):

nth ri (S n) (x::t) a (x::t').

9 Inductive nd map {A B : Type}

(A \rightarrow B) \rightarrow list A \rightarrow list B \rightarrow \mathbf{Prop} :=

| NDNil (f : A \rightarrow B) :

nd_map f [] []

12

NDCons (f : A \rightarrow B) (l l1 : list A) (l2 l' : list B) (a : A) (n : nat)

13

(Hl: nth rinlal1)

14

(Hmap: nd_map f l1 l2)

15

(Hl': nth_ri n l' (f a) l2) :

16

```

```

17 nd map f l l'.

```

Listing 2.6 first defines proposition nth\_ri, which removes an element a at position n from a given given list 1, and returns a new list 1'. We use this definition to create a non-deterministic map function nd\_map. It is non-deterministic in the sense that the elements are processed in an arbitrary order and not from front to back. This captures all possible thread schedules for warps, which execute threads in lock-step but in an unspecified order. Some components on the SM, such as SFUs, are physically limited in quantity, making it impossible for all threads in a warp to execute on the same clock cycle. Therefore, we seek to prove that a non-deterministic execution is equivalent to a deterministic one.

Listing 2.7: Non-deterministic/Deterministic Equiv

```

<sup>1</sup> Theorem nd_map_eq:

\forall (A B : \mathbf{Type}) (f : A \rightarrow B) (l : list A) (l' : list B),

nd_map f l l' \longleftrightarrow l' = map f l.

4 Proof.

intros A B f l l'.

split; intros H.

(* nd\_map \rightarrow map *)

induction H.

(* Case: NDNil *)

10

reflexivity.

11

(* Case: NDCons *)

12

inversion Hl'; subst; inversion Hl; subst; clear Hl Hl'.

13

(* SCase: n = 0 *)

14

reflexivity.

15

```

```

(* SCase: n is in the middle somewhere *)

16

inversion H3; subst; clear H3 H.

17

simpl. apply list hd eq.

18

generalize dependent t.

19

induction Hn0; intros.

inversion Hn; subst; clear Hn.

21

reflexivity.

inversion Hn; subst; clear Hn.

simpl. apply list hd eq. eapply IHHn0. exact Hn1.

24

(*\ map\ \rightarrow\ nd\_\ map\ *)

26

generalize dependent l'.

27

induction l; intros; subst; simpl.

28

(* Case \ l = [] *)

29

apply NDNil.

30

(* Case \ l = hd :: tl *)

31

eapply NDCons; try apply RI O.

32

apply IHl. reflexivity.

33

34 Qed.

```

Listing 2.7 summarizes our equivalence proof. We start by inducting on the definition of nd\_map, which generates two cases: the base case NDNil and inductive case NDCons. The base case is straightforward, so we here focus on the inductive case. It divides into two sub-cases: an element is chosen from the head, or from within the tail. The bulk of the proof focuses on the second sub-case. It leverages dependent inductive reasoning (Cornes and Terrasse, 1995; McBride, 2002) to universally consider all possible thread orderings.

In future work, we plan to extend this result to the warp scheduling algorithm as well, to also eliminate that source of non-determinism from proofs. This result is more challenging because it requires reasoning about the order of memory operations. One reason nd\_map is equivalent to map is because computation does not affect an output at another index. Moving up in the thread hierarchy to thread blocks, one must additionally consider the order of memory operations, which could potentially affect the output of another thread.

## 2.5 Summary

Our work shows promise in providing a feasible means to machine-verify GPU programs using a well-established, mature proof assistant—the Coq system. Coq's strong, dependent typing system facilitates a natural encoding of GPU assembly code operational semantics as inductive axioms, including modeling its traditionally challenging parallelism and thread scheduling properties. To streamline proofs, Coq's tactic language was leveraged to build a symbolic interpreter that automatically derives provably correct symbolic expressions for assembly code fragments within the proof environment.

Using the resulting framework, we constructed the first machine-checked proof of CUDA thread scheduling transparency, as well as validating correctness properties of some simple programs.

As with any formal validation, our approach does not replace code testing, but can provide stronger guarantees and assurances that do not rely upon comprehensiveness of test sets. By targeting assembly code programs, our framework is applicable to GPU code produced from arbitrary source languages and compilation toolchains. In future work we plan to further ease the task of proof-writing by formulating more extensive theorem libraries and tactic libraries that modularize and automate GPU code correctness proofs.

### CHAPTER 3

### J-GANG $^1$

#### 3.1 Overview

This chapter presents the design, implementation, and evaluation of a framework for translating Java source code to a CPU-GPU hybrid architecture suitable for secure, n-variant computation. Translation entails semantic preservation of the source Java code to each target architecture (CPU and GPU), and verification entails detection of semantic divergence between these two target computations.

The open library for analysis of the Java language, Java Spoon by Inria (Pawlak et al., 2015) and Javassist, is adopted to exact all the data and logic information from original code (or bytecode) both statically and dynamically. Additionally, it is also applied to record local variables for state logging operations. These are re-composed into new code satisfying the grammar rules of the GPU kernel language. After the translation, our system executes the code and the replica in parallel by using Java Aaprapi and OpenCL. Throughout this parallel execution, two series of memory states are logged and compared to detect divergences. To evaluate the prototype implementation, experiments on third-party Java programs demonstrate performance and security effectiveness of the approach.

The contributions of J-GANG can be summarized as follows:

- We introduce the first *n*-variant system for Java computation verification based on architectural differences between GPU and CPU.

- To harmonize the dissimilar performance advantages of the two architectures, we introduce an asynchronous trust-but-verify n-variant model, in which single- or few-

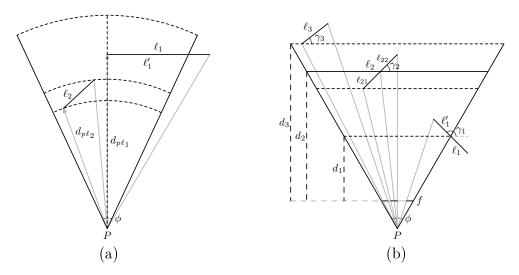

<sup>&</sup>lt;sup>1</sup>The material in this chapter was originally published as: Jun Duan, Kevin W. Hamlen, and Benjamin Ferrell, "Better Late Than Never: An N-variant Framework of Verification for Java Source Code on CPU×GPU Hybrid Platform," In Proceedings of the 28th International Symposium on High-Performance Parallel and Distributed Computing (HPDC), pp. 207–208, June 2019.