# HIGH MOBILITY III-V SEMICONDUCTOR DEVICES WITH GATE DIELECTRICS AND PASSIVATION LAYERS GROWN BY ATOMIC LAYER DEPOSITION

by

Xin Meng

## APPROVED BY SUPERVISORY COMMITTEE:

| Jiyoung Kim, Chair |      |  |

|--------------------|------|--|

|                    |      |  |

|                    | <br> |  |

| Chadwin D. Young   |      |  |

|                    |      |  |

|                    |      |  |

| Jeong-Bong Lee     |      |  |

|                    |      |  |

|                    |      |  |

| Walter Hu          |      |  |

Copyright 2018

Xin Meng

All Rights Reserved

# HIGH MOBILITY III-V SEMICONDUCTOR DEVICES WITH GATE DIELECTRICS AND PASSIVATION LAYERS GROWN BY ATOMIC LAYER DEPOSITION

by

XIN MENG, BS, MS

## **DISSERTATION**

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT DALLAS

May 2018

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my special appreciation and gratitude to my advisor Professor Jiyoung Kim for giving me great support and guidance through my research and study at UTD. He is a tremendous mentor who always gives me brilliant ideas, invaluable advice, and encouraging words when I am struggling with experiments. His perseverance and optimistic attitude have deeply affected me and will continue to encourage me through my life. I also deeply appreciate him for providing me the precious opportunity to attend academic conferences, where I gained valuable experience and came up with new ideas for my research and future career. Without his support, I would not have had the chance to receive graduate fellowships and best ALD 2017 student paper finalist award.

I would like to thank Professor Chadwin D. Young, Professor Jeong-Bong Lee, and Professor Walter Hu for serving on my committee, as well as spending their valuable time for my doctoral proposal and defense examination. I sincerely appreciate Professor Chadwin D. Young and Professor Robert M. Wallace for allowing me to use the instruments in their labs to conduct my experiments.

I also want to acknowledge Dr. Antonio T. Lucero, who serves as an "assistant advisor" in my lab, for sharing with me the mechanism of parts, tools, equipment, and process, as well as teaching me a lot of interesting things (e.g., beers, foods, and quantum physics for babies) and practical experience (e.g., change engine oil and repair things), which I would have never known as a foreigner. I really appreciate Dr. Lanxia Cheng for sharing her valuable research experience and providing great help to me during the submission of my first paper at UTD. I am greatly indebted to Dr. Young-Chul Byun and Dr. Jae-Gil Lee for carefully guiding me on how to fabricate and

measure GaN and InGaAs devices at the beginning of my research. Without their selfless help, I would not be able to have a steady research progress. Many thanks to my other group members, both past and present, including Dr. Si Joon Kim, Dr. Heber Hernandez-Arriaga, Joy Lee, Jaebeom Lee, Arul Ravichandran, Harrison Kim, Su Min Hwang, Jaidah Mohan, Dushyant Narayan, Aswin Kondusamy, who are always supportive and make my life at UTD memorable. I also thank my UTD friends, including Xiaoye Qin, Hui Zhu, Kui Tan, Fantai Kong, Ruoyu Yue, Chunlei Zhang, Shi Liang, Yichi Jia, Liang Xu, Jian Wang, Bo Zhang, and Chenxi Zhang, for being important witnesses of my journey toward earning a doctoral degree.

I express my sincere gratitude to the entire NSERL cleanroom staff (Wallace Martin, Vickie Lincoln, Dr. Gordon Pollack, Dr. Roger Robbins, Scott Riekena, John Goodnight, Zane Borg, Bruce Albert, and late Mr. John Maynard) and the technical staff (Tommy Bennett and Dave Stimson), who work diligently to maintain the research facilities very well and provide us the technical training for our research.

Lastly, I could not be more grateful to my family for their endless love and support. They are always the most beloved and trustable people in my life. I want to give special thanks to my wife, Chunjin An, who is considerate and supportive all the time. I cannot describe my deepest love and appreciation to her in words.

March 2018

HIGH MOBILITY III-V SEMICONDUCTOR DEVICES WITH GATE DIELECTRICS

AND PASSIVATION LAYERS GROWN BY ATOMIC LAYER DEPOSITION

Xin Meng, PhD

The University of Texas at Dallas, 2018

Supervising Professor: Jiyoung Kim

This dissertation focuses on the applications of atomic layer deposition (ALD) to high mobility

III-V semiconductor devices. The first study is an in situ ALD-based interface passivation

technique using ALD diethylzinc (DEZ) treatment on n-type and p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As substrate.

The capacitance-voltage (C-V) characteristics of metal-oxide-semiconductor capacitors

(MOSCAPs) were studied for a variety of ALD DEZ treatment cycles, different measurement

temperatures, and different thickness of ALD-grown high-k gate insulators. The reasons for the

presence of inversion-like C-V characteristics shown on n-type substrates are discussed. In

addition to ALD DEZ passivation, two alternative ALD-based interface passivation techniques

were studied. Furthermore, inversion-type enhancement-mode n-channel and p-channel

In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor field-effect transistors (MOSFETs) were demonstrated

using in situ ALD DEZ-based interface passivation techniques.

The second part of this dissertation is the fabrication and characterization of AlGaN/GaN MIS-

HEMTs. Silicon nitride (SiN<sub>x</sub>), grown by low-temperature hollow cathode plasma-enhanced ALD

(PEALD), served as a gate dielectric and a surface passivation layer for MIS-HEMTs. Extensive

vii

characterization of the devices was done by high-resolution transmission electron microscopy (HRTEM), current-voltage (I-V) measurement, C-V measurement, gate bias stress measurement, and pulsed I-V measurement. The SiN<sub>x</sub>/GaN MIS-HEMTs not only showed a crystalline interfacial layer in the HRTEM images of gate stack, but also demonstrated excellent threshold voltage stability and a mitigated current collapse. Clearly, the effective passivation of surface/interface defects (e.g., nitrogen vacancies and dangling bonds) by the crystalline interfacial layer and the low bulk trap density of PEALD SiN<sub>x</sub> are highly beneficial to the reliability of GaN devices. The last part of this dissertation mainly focuses on the electrical characteristics of AlGaN/GaN heterostructure with ALD-grown epitaxial ZnO cap layer. Theoretically, it was predicted that the piezoelectric polarization of epitaxial ZnO cap layer should have a direction opposite to that in the underlying AlGaN/GaN substrate. As a result, resembling the effect of an InGaN cap layer, a ZnO cap layer may deplete the two-dimensional electron gas (2DEG) near the AlGaN/GaN interface. Experimentally, HRTEM confirmed the epitaxial growth of single-crystalline ZnO cap layer on AlGaN/GaN heterostructure by thermal ALD at 300 °C. The  $I_{ds}$ -V  $_g$  transfer curve and C-V curve showed a significant positive shift (~1 V) for devices with an O<sub>3</sub>-based epitaxial ZnO cap layer, compared to those of Schottky gate devices and devices with a highly conductive H<sub>2</sub>O-based epitaxial ZnO cap layer.

## TABLE OF CONTENTS

| ACKNOWLE    | DGME   | ENTS                                              | v   |

|-------------|--------|---------------------------------------------------|-----|

| ABSTRACT.   |        |                                                   | vi  |

| LIST OF FIG | URES.  |                                                   | xii |

| LIST OF TAI | BLES   |                                                   | xix |

| CHAPTER 1   | INTR   | ODUCTION AND BACKGROUND                           | 1   |

| 1.1         | Introd | luction                                           | 1   |

| 1.2         | High 1 | Mobility III-V Compound Semiconductor Devices     | 2   |

|             | 1.2.1  | Overview of InGaAs MOS Devices and Present Issues | 2   |

|             | 1.2.2  | Overview of AlGaN/GaN HEMTs and Present Issues    | 5   |

| 1.3         | Atom   | ic Layer Deposition                               | 20  |

|             | 1.3.1  | ALD of Silicon Nitride (SiN <sub>x</sub> )        | 22  |

| 1.4         | Disser | rtation Outline                                   | 23  |

| CHAPTER 2   | EXPE   | ERIMENTAL                                         | 25  |

| 2.1         | Introd | luction                                           | 25  |

| 2.2         | ALD :  | Reactors                                          | 25  |

|             | 2.2.1  | Cambridge Nanotech Thermal ALD                    | 25  |

|             | 2.2.2  | Hollow Cathode Plasma-Enhanced ALD                | 26  |

| 2.3         | Mater  | rial Characterization Facility                    | 28  |

|             | 2.3.1  | Spectroscopic Ellipsometer                        | 28  |

|             | 2.3.2  | X-ray Photoelectron Spectroscopy                  | 28  |

|             | 2.3.3  | Atomic Force Microscopy                           | 29  |

|             | 2.3.4  | Profilometer                                      | 30  |

|             | 2.3.5  | High-Resolution Transmission Electron Microscopy  | 31  |

| 2.4         | Electr | rical Characterization Facility                   | 31  |

|             | 2.4.1  | Cascade Probe Station                             | 31  |

|             | 2.4.2  | Cryogenic Probe Station                           | 32  |

|             | 2.4.3  | Hall Effect Measurement                           | 33  |

| 2 | 2.5         | Device  | Fabrication and Mask Layout                                                                                                                                          | 33 |

|---|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | 2.6         | Device  | Characterization Methods                                                                                                                                             | 36 |

|   |             | 2.6.1   | Transmission Line Measurement                                                                                                                                        | 36 |

|   |             | 2.6.2   | Positive/Negative Bias Instability (PBI or NBI) Stress Measurement                                                                                                   | 37 |

|   |             | 2.6.3   | Pulsed I-V Measurement                                                                                                                                               | 39 |

|   |             |         | GA <sub>0.47</sub> AS MOS DEVICES USING ALD-BASED INTERFACIAL<br>ER AND HIGH-K GATE DIELECTRIC STACKS                                                                | 41 |

| 3 | 3.1         | Introdu | action                                                                                                                                                               | 41 |

| _ |             |         | H/(NH <sub>4</sub> ) <sub>2</sub> S Treated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAPs using ALD-Grown High-k c Stacks without ALD-Based Interface Passivation |    |

|   |             | 3.2.1   | Experimental                                                                                                                                                         | 42 |

|   |             | 3.2.2   | Results and Discussions                                                                                                                                              | 45 |

| 3 | 3.3         | In situ | ALD DEZ-Based Interface Passivation on In <sub>0.53</sub> Ga <sub>0.47</sub> As                                                                                      | 49 |

|   |             | 3.3.1   | Introduction                                                                                                                                                         | 49 |

|   |             | 3.3.2   | Experimental, Results, and Discussion                                                                                                                                | 51 |

| 3 | 3.4         | Alterna | ative ALD-based Interface Passivation on In <sub>0.53</sub> Ga <sub>0.47</sub> As                                                                                    | 63 |

| _ |             |         | on-Type Enhancement-Mode n-channel and p-channel In <sub>0.53</sub> Ga <sub>0.47</sub> As ng in situ ALD DEZ-Based Interface Passivation Techniques                  | 70 |

|   |             | 3.5.1   | Introduction                                                                                                                                                         | 70 |

|   |             | 3.5.2   | Experimental                                                                                                                                                         | 72 |

|   |             | 3.5.3   | Results and Discussion                                                                                                                                               | 75 |

| 3 | 3.6         | Summa   | ary                                                                                                                                                                  | 82 |

|   |             |         | GAN MIS-HEMTS WITH CRYSTALLINE INTERFACIAL LAYER ATHODE PEALD                                                                                                        | 84 |

| 4 | <b>l</b> .1 | Abstra  | ct                                                                                                                                                                   | 84 |

| 4 | 1.2         | Introdu | action                                                                                                                                                               | 85 |

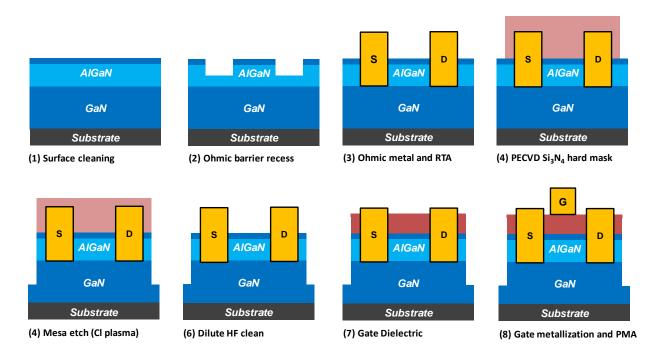

| 4 | 1.3         | Experi  | mental                                                                                                                                                               | 86 |

| 4 | 1.4         | Results | s and Discussion                                                                                                                                                     | 92 |

|   |             | 4.4.1   | Contact Resistance and Buffer Leakage                                                                                                                                | 92 |

|   |             | 4.4.2   | Characterization of Hollow Cathode PEALD SiN <sub>x</sub> Film                                                                                                       |    |

|   |             | 112     | Davica Characterization                                                                                                                                              | 05 |

| 4.5        | Summary                                                                                           | 101 |

|------------|---------------------------------------------------------------------------------------------------|-----|

|            | EFFECT OF ALD-GROWN EPITAXIAL ZNO CAP LAYER ON THE L CHARACTERISTICS OF ALGAN/GAN HETEROSTRUCTURE | 103 |

| 5.1        | Introduction                                                                                      |     |

| 5.2        | Experimental                                                                                      | 103 |

| 5.3        | Results and Discussion                                                                            | 106 |

| 5.4        | Summary                                                                                           | 113 |

| CHAPTER 6  | CONCLUSIONS AND FUTURE WORK                                                                       | 114 |

| 6.1        | Conclusions                                                                                       | 114 |

| 6.2        | Future Work                                                                                       | 116 |

| APPENDIX A | A GATE-LAST INGAAS MOSFET GENERAL PROCESS FLOW                                                    | 120 |

| APPENDIX I | B GAN HEMT GENERAL PROCESS FLOW                                                                   | 127 |

| REFERENCI  | ES                                                                                                | 133 |

| BIOGRAPHI  | CAL SKETCH                                                                                        | 146 |

| CURRICULI  | IM VITAE                                                                                          |     |

## LIST OF FIGURES

| Figure 1.1  | Schematic diagram of the crystal structure of wurtzite GaN with Ga-face and N-face polarity [24]. Reprinted from Ambacher et al., Journal of Applied Physics 85, 3222 (1999), with the permission of AIP Publishing                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2  | Schematic diagram of the spontaneous polarization and piezoelectric polarization existing in an $Al_xGa_{1-x}N/GaN$ heterostructure, Ga-face polarity is assumed [25]. Adapted from ESSDERC 2013 tutorial, "High Voltage GaN HEMT devices and modelling" by Dr. Stephen Sque.                                                                                                                                 |

| Figure 1.3  | Schematic diagram of the spontaneous polarization and piezoelectric polarization existing in an $Al_xGa_{1-x}N/GaN$ heterostructure and the corresponding energy band diagram [25]. Adapted from ESSDERC 2013 tutorial, "High Voltage GaN HEMT devices and modelling" by Dr. Stephen Sque. 9                                                                                                                  |

| Figure 1.4  | Schematic band diagram of a GaN MIS-HEMT structure using a gate insulator to reduce the gate leakage current                                                                                                                                                                                                                                                                                                  |

| Figure 1.5  | Schematic diagram of a GaN MIS-HEMT structure with the presence of traps near the dielectric/III-N interface on either (I) gate region or (II) access region11                                                                                                                                                                                                                                                |

| Figure 1.6  | Representative C-V curve of a GaN MIS-capacitor measured at 100 kHz with Ni/Au gate electrode                                                                                                                                                                                                                                                                                                                 |

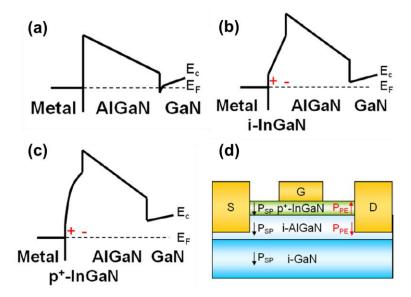

| Figure 1.7  | Schematic of the energy band-diagram in a Schottky gate AlGaN/GaN structure (a) without cap layer, (b) with an i-InGaN cap layer, (c) with a p-InGaN cap layer, and (d) schematic of a Schottky gate HEMT structure with a p-InGaN cap layer and the polarization direction inside [67]. Reprinted from Mizutani et al., Journal of Applied Physics 113, 034502 (2013), with the permission of AIP Publishing |

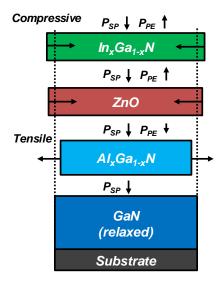

| Figure 1.8  | Schematic of spontaneous polarization $(P_{SP})$ and piezoelectric polarization $(P_{PE})$ present in epitaxial $Al_xGa_{1-x}N$ , $ZnO$ , and $In_xGa_{1-x}N$ on $GaN$                                                                                                                                                                                                                                        |

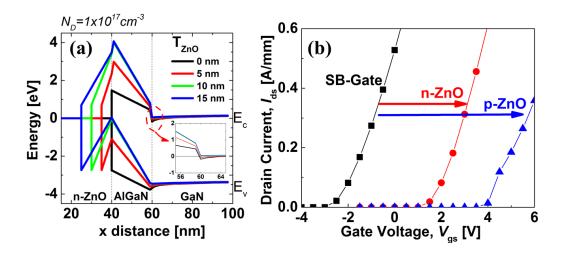

| Figure 1.9  | (a) Schematic of $Al_{0.25}Ga_{0.75}N/GaN$ band diagram without (0 nm) and with (5 nm, 10 nm, and 15 nm) n-type ZnO cap layer, (b) $V_{gs}$ - $I_{ds}$ transfer curves of HEMTs without (Schottky gate) and with 15 nm n-type or p-type ZnO cap layer. The results were simulated by Dr. Jae-Gil Lee using Silvaco Atlas                                                                                      |

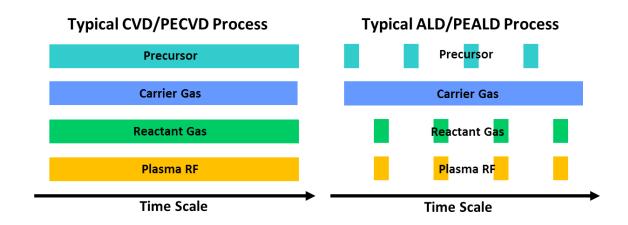

| Figure 1.10 | Schematic of the typical CVD/PECVD process and typical ALD/PEALD process20                                                                                                                                                                                                                                                                                                                                    |

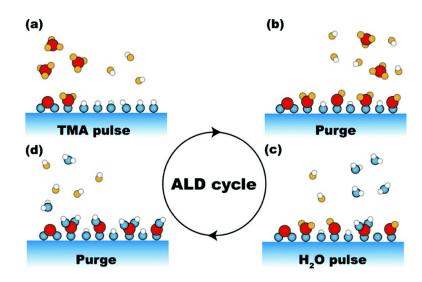

| Figure 1.11 | Schematic diagram of typical surface reactions of one cycle Al <sub>2</sub> O <sub>3</sub> ALD process using TMA and H <sub>2</sub> O [78]. Reproduced from H. Van Bui et al., Chem. Commun., 2017, 53, 45 with permission of The Royal Society of Chemistry             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

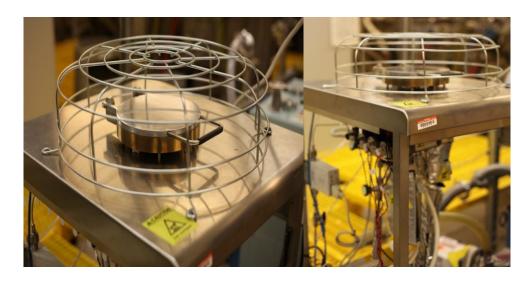

| Figure 2.1  | Cambridge Nanotech/Ultratech Savannah S100 (CNT) ALD reactor                                                                                                                                                                                                             |

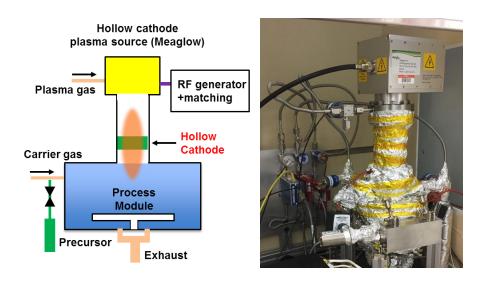

| Figure 2.2  | Schematic diagram and image of hollow cathode plasma-enhanced ALD reactor26                                                                                                                                                                                              |

| Figure 2.3  | A hollow cathode plasma source, a view of plasma inside the reactor, and the unique features compared to other plasma sources (adapted from www.meaglow.com). CCP is capacitive coupled plasma (CCP), ICP is inductively coupled plasma, MP is microwave plasma.         |

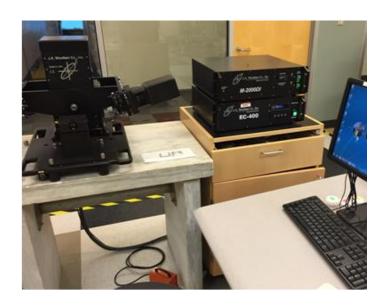

| Figure 2.4  | J. A. Woolam M-2000DI spectroscopic ellipsometer                                                                                                                                                                                                                         |

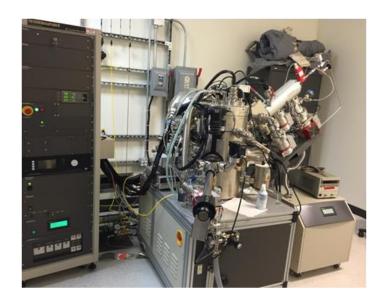

| Figure 2.5  | PHI VersaProbe II XPS system. 29                                                                                                                                                                                                                                         |

| Figure 2.6  | Veeco 5000 AFM located in UTD NSERL cleanroom                                                                                                                                                                                                                            |

| Figure 2.7  | Veeco Dektak VIII profilometer located in UTD NSERL cleanroom                                                                                                                                                                                                            |

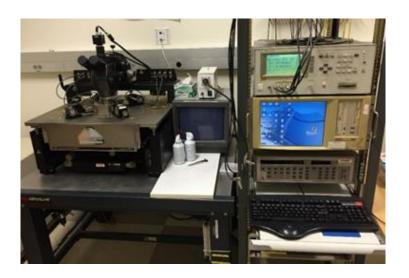

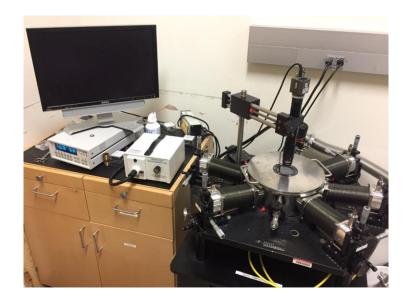

| Figure 2.8  | The Cascade probe station, HP 4284 LCR meter and Keithley 4200 semiconductor parameter analyzer                                                                                                                                                                          |

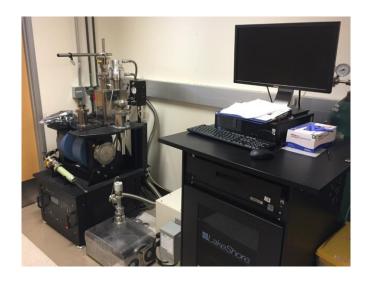

| Figure 2.9  | Cryogenic probe station, model TTPX, Lake Shore Cryotronics, Inc32                                                                                                                                                                                                       |

| Figure 2.10 | Lake Shore 8400 series Hall measurement system                                                                                                                                                                                                                           |

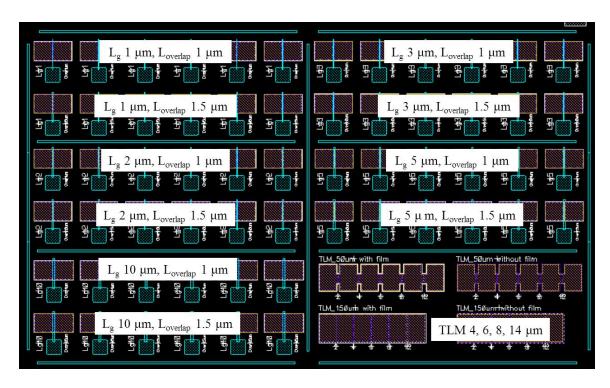

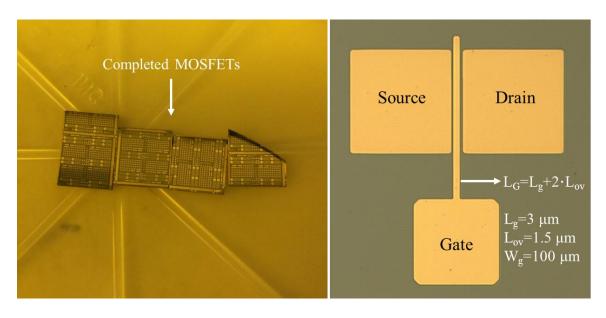

| Figure 2.11 | Mask layout designed by Dr. Jae-Gil Lee for InGaAs MOSFETs fabrication34                                                                                                                                                                                                 |

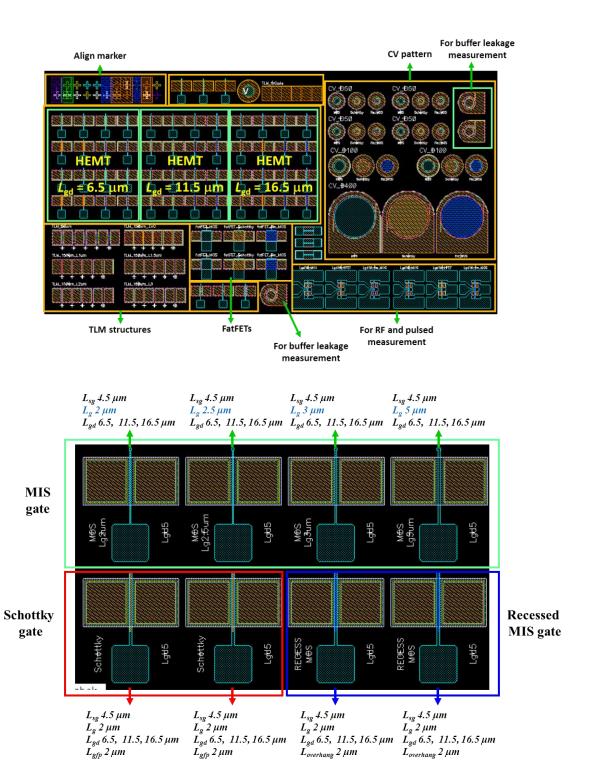

| Figure 2.12 | Mask layout designed by Dr. Jae-Gil Lee for GaN HEMTs fabrication35                                                                                                                                                                                                      |

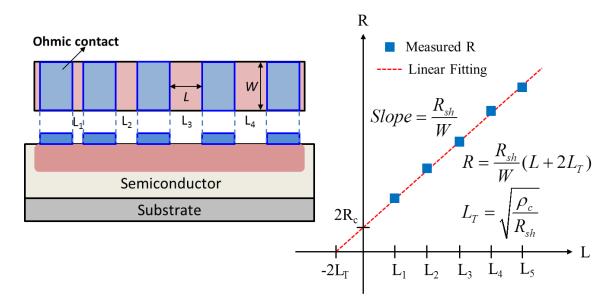

| Figure 2.13 | Schematic of contact resistance ( $R_c$ ), sheet resistance ( $R_{sh}$ ), and specific contact resistivity ( $\rho_c$ ) calculation using TLM                                                                                                                            |

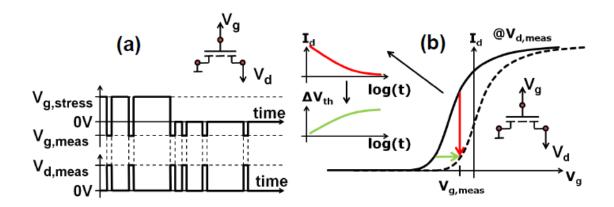

| Figure 2.14 | An example of the method for characterizing the V <sub>th</sub> instability of GaN MIS-HEMTs described by P. Lagger et al. [80]. Adapted from P. Lagger, et al., IEEE International Electron Devices Meeting (IEDM 12), pp. 13-1, with permission. Copyright 2012, IEEE. |

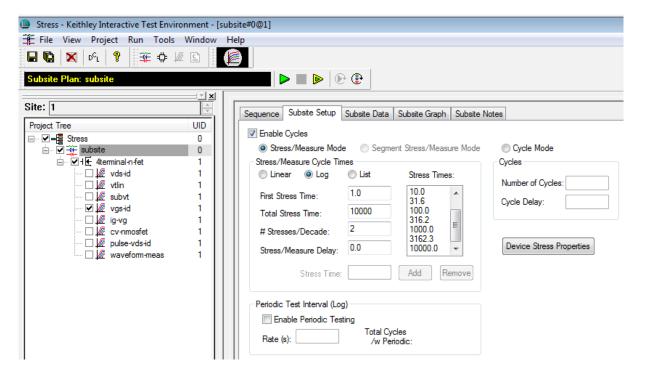

| Figure 2.15 | Snapshot of the stress measurement program of Keithley 4200-SCS                                                                                                                                                                                                          |

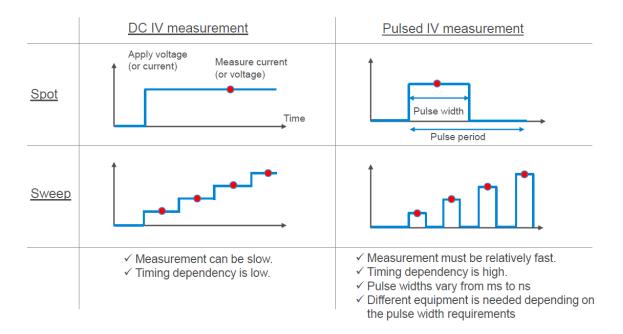

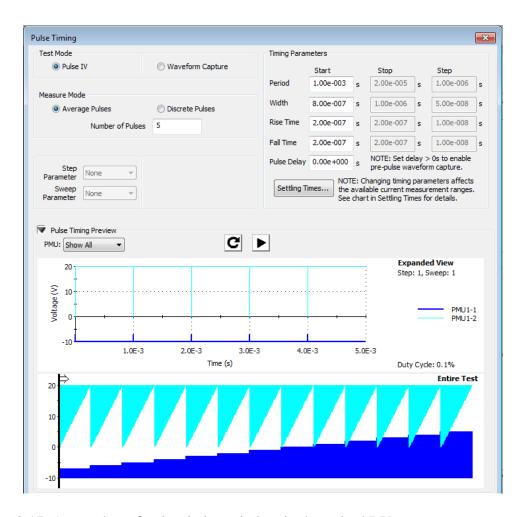

| Figure 2.16 | 6 Comparison between DC I-V measurement and Pulsed I-V measurement. Source:<br>"Fundamentals of fast pulsed IV measurement" by Alan Wadsworth, Agilent Technologies [81]                                                                                                                                                          |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.17 | A snapshot of pulse timing window in the pulsed I-V measurement program of Keithley 4200-SCS                                                                                                                                                                                                                                      |

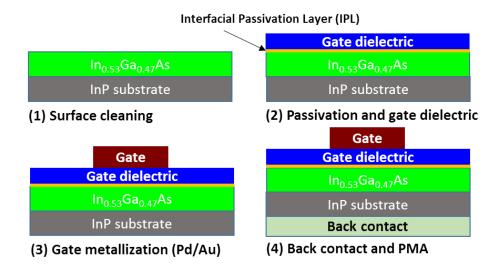

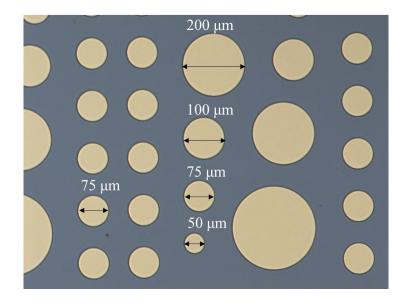

| Figure 3.1  | Schematic of the In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP fabrication process flow                                                                                                                                                                                                                                         |

| Figure 3.2  | Optical microscope image of the In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAPs                                                                                                                                                                                                                                                  |

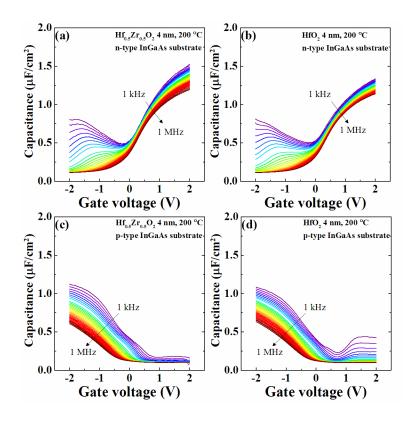

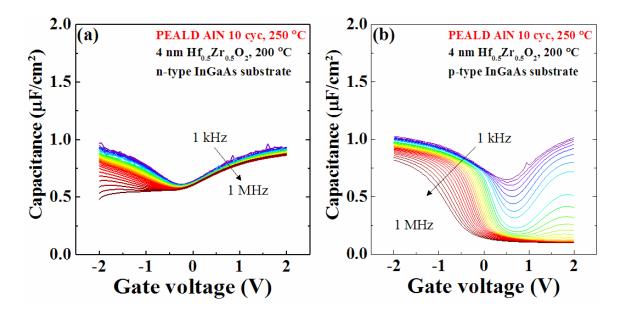

| Figure 3.3  | C-V frequency dispersion characteristics for $NH_4OH/(NH_4)_2S$ treated $In_{0.53}Ga_{0.47}As$ MOSCAPs with (a, c) 4 nm $Hf_{0.5}Zr_{0.5}O_2$ and (b, d) 4 nm $HfO_2$ ALD-grown gate insulator                                                                                                                                    |

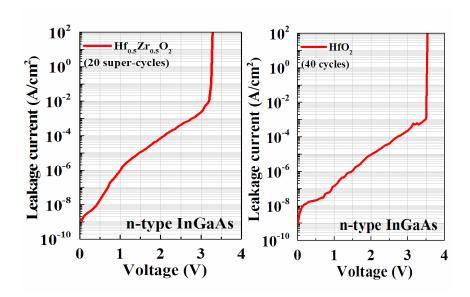

| Figure 3.4  | Breakdown characteristics for $NH_4OH/(NH_4)_2S$ treated MOSCAPs on n-type $In_{0.53}Ga_{0.47}As$ substrate with 4 nm $Hf_{0.5}Zr_{0.5}O_2$ and 4 nm $HfO_2$ gate insulator47                                                                                                                                                     |

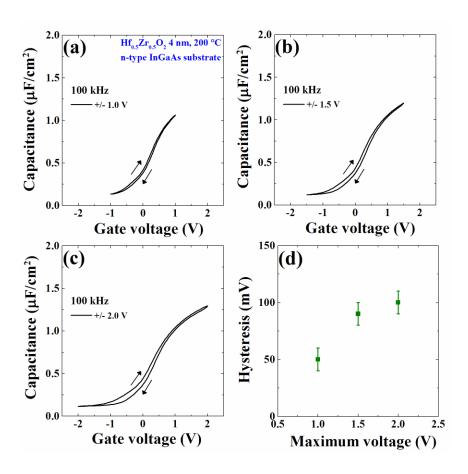

| Figure 3.5  | C-V hysteresis characteristics of $NH_4OH/(NH_4)_2S$ treated MOSCAPs on n-type $In_{0.53}Ga_{0.47}As$ substrate with 4 nm $Hf_{0.5}Zr_{0.5}O_2$ gate insulator as a function of maximum measurement voltage (a) 1.0 V, (b) 1.5 V, (c) 2.0 V, and (d) the corresponding hysteresis.                                                |

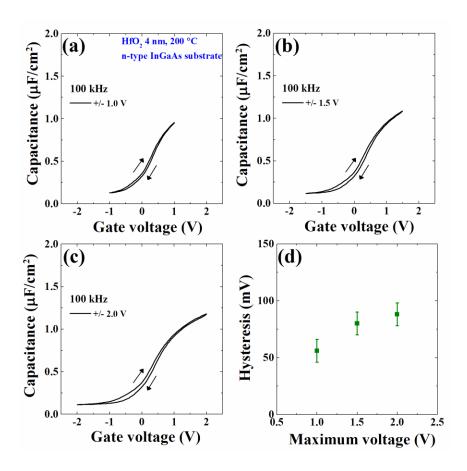

| Figure 3.6  | C-V hysteresis characteristics of NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated MOSCAPs on n-type In <sub>0.53</sub> Ga <sub>0.47</sub> As substrate with 4 nm HfO <sub>2</sub> gate insulator as a function of maximum measurement voltage (a) 1.0 V, (b) 1.5 V, (c) 2.0 V, and (d) the corresponding hysteresis. |

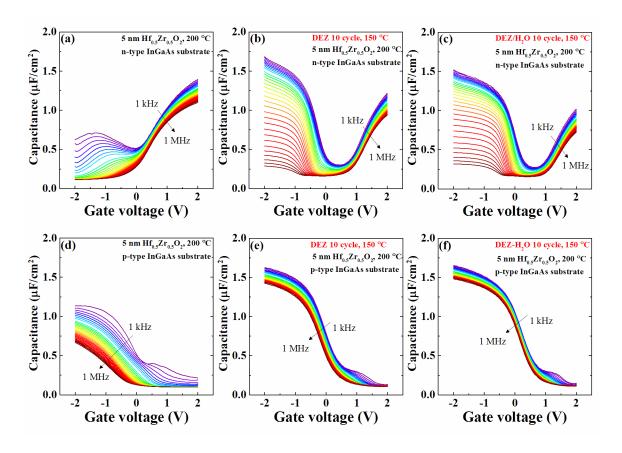

| Figure 3.7  | C-V frequency dispersion (from 1 kHz to 1 MHz) characteristics for NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples (a, d) without and with interface passivation by (b, e) in situ ALD DEZ and (c, f) ALD DEZ/H <sub>2</sub> O surface treatment             |

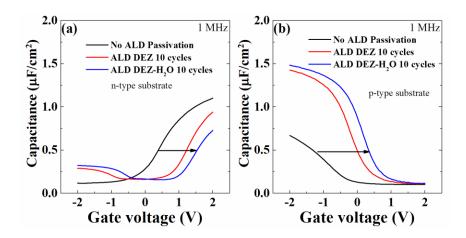

| Figure 3.8  | Comparison of C-V curves at 1 MHz for $NH_4OH/(NH_4)_2S$ treated $In_{0.53}Ga_{0.47}As$ MOSCAP samples on (a) n-type substrate (b) p-type substrate, without and with interface passivation by in situ ALD DEZ and ALD DEZ/ $H_2O$ surface treatment53                                                                            |

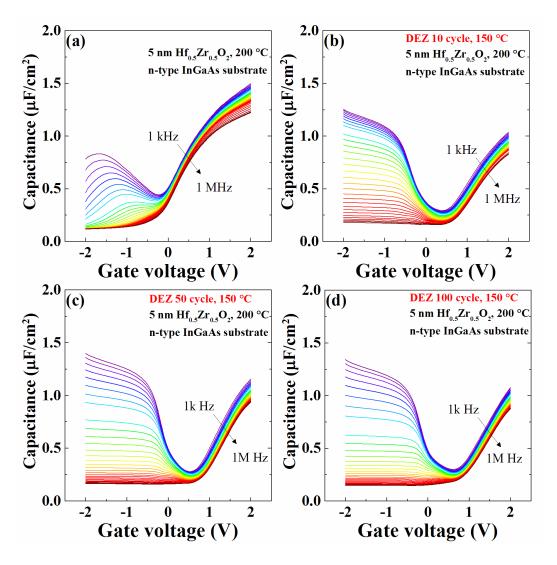

| Figure 3.9  | C-V frequency dispersion (from 1 kHz to 1 MHz) characteristics for NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples on n-type substrate with (a) 0 cycle, (b) 10 cycles, (c) 50 cycles, and (d) 100 cycles of in situ ALD DEZ interface passivation. 56       |

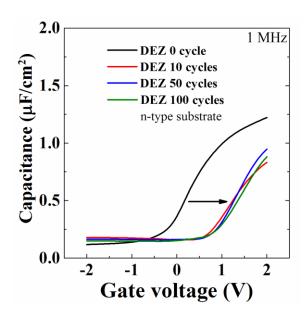

| Figure 3.10 | O Comparison of C-V curves at 1 MHz for NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples on n-type substrate with 0 cycle, 10 cycles, 50 cycles, and 100 cycles of in situ ALD DEZ interface passivation                                                      |

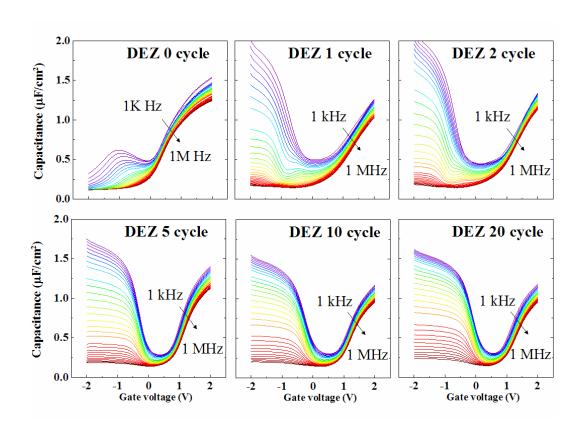

| Figure 3.11 C-V frequency dispersion characteristics (from 1 kHz to 1 MHz) for n-type In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP with 5 nm Hf <sub>0.5</sub> Zr <sub>0.5</sub> O <sub>2</sub> as a function of the cycle number of in situ ALD DEZ treatment. Measurements were done at room temperature 295 K. 58                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.12 C-V frequency dispersion characteristics (from 1 kHz to 1 MHz) for n-type $In_{0.53}Ga_{0.47}As$ MOSCAP with 5 nm $Hf_{0.5}Zr_{0.5}O_2$ as a function of the cycle number of in situ ALD DEZ treatment. Measurements were done at low temperature 100 K59                                                                                |

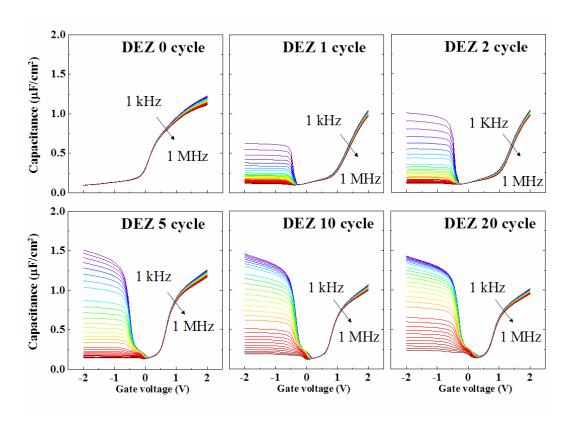

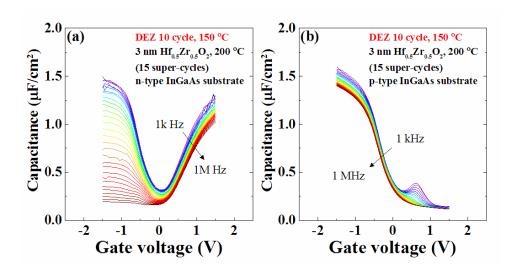

| Figure 3.13 C-V frequency dispersion (from 1 kHz to 1 MHz) characteristics for (a) n-type and (b) p-type $In_{0.53}Ga_{0.47}As$ MOSCAP with 10 cycles of in situ ALD DEZ treatment and ~3 nm $Hf_{0.5}Zr_{0.5}O_2$ gate insulator.                                                                                                                   |

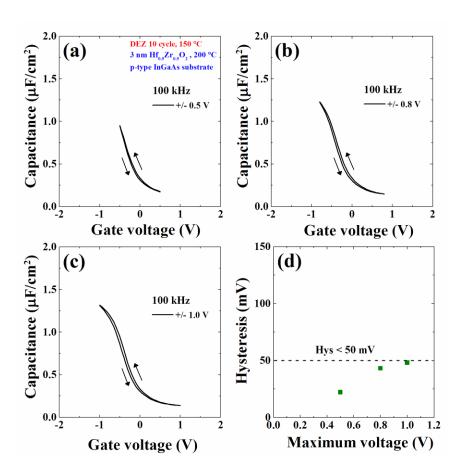

| Figure 3.14 C-V hysteresis characteristics of p-type In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP with 10 cycles of in situ ALD DEZ treatment and ~3 nm Hf <sub>0.5</sub> Zr <sub>0.5</sub> O <sub>2</sub> gate insulator as a function of the maximum measurement voltage (a) 1.0 V, (b) 1.5 V, (c) 2.0 V, and (d) the corresponding hysteresis. |

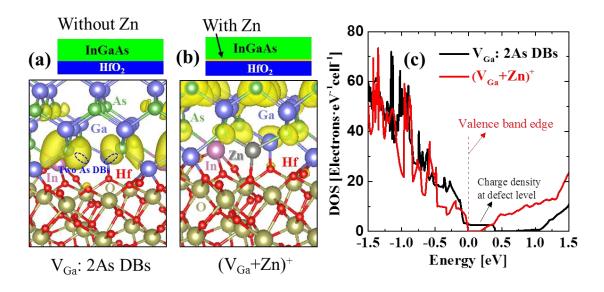

| Figure 3.15 First-principle calculation using DFT in the case of (a) without a Zn atom, (b) with a Zn atom to passivate two As dangling bonds generated by Ga vacancy at the HfO <sub>2</sub> /InGaAs interface, and (c) the corresponding density of states for each cases63                                                                        |

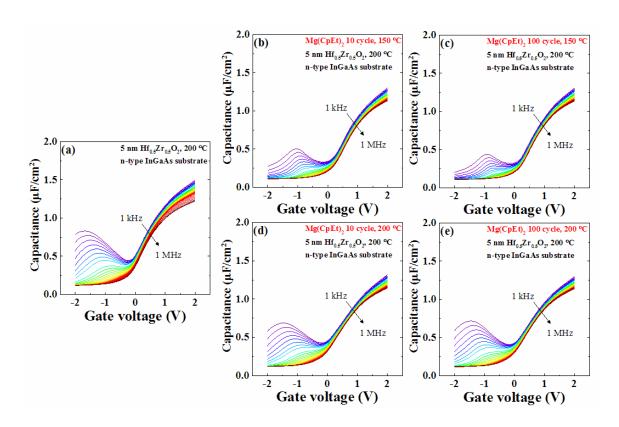

| Figure 3.16 C-V frequency dispersion (from 1 kHz to 1 MHz) characteristics for NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated n-type In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples (a) without and (b-e) with 10, 100 cycles of in situ ALD-Mg(CpEt) <sub>2</sub> treatment at either 150 °C or 200 °C                       |

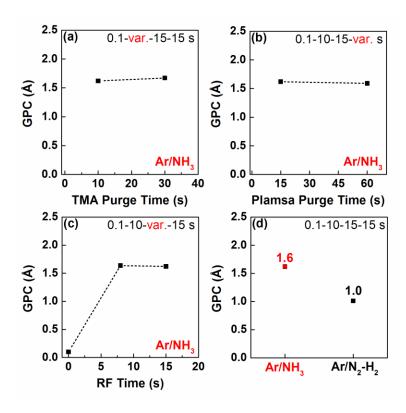

| Figure 3.17 Growth per cycle (GPC, Å) of hollow cathode PEALD-AlN grown at 250 °C as a function of (a) TMA purge time (b) plasma purge time (c) RF time and (d) plasma gas                                                                                                                                                                           |

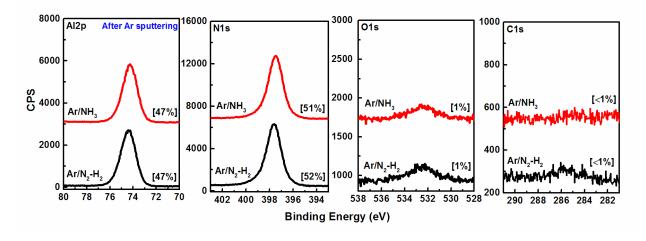

| Figure 3.18 XPS spectra of hollow cathode PEALD-AlN grown at 250 °C using Ar/NH <sub>3</sub> plasma or Ar/N <sub>2</sub> -H <sub>2</sub> (10%) plasma. Calculated atomic composition of each element is also provided.                                                                                                                               |

| Figure 3.19 C-V frequency-dispersion (from 1 kHz to 1 MHz) characteristics for In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples using ex situ grown ~3 nm hollow cathode PEALD-AlN interlayer on (a) n-type and (b) p-type substrate                                                                                                          |

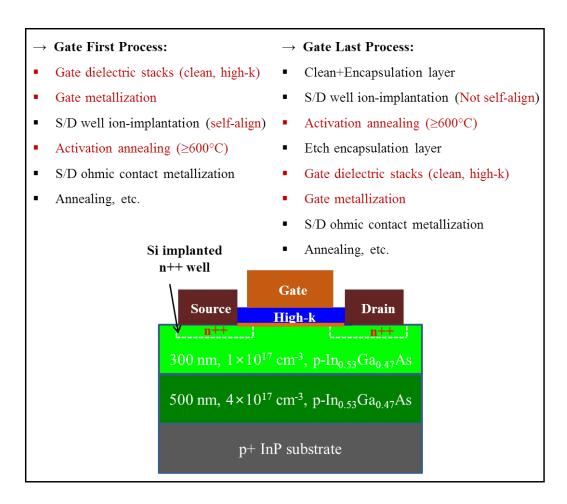

| Figure 3.20 Basic flow of gate-first and gate-last process for high-k/metal gate based inversion-type n-channel MOSFETs fabrication                                                                                                                                                                                                                  |

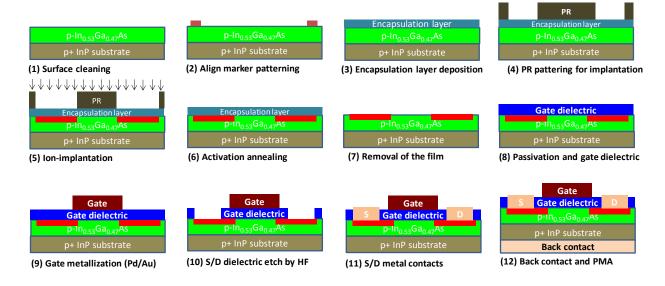

| Figure 3.21 Schematic of n-channel In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs fabrication process flow72                                                                                                                                                                                                                                       |

| Figure 3.22 Camera and optical microscope image of the In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs74                                                                                                                                                                                                                                            |

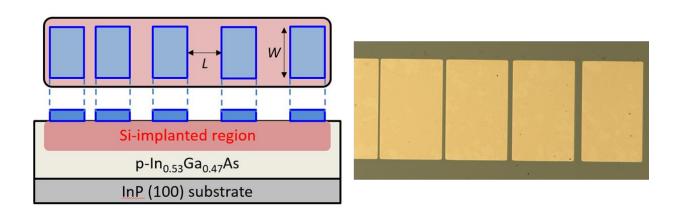

| Figure 3.23 | TLM structure on $In_{0.53}Ga_{0.47}As$ MOSFETs sample. Pad width (W) is 50 $\mu$ m and distance (L) is 4 $\mu$ m, 6 $\mu$ m, 8 $\mu$ m, 12 $\mu$ m, respectively                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

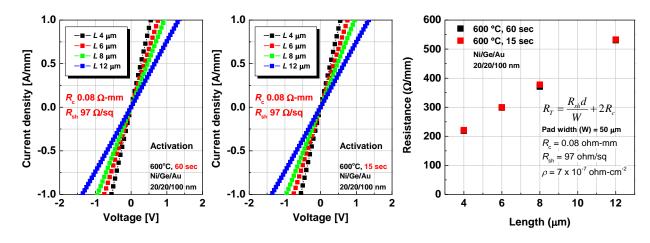

| Figure 3.24 | TLM results of n-channel MOSFETs with an activation annealing time of 15 s and 60 s at 600 °C in an N <sub>2</sub> ambient, respectively                                                                                                               |

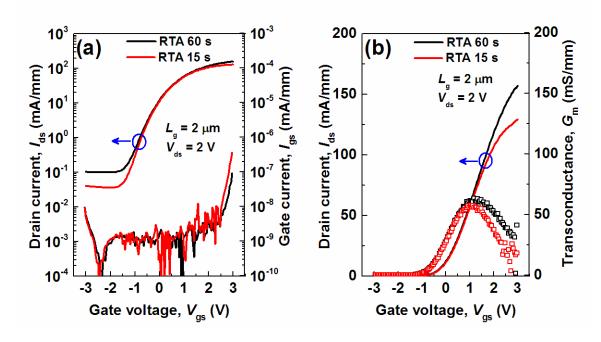

| Figure 3.25 | I <sub>ds</sub> -V <sub>gs</sub> transfer characteristics of n-channel In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs with 10 nm Al <sub>2</sub> O <sub>5</sub> gate dielectric, (a) log scale (b) linear scale                                      |

| Figure 3.26 | $I_{ds}$ - $V_{ds}$ output characteristics of n-channel $In_{0.53}Ga_{0.47}As$ MOSFETs with 10 nm $Al_2O_3$ gate dielectric, (a) RTA 60 s at 600 °C (b) RTA 15 s at 600 °C                                                                             |

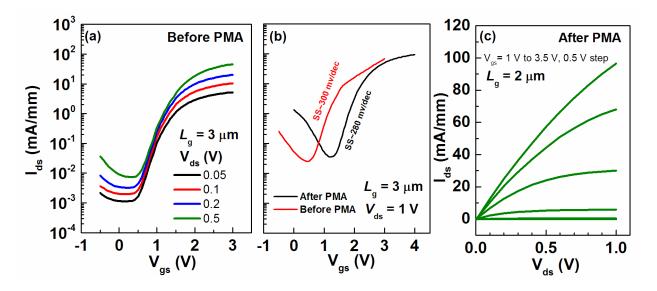

| Figure 3.27 | (a) (b) $I_{ds}$ - $V_{gs}$ transfer characteristics and (c) $I_{ds}$ - $V_{ds}$ output characteristics of n-channe $In_{0.53}Ga_{0.47}As$ MOSFETs with 10 cycles of in situ ALD DEZ treatment and 5 nm $Hf_{0.5}Zr_{0.5}O_2$ gate insulator.          |

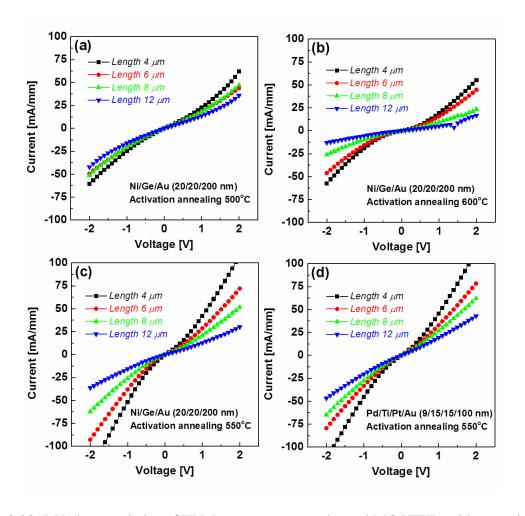

| Figure 3.28 | I-V characteristics of TLM structures on p-channel MOSFETs with an activation annealing time of 60 s in an N <sub>2</sub> ambient at (a) 500 °C, (b) 600 °C (c) 500 °C using Ni/Ge/Au stacks, and (d) at 550 °C using Pd/Ti/Pt/Au stacks, respectively |

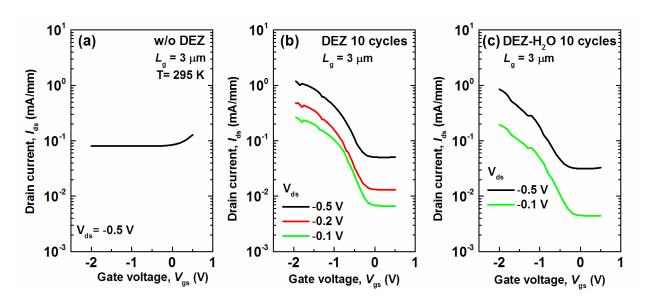

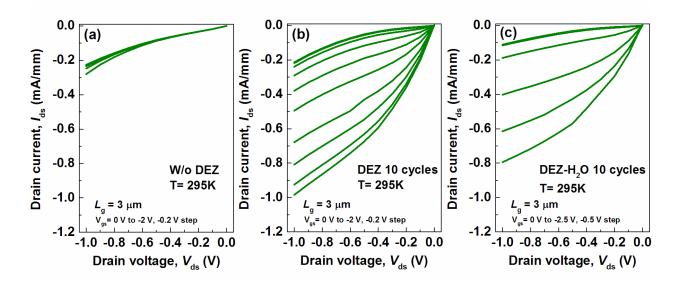

| Figure 3.29 | $I_{ds}$ - $V_{gs}$ transfer characteristics of p-channel $I_{0.53}Ga_{0.47}As$ MOSFETs (a) without DEZ treatment (b) with DEZ 10 cycles (c) with DEZ- $H_2O$ 10 cycles of treatment81                                                                 |

| Figure 3.30 | (a) $I_{ds}$ - $V_{ds}$ output characteristics of p-channel $In_{0.53}Ga_{0.47}As$ MOSFETs (a) withou DEZ treatment (b) with DEZ 10 cycles (c) with DEZ- $H_2O$ 10 cycles of treatment82                                                               |

| Figure 4.1  | Schematic of the AlGaN/GaN MIS-HEMTs fabrication process flow88                                                                                                                                                                                        |

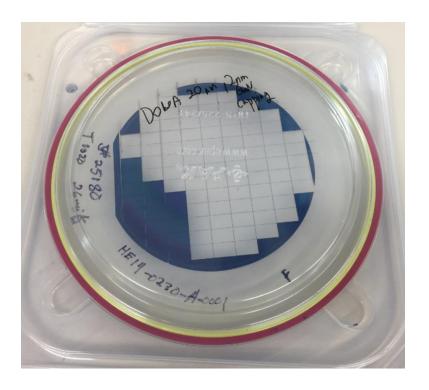

| Figure 4.2  | Coupons diced from 6-inch wafer used for AlGaN/GaN MIS-HEMTs fabrication88                                                                                                                                                                             |

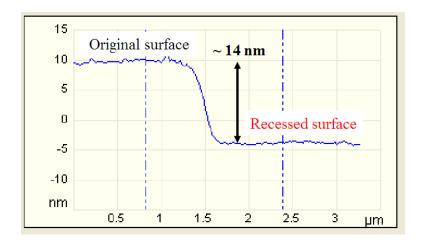

| Figure 4.3  | AFM line profile of a barrier recess step height of ~14 nm                                                                                                                                                                                             |

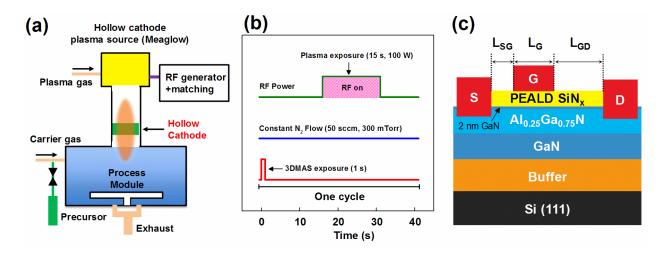

| Figure 4.4  | (a) Schematic of the hollow cathode PEALD reactor, (b) PEALD $SiN_x$ process sequence, and (c) schematic cross-sectional structure of $SiN_x/GaN$ MIS-HEMT91                                                                                           |

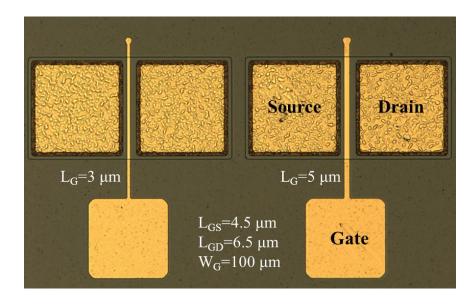

| Figure 4.5  | Optical microscope image of the completed GaN MIS-HEMTs                                                                                                                                                                                                |

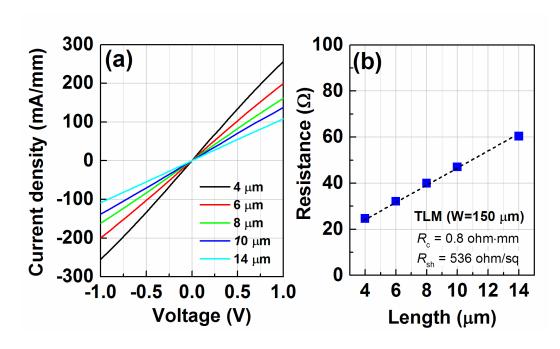

| Figure 4.6  | (a) I-V characteristics and (b) resistance of TLM structure after mesa isolation as a function of the distance (4 $\mu$ m, 6 $\mu$ m, 8 $\mu$ m, 10 $\mu$ m, and 14 $\mu$ m) between each pad. 93                                                      |

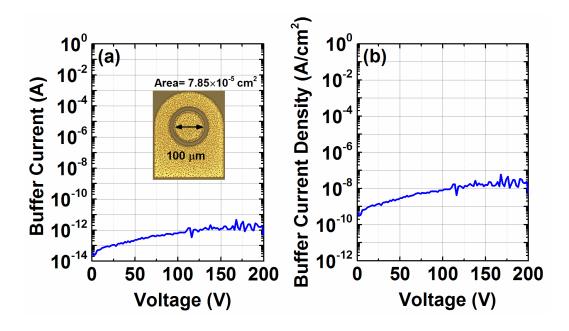

| Figure 4.7  | I-V breakdown characteristics of buffer leakage test structure after mesa isolation using (a) current (A) and (b) current density (A/cm²) as the unit93                                                                                                |

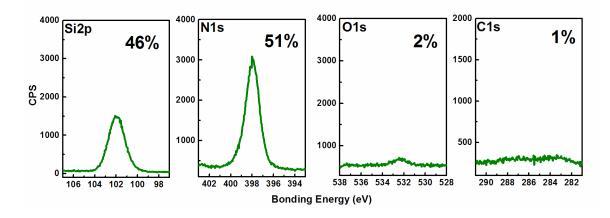

| Figure 4.8  | Ex situ XPS analysis of the PEALD SiN <sub>x</sub> film after 2 min argon sputtering94                                                                                                                                                                 |

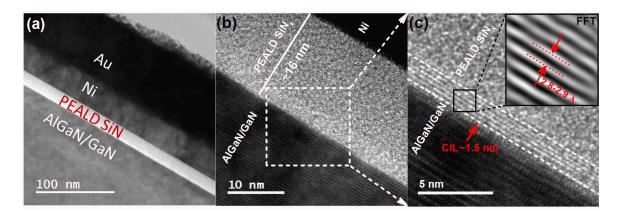

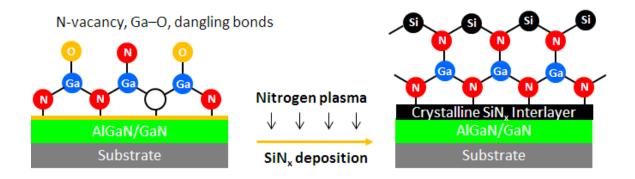

| Figure 4.9  | (a) (b) Cross-sectional HRTEM images of the gate stack of $SiN_x/GaN$ MIS-HEMT. (c) A higher magnification view of ~1.5 nm crystalline interfacial layer (CIL). The inset FFT image shows the d-spacing is 2.8-2.9 Å, indicating that the CIL is $\beta$ -phase $Si_3N_4$ .                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.10 | Schematic of a PEALD SiN <sub>x</sub> crystalline interfacial layer, which passivates the nitrogen vacancies and the dangling bonds terminated on the III-nitrides surface95                                                                                                                                                                                                                                                  |

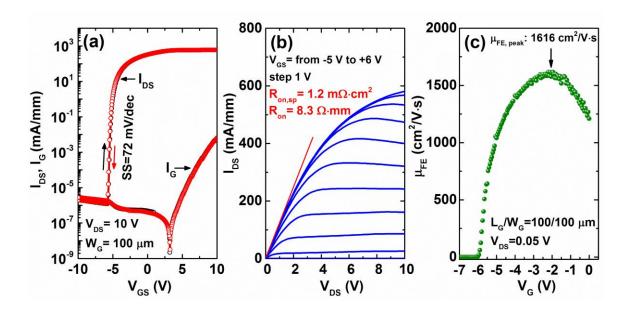

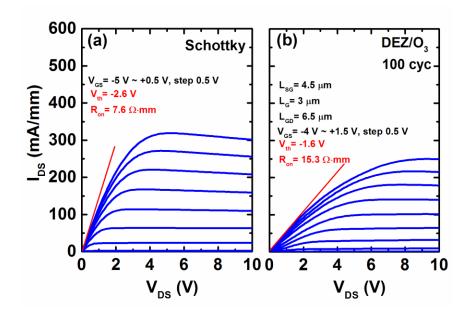

| Figure 4.11 | 1 (a) DC $I_{DS}/I_G-V_{GS}$ double sweep transfer curves and (b) $I_{DS}-V_{DS}$ output curves. $L_{GS}/L_G/L_{GD}=4.5/3/6.5~\mu m$ . (c) Field effective mobility extracted from a long channel device ( $W_G/L_G=100/100~\mu m$ )96                                                                                                                                                                                        |

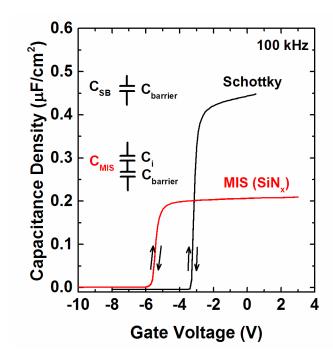

| Figure 4.12 | Bi-directional C-V hysteresis characteristics of a Schottky gate capacitor and a MIS-capacitor (16 nm PEALD $SiN_x$ ) measured at 100 kHz. The gate electrode diameter is 100 $\mu$ m.                                                                                                                                                                                                                                        |

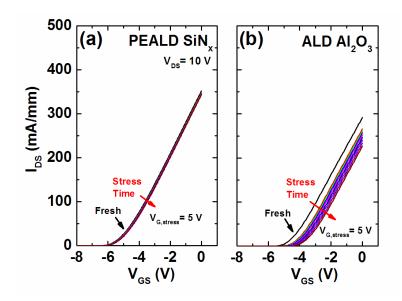

| Figure 4.13 | $I_{DS}$ - $V_{GS}$ transfer characteristics of MIS-HEMTs with (a) 16 nm PEALD SiN <sub>x</sub> and (b) 15 nm ALD Al <sub>2</sub> O <sub>3</sub> gate insulator under a constant gate bias stress of 5 V up to 3162 s. $L_{GS}/L_{G}/L_{GD}$ =4.5/5/11.5 $\mu$ m                                                                                                                                                              |

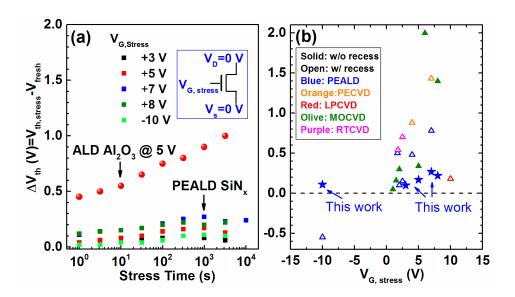

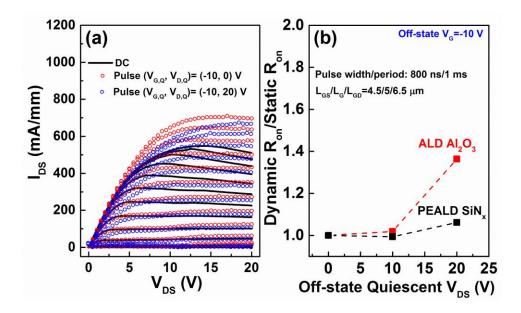

| Figure 4.14 | (a) Bias-induced $V_{th}$ instability of MIS-HEMTs using gate bias stress measurement at room temperature. The $\Delta V_{th}$ values are plotted as a function of the stress time. $L_{GS}/L_{G}/L_{GD}=4.5/5/11.5~\mu m$ . (b) Comparison of the $\Delta V_{th}$ values under different gate stress voltages for $10^3$ - $10^4$ s in this work with the results reported in the literatures using $SiN_x$ gate insulators. |

| Figure 4.15 | (a) I <sub>DS</sub> -V <sub>DS</sub> output curves of MIS-HEMTs with 16 nm PEALD SiN <sub>x</sub> gate insulator using DC and pulsed I–V measurements. (b) the extracted ratio of dynamic R <sub>on</sub> /DC static R <sub>on</sub> , compared to that of a sample using 15 nm ALD Al <sub>2</sub> O <sub>3</sub> gate insulator101                                                                                          |

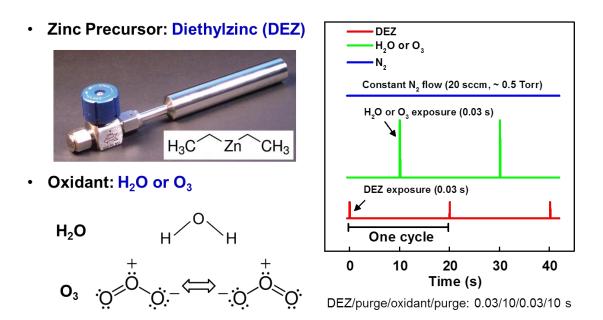

| Figure 5.1  | Schematic diagram of one cycle of ZnO ALD process                                                                                                                                                                                                                                                                                                                                                                             |

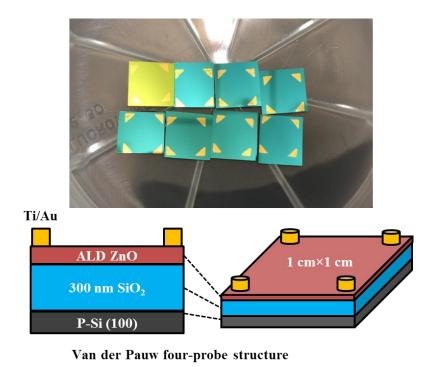

| Figure 5.2  | Samples for Hall effect measurement with Van der Pauw four-probe structure104                                                                                                                                                                                                                                                                                                                                                 |

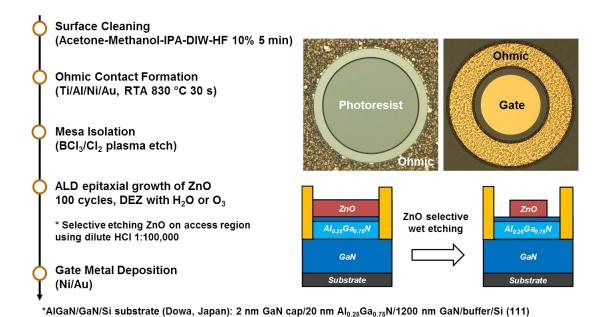

| Figure 5.3  | Process Flow of fabricating AlGaN/GaN HEMTs with ALD-grown epitaxial ZnO cap layer. Selective etching technique was developed to define the pattern of ZnO105                                                                                                                                                                                                                                                                 |

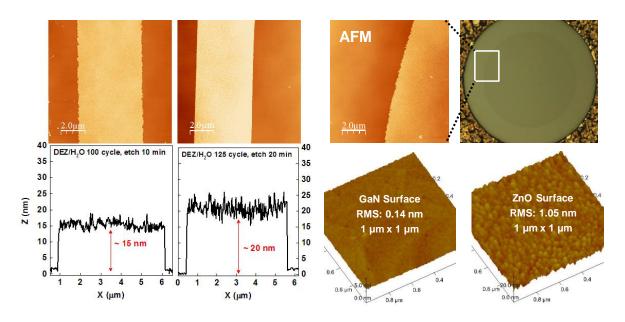

| Figure 5.4  | AFM characterization of ZnO step height on HEMT structures and surface morphology on a capacitor structure, after ZnO cap layer was defined by selective etching106                                                                                                                                                                                                                                                           |

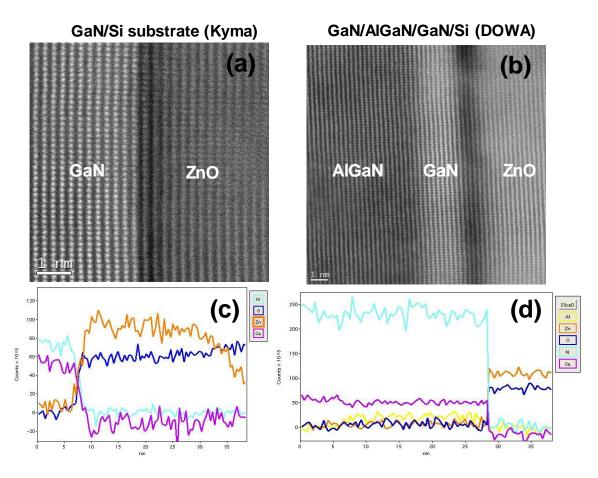

| Figure 5.5  | HRTEM images and corresponding energy dispersive spectroscopy (EDS) composition analysis of ALD ZnO on (a, c) GaN/Si substrate (b, d) GaN/AlGaN/GaN/Si substrate.                                                                                                                                                                                                                                                             |

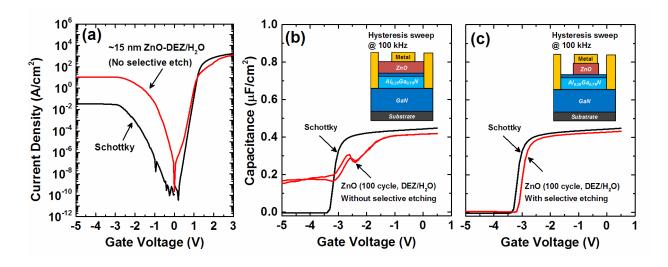

| Figure 5.6  | Comparison between the Schottky capacitor and the ZnO MOS capacitor. (a) I-V characteristics, (b) C-V characteristics without selective etching, and (c) C-V characteristics with selective etching. The diameter of gate electrode was 100 µm in this work              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

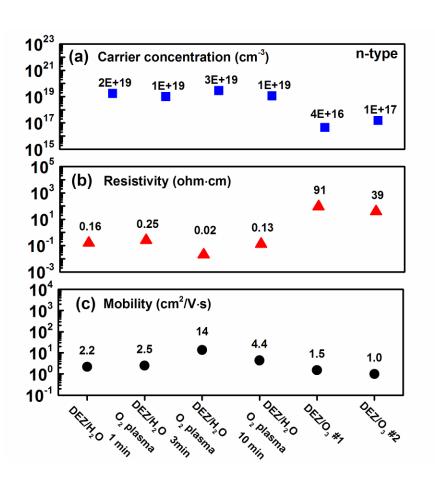

| Figure 5.7  | (a) Carrier concentration, (b) resistivity, and (c) mobility of the ALD ZnO films determined by Hall effect measurement                                                                                                                                                  |

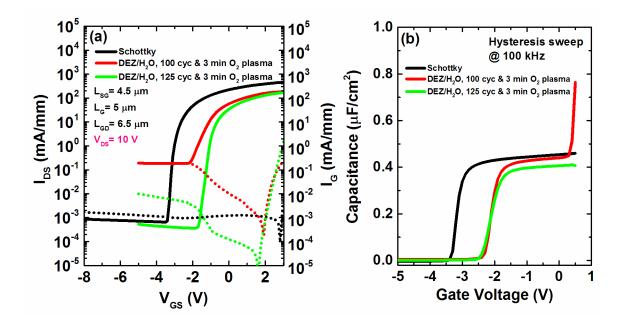

| Figure 5.8  | Comparison between the Schottky gate HEMT sample and the O <sub>2</sub> plasma treated H <sub>2</sub> O-based ZnO cap layer HEMT samples. (a) The V <sub>GS</sub> -I <sub>DS</sub> transfer characteristics and (b) the corresponding C-V characteristics of capacitors. |

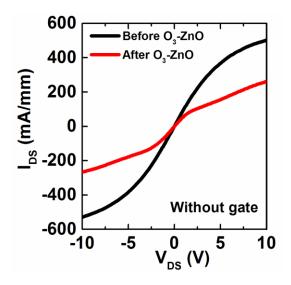

| Figure 5.9  | Comparison of source/drain two-terminal I-V curves before and after O <sub>3</sub> -based ZnO cap layer growth (DEZ/O <sub>3</sub> , 100 cycles)                                                                                                                         |

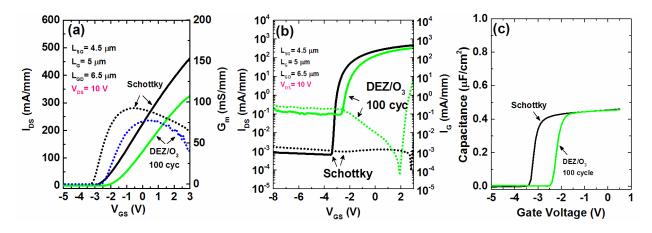

| Figure 5.10 | Comparison between the Schottky gate HEMT sample and the O <sub>3</sub> -based ZnO cap layer HEMT sample. (a) Linear scale, (b) log scale of the V <sub>GS</sub> -I <sub>DS</sub> transfer characteristics, and (c) the corresponding C-V characteristics                |

| Figure 5.11 | Comparison of the V <sub>DS</sub> -I <sub>DS</sub> output characteristics between (a) the Schottky gate HEMT sample and (b) the O <sub>3</sub> -based ZnO cap layer HEMT sample112                                                                                       |

# LIST OF TABLES

| Table 1.1  | The material properties of Si, Ge, and the representative III-V semiconductors [7-9]. 3                                                                                                                                          |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2  | The material properties of Si, Ge, and the representative III-N semiconductors [7-9].                                                                                                                                            |

| Table 1.3  | Basic material properties of ZnO and the representative III-N semiconductors [68, 69]                                                                                                                                            |

| Table 3.1  | The epitaxial structure information of n-type In <sub>0.53</sub> Ga <sub>0.47</sub> As wafer                                                                                                                                     |

| Table 3.2  | The epitaxial structure information of p-type In <sub>0.53</sub> Ga <sub>0.47</sub> As wafer                                                                                                                                     |

| Table 3.3  | $NH_4OH/(NH_4)_2S$ treated $In_{0.53}Ga_{0.47}As$ MOSCAP samples with ALD-grown $Hf_{0.5}Zr_{0.5}O_2$ and $HfO_2$ gate insulators.                                                                                               |

| Table 3.4  | NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples without and with interface passivation by in situ ALD DEZ and ALD DEZ/H <sub>2</sub> O surface treatment51  |

| Table 3.5  | Summary of the representative dopants of In <sub>0.53</sub> Ga <sub>0.47</sub> As and the corresponding ionization energy [94]54                                                                                                 |

| Table 3.6  | NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples with 0, 10, 50, and 100 cycles of in situ ALD DEZ interface passivation                                     |

| Table 3.7  | $NH_4OH/(NH_4)_2S$ treated $In_{0.53}Ga_{0.47}As$ MOSCAP samples with 0, 1, 2, 10, and 20 cycles of in situ ALD DEZ interface passivation                                                                                        |

| Table 3.8  | $NH_4OH/(NH_4)_2S$ treated $In_{0.53}Ga_{0.47}As$ MOSCAP samples with 10 cycles of in situ ALD DEZ treatment and ~3 nm $Hf_{0.5}Zr_{0.5}O_2$ gate insulator                                                                      |

| Table 3.9  | NH <sub>4</sub> OH/(NH <sub>4</sub> ) <sub>2</sub> S treated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAP samples without and with 10, 100 cycles of in situ ALD-Mg(CpEt) <sub>2</sub> treatment at either 150 °C or 200 °C64 |

| Table 3.10 | $NH_4OH/(NH_4)_2S$ treated $In_{0.53}Ga_{0.47}As$ MOSCAP samples using ex situ grown ~3 nm hollow cathode PEALD-AlN interlayer on (a) n-type and (b) p-type substrate68                                                          |

| Table 3.11 | $NH_4OH/(NH_4)_2S$ treated $In_{0.53}Ga_{0.47}As$ p-channel MOSFETs samples (no PMA)80                                                                                                                                           |

| Table 4.1  | The wafer epitaxial structure information of 6-inch AlGaN/GaN on Si wafer purchased from DOWA Electronic Materials Co., Ltd. (Tokyo, Japan)                                                                                      |

| Table 4.2  | Summary of the properties of the PEALD SiN <sub>x</sub> film.                                                                                                                                                                    |

#### **CHAPTER 1**

#### INTRODUCTION AND BACKGROUND

### 1.1 Introduction

The past two decades have witnessed revolutionary progress of the silicon metal-oxidesemiconductor field-effect transistor (Si MOSFET) technology and continuous scaling of device dimension, owing to the introduction of a series of innovative techniques such as strained-silicon, high-k/metal gate, multiple patterning, fin or gate-all-around (GAA) channel structure [1]. Although the efforts to further explore the limit of Si MOSFET technology never cease, researchers have realized the inevitable limitation (e.g., mobility and thermal conductivity) from channel material silicon itself. A high field-effect mobility is extremely critical to obtain highperformance MOSFETs for the applications in high-speed logic circuits. The high-performance and low-power-consumption logic computing will accelerate the development of machine learning, robotics, cloud computing, and internet of things (IoT). Fundamentally, the use of alternative high-mobility channel material in MOSFETs can result in a higher field-effect mobility. This triggered the need to investigate alternative high-mobility channel materials such as the III-V compound semiconductors [2], germanium (Ge), graphene, two-dimensional transition metal dichalcogenides (2D TMDs), and black phosphorus (BP) [3]. Among these novel channel materials, InGaAs has been considered a promising channel material of n-channel MOSFET (NMOS) in sub-7 nm technology node owing to the high electron mobility and appropriate band gap [4].

In addition, there is an ever-increasing demand for devices used in next generation highfrequency and high-power applications, such as radar system, satellite communication, mobile station, power switch, power amplifier, and power converter. Gallium nitride (GaN) has emerged as the material of choice for the next generation high-performance radio-frequency (RF) device and power devices, competing with the state-of-art devices using conventional semiconductor materials such as the silicon (Si), silicon carbide (SiC), and gallium arsenide (GaAs) [5, 6]. GaN is a wide band gap semiconductor with high critical electric field and high thermal conductivity, which are attractive material properties for power devices. Furthermore, GaN-based high electron mobility transistors (GaN HEMTs) using AlGaN/GaN and InAlN/GaN heterostructures exhibit high electron mobility and electron sheet density owing to the existence of two-dimensional electron gas (2DEG). Over more than 20 years of development, commercial available GaN HEMT products have demonstrated superior performance, including a high power density, high switching speed, high frequency, high working temperature, high breakdown voltage, low power-loss, low noise, and low on-resistance. Therefore, they are very suitable for the next generation high-frequency and high-power applications.

## 1.2 High Mobility III-V Compound Semiconductor Devices

### 1.2.1 Overview of InGaAs MOS Devices and Present Issues

The III-V compound semiconductors are referred as a family of semiconductors consisted of the elements in columns III and V of the periodic table, like GaAs, InAs, GaSb, and InP. In addition, ternary and quaternary alloys are attractive owing to the tunable properties. The basic material properties of Si, Ge, and the representative III-V semiconductor materials are tabulated in Table 1.1.

Table 1.1. The material properties of Si, Ge, and the representative III-V semiconductors [7-9].

| Properties                    | Si       | Ge       | GaAs   | In <sub>0.53</sub> Ga <sub>0.47</sub> As | InAs   | GaSb   | InSb   | InP    |

|-------------------------------|----------|----------|--------|------------------------------------------|--------|--------|--------|--------|

| Band gap                      | Indirect | Indirect | Direct | Direct                                   | Direct | Direct | Direct | Direct |

| Structure                     | DC       | DC       | ZB     | ZB                                       | ZB     | ZB     | ZB     | ZB     |

| χ(eV)                         | 4.05     | 4.0      | 4.07   | 4.5                                      | 4.9    | 4.06   | 4.38   | 4.38   |

| $E_{g}$ (eV)                  | 1.12     | 0.66     | 1.42   | 0.74                                     | 0.36   | 0.73   | 0.17   | 1.35   |

| $\mu_e$ (cm <sup>2</sup> /Vs) | 1350     | 3900     | 8500   | 13000                                    | 33000  | 3750   | 77000  | 4000   |

| $\mu_h (cm^2/Vs)$             | 450      | 1900     | 400    | 400                                      | 460    | 680    | 850    | 100    |

| $v_{e,sat}$ (10 $^7$ cm/s)    | 1.0      | 0.7      | 1.2    | 3                                        | 3.5    | -      | 5.0    | 0.67   |

| $\epsilon_{ m r}$             | 11.7     | 16       | 13.2   | 13.9                                     | 15.1   | 15.7   | 12.5   | 12.4   |

DC is diamond cubic, ZB is zinc blende,  $\chi$  is electron affinity.  $\mu_e$  is electron mobility,  $\mu_e$  is hole mobility,  $\nu_{e,sat}$  is electron saturation velocity, and  $\epsilon_r$  is relative permittivity (i.e. dielectric constant  $\kappa$ ).

Unlike Si and Ge with an indirect band gap and a diamond cubic crystal structure, GaAs and InGaAs are both direct bandgap semiconductor with a zinc blende crystal structure. The adjustable direct band gap of III-V alloys made them a research focus for optical applications such as infrared lasers and photonic detectors. More importantly, the high electron mobility of GaAs and In<sub>x</sub>Ga<sub>1-x</sub>As provides them a wider platform in the applications of high-performance NMOS devices. Particularly, a mid-range ternary composition of In<sub>x</sub>Ga<sub>1-x</sub>As (x=0.53) can be grown an InP substrate with precise lattice matching to obtain a high-quality single crystal. With higher electron mobility and narrower band gap, In<sub>0.53</sub>Ga<sub>0.47</sub>As has surpassed GaAs to be a better candidate for fabricating high-performance n-channel MOSFETs to deliver a high computing speed and a low operation voltage.

Although In<sub>x</sub>Ga<sub>1-x</sub>As possesses excellent materials properties, silicon MOSFETs are still playing a dominant role in ultra-large scale integration (ULSI). One important reason for the lag of progress in developing high-performance In<sub>x</sub>Ga<sub>1-x</sub>As MOSFETs is the difficulty to obtain highquality gate dielectric/In<sub>x</sub>Ga<sub>1-x</sub>As interface [10]. Unlike silicon with high-quality native oxide, III-V semiconductors and Ge are lacking a high-quality native oxide as the gate dielectric. Attempts to grow non-native oxides such as high-k dielectrics on In<sub>x</sub>Ga<sub>1-x</sub>As failed to obtain a high-quality interface due to the formation of a detrimental interfacial layer [11]. The interfacial layer consists a variety of complex electronic defects, including Ga-O bonds, As-O bonds, In-O bonds, elemental As, As-As dimer, vacancies, dangling bonds, and anti-sites. These interface imperfections are believed to cause a high interface trap density (Dit), which induces a large frequency dispersion and a failure to effectively modulate the electrostatic potential inside the III-V semiconductors, i.e. Fermi level pinning. Since the Fermi level typically moves between the conduction band edge and valence band edge, a defect state normally originates from an interface state with its energy level located within the band gap. For example, a hump-like feature shown in a capacitance-voltage (C-V) curve usually corresponds to the response of mid-gap interface traps of III-V semiconductors. The frequency dispersion of accumulation capacitance usually corresponds to the interface/border traps near the conduction band edge of the III-V semiconductors.

To remove the defective interfacial layer and passivate the III-V semiconductor surface without further oxidation during growing the gate dielectrics, many ex situ or in situ cleaning and passivation techniques have been investigated. Ex situ wet cleaning with solutions such as buffered oxide etch (BOE), hydrochloric acid (HCl), hydrofluoric acid (HF), ammonium hydroxide (NH<sub>4</sub>OH), and ammonium sulfide (NH<sub>4</sub>)<sub>2</sub>S are widely used to remove the surface oxides and

passivate the surface [12, 13]. However, the surface can be immediately re-oxidized upon exposure to oxygen and moisture in the ambient air.

This problem was effectively addressed by growing thin interfacial passivation layer (IPL) or Si precursor treatment including amorphous Si [14], Ge [15], SiH<sub>4</sub> treatment [16], Si<sub>2</sub>H<sub>6</sub> treatment [17], SiH<sub>4</sub>/NH<sub>3</sub> treatment [18], AlN IPL[19], AlON IPL [20], and ZnO IPL [21]. By depositing a thin IPL (0.5–1.5 nm) to passivate the surface, the oxidation of III-V semiconductor surface was greatly suppressed and D<sub>it</sub> was noticeably reduced. For example, the Si or Ge IPL allows oxygen gettering from the III-V semiconductor surface and reduces the high oxidization states of III-V semiconductor. However, it is difficult to precisely control the uniform coverage of thin IPL on the surface. Also, the formation of low dielectric constant (κ) interfacial silicon oxide or germanium oxide forbids the continuous scaling of effective oxide thickness (EOT).

As the device fabrication approaches atomic-scale dimensions, interface passivation at atomic-scale dimensions are preferred. To prepare only a few angstroms (Å) of the interfacial layer, atomic layer deposition (ALD) is a very promising technique to meet this requirement [22]. In addition, ALD is also considered a suitable method to grow highly uniform gate dielectrics with atomic scale precision. The detailed description about ALD will be presented in section 1.3.

## 1.2.2 Overview of AlGaN/GaN HEMTs and Present Issues

AlN, GaN, and InN belong to III-V semiconductors, and they are usually referred as III-nitride (III-N) semiconductors [23]. Simply by replacing As atom with N atom, the materials properties of III-N semiconductors totally differ from those of their counterparts

(AlAs/GaAs/InAs). The basic material properties of Si, Ge, and the representative III-N semiconductors are tabulated in Table 1.2.

Table 1.2. The material properties of Si, Ge, and the representative III-N semiconductors [7-9].

| Properties                         | Si       | Ge       | GaAs   | $In_{0.53}Ga_{0.47}As$ | AlN    | GaN         | InN    |

|------------------------------------|----------|----------|--------|------------------------|--------|-------------|--------|

| Band gap                           | Indirect | Indirect | Direct | Direct                 | Direct | Direct      | Direct |

| Structure                          | DC       | DC       | ZB     | ZB                     | WZ     | WZ          | WZ     |

| χ(eV)                              | 4.05     | 4.0      | 4.07   | 4.5                    | 0.6    | 4.1         | 5.8    |

| $E_{g}\left( eV\right)$            | 1.12     | 0.66     | 1.42   | 0.74                   | 6.2    | 3.4         | 0.7    |

| $\mu_e$ (cm <sup>2</sup> /Vs)      | 1350     | 3900     | 8500   | 13000                  | 1100   | 400 (bulk)  | 3600   |

|                                    |          |          |        |                        | 1100   | 1500 (2DEG) |        |

| $\mu_h  (cm^2/V_S)$                | 450      | 1900     | 400    | 400                    | 14     | 10          | 30     |

| $v_{e,sat}$ (10 <sup>7</sup> cm/s) | 1.0      | 0.7      | 1.2    | 3                      | 1.5    | 1.5-2       | 1.0    |

| $\epsilon_{\rm r}$                 | 11.7     | 16       | 13.2   | 13.9                   | 8.5    | 8.9         | 15.3   |

DC is diamond cubic, ZB is zinc blende, WZ is wurtzite,  $\chi$  is electron affinity.  $\mu_e$  is electron mobility,  $\mu_e$  is hole mobility,  $\nu_{e,sat}$  is electron saturation velocity, and  $\epsilon_r$  is relative permittivity (i.e. dielectric constant  $\kappa$ ).

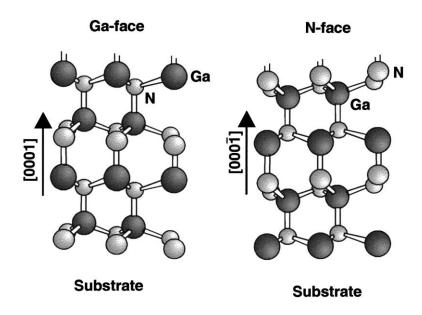

Although the III-N semiconductors can exist in both the zinc blende and wurtzite crystal structure, the wurtzite form with noncentrosymmetric (lacking inversion symmetry) crystal structure along the [0001] c-axis has been mainly investigated. There is a strong spontaneous polarization (P<sub>SP</sub>) present in the wurtzite crystal structure owing to the cation-anion (metal-nitrogen) dipole moment. The direction (polarity) of P<sub>SP</sub> depends on the crystal orientation relative to the substrate. As shown in Figure 1.1, there are two types of polarity in the wurtzite GaN crystal structure: Ga-face and N-face polarity [24]. The direction of P<sub>SP</sub> is parallel to the [0001]

orientation: pointing towards (down direction) the substrate for the Ga-face crystal whereas pointing opposite to (up direction) the substrate for the N-face crystal.

Figure 1.1. Schematic diagram of the crystal structure of wurtzite GaN with Ga-face and N-face polarity [24]. Reprinted from Ambacher et al., Journal of Applied Physics 85, 3222 (1999), with the permission of AIP Publishing.

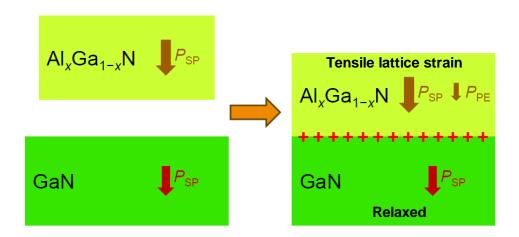

Figure 1.2. Schematic diagram of the spontaneous polarization and piezoelectric polarization existing in an Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterostructure, Ga-face polarity is assumed [25]. Adapted from ESSDERC 2013 tutorial, "High Voltage GaN HEMT devices and modelling" by Dr. Stephen Sque.

When lattice strain is present due to the lattice mismatch, a piezoelectric polarization ( $P_{PE}$ ) will be induced in wurtzite III-N semiconductors. The direction of  $P_{PE}$  not only depends on the crystal orientation (Ga-face or N-face), but also depends on the nature of the strain (compressive or tensile). One important application of the inherent polarization behavior is to form the heterostructures such as  $Al_xGa_{1-x}N/GaN$  and  $In_xAl_{1-x}N/GaN$ . As shown in Figure 1.2, in the case of an  $Al_xGa_{1-x}N/GaN$  heterostructure (Ga-face polarity is assumed), the direction of spontaneous polarization ( $P_{SP}$ ) is pointing to the substrate. When an  $Al_xGa_{1-x}N$  layer is epitaxially grown on a GaN substrate, due to the presence of a tensile lattice strain (lattice constant: AlN < GaN), there is additional piezoelectric polarization induced in the  $Al_xGa_{1-x}N$  layer with the same direction. In the case of the GaN substrate, the lattice is relaxed (strain-free) and the piezoelectric polarization does not exist.

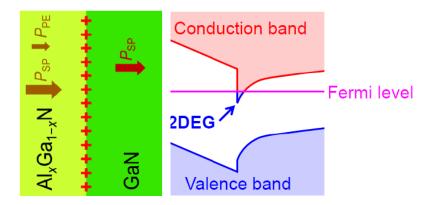

As illustrated in Figure 1.3, the strong polarization induces the band bending, and the Fermi level moves above the conduction band edge of GaN at the heterointerface. Electrons will populate near the interface and form two-dimensional electron gas (2DEG). The 2DEG can be confined by the energy barrier near the  $Al_xGa_{1-x}N/GaN$  interface due to presence of the conduction band offset between  $Al_xGa_{1-x}N$  and GaN. Interestingly, the lattice-matched  $In_xAl_{1-x}N/GaN$  heterostructures are currently investigated as the alternatives to the conventional  $Al_xGa_{1-x}N/GaN$  heterostructures [26]. There is a larger spontaneous polarization while no strain-induced piezoelectric polarization present in an  $In_xAl_{1-x}N/GaN$  heterostructure. The mobility degradation related to lattice strain is expected to be effectively suppressed.

Figure 1.3. Schematic diagram of the spontaneous polarization and piezoelectric polarization existing in an  $Al_xGa_{1-x}N/GaN$  heterostructure and the corresponding energy band diagram [25]. Adapted from ESSDERC 2013 tutorial, "High Voltage GaN HEMT devices and modelling" by Dr. Stephen Sque.

Without any intentional doping, the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN channel (2DEG) shows high sheet carrier density (~10<sup>13</sup> cm<sup>-2</sup>), high electron mobility (~1500 cm<sup>2</sup>/Vs), and high electron saturation velocity (~2.5×10<sup>7</sup> cm/s vs. 1.0×10<sup>7</sup> cm/s for Si), which are attributed to the effective suppression of mobility degradation by surface roughness scattering and impurity scattering. These exceptional electron transport characteristics make way for the development of high electron mobility transistors (HEMTs) operated at high frequencies. In addition, the excellent chemical/thermal stability, the high critical electric field (E<sub>c</sub>~3 MV/cm vs. 0.3 MV/cm for Si), and the wide band gap (3.4 eV vs. 1.12 eV for Si) allow GaN HEMTs to operate at high-temperature (>250 °C) and high-voltage conditions (>600 V). Regarding the limitation from the lateral device structure, the vertical GaN power devices have been investigated for a higher voltage conditions (>1000 V) [27].

Three mainstream substrates for AlGaN/GaN HEMTs are sapphire (Al<sub>2</sub>O<sub>3</sub>), SiC, and silicon (111). Al<sub>2</sub>O<sub>3</sub> substrate is inexpensive, but it suffers from poor epitaxy quality (a large dislocation density due to a large lattice mismatch with GaN) and poor thermal conductivity. SiC

substrate provides a high epitaxy quality and a high thermal conductivity, but the manufacturing cost is very high. GaN HEMTs on SiC are targeted at the performance-oriented applications. Compared to the Al<sub>2</sub>O<sub>3</sub> and the SiC substrate, the Si substrate can offer a larger wafer size (cost-effective) and is compatible with the mainstream CMOS production lines in the semiconductor fabs. Therefore, the industrial community has devoted tremendous efforts to developing CMOS-compatible technology (e.g., gold-free ohmic contact, Ga contamination prevention) to fabricate GaN HEMTs on Si substrate [28].

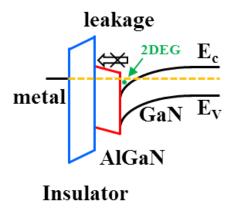

Figure 1.4. Schematic band diagram of a GaN MIS-HEMT structure using a gate insulator to reduce the gate leakage current.

In addition, a low gate leakage current is extremely important for power device application. The use of a metal-insulator-semiconductor (MIS) structure can reduce the gate leakage current of GaN HEMTs [29], as shown in Figure 1.4. Early attempts to grow gate dielectrics focused on using conventional deposition methods including plasma-enhanced vapor deposition (PECVD), thermal CVD, and physical vapor deposition (PVD). However, these methods suffered from poor film quality, non-uniform thickness, high thermal budget, or ion bombardment damage. Inspired by the

pioneering work using ALD Al<sub>2</sub>O<sub>3</sub> as a gate dielectric on GaN HEMTs by Ye et al. [30], as well as encouraged by the successful integration of ALD high-k dielectrics into the Si CMOS platform for mass production, the GaN community has considered ALD a highly attractive method to grow high-quality gate dielectrics for AlGaN/GaN MIS-HEMTs. The past decade witnessed a boost of research efforts and an unprecedented improvement of device performance. However, people have realized that there are still many issues and challenges to address to obtain high performance and high reliability.

I. Gate region: ΔV<sub>th</sub>

II. Access region: Dynamic R<sub>on</sub>

II Gate

II Gate

Dielectric

S Θ Θ Θ Θ Θ Θ D

AlGaN Traps

GaN

Channel

Figure 1.5. Schematic diagram of a GaN MIS-HEMT structure with the presence of traps near the dielectric/III-N interface on either (I) gate region or (II) access region.

Figure 1.5 shows a schematic diagram of a MIS-HEMT structure with the presence of traps near the dielectric/III-N interface on either gate region or access region. These traps may capture and emit electrons dynamically during the device operation. The trapping/detrapping of interface traps and border traps near the dielectric/III-N interface may induce several reliability issues [31]. One of the issues is the threshold voltage instability [32, 33]. The  $V_{th}$  instability is typically referred

as the  $V_{th}$  hysteresis and  $V_{th}$  drift under a forward or large reverse gate bias, which is because of the interface/border traps under the gate region. The traps with captured electrons act as fixed charge (usually negative charge for acceptor-like traps) and induced the change of  $V_{th}$ . Temperature also directly impact the  $V_{th}$  instability since it can change the emission time constant of traps.

On the other hand, electrons captured by the traps can induce another problem called dynamic on-resistance (R<sub>on</sub>) or current collapse. Specifically, the interface/border traps and the buffer layer traps from gate-to-drain region have more influence since a high electric field exists in this region. Electrons can be injected from the gate or the substrate, and then captured by the traps. During fast switching operation, the captured electrons may not be immediately emitted. As a result, the filled trap acts as a negatively charged virtual gate, which screens (or depletes) the electrons in the 2DEG channel and causes a temporarily reduced drain current [34]. As a symptom of current collapse, the R<sub>on</sub> extracted from pulsed I-V output curves increases with the increasing of quiescent drain voltage.

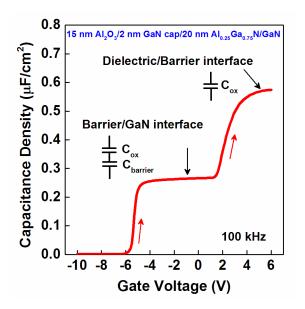

Figure 1.6 shows a representative C-V curve of a GaN MIS-capacitor. There are two major interfaces in a typical MIS-capacitor structure: the barrier/GaN interface and the dielectric/III-N barrier interface. First, the forward gate bias modulates the Fermi level to move above the conduction band edge of GaN. Electrons accumulate at the barrier/GaN interface to form the 2DEG channel. There will be no interaction between 2DEG and the traps near the dielectric/III-N barrier interface because of the physical separation by the barrier. At this moment, the first slope appears in the C-V characteristics. The saturated capacitance is a total capacitance of the dielectric capacitance ( $C_{ox}$ ) and the barrier capacitance ( $C_{barrier}$ ) in series connection. The value is smaller

than that of Schottky gate structure with only the barrier capacitance ( $C_{barrier}$ ). If the forward gate bias is large enough to allow the electrons to spill over the barrier, the electrons will populate at the dielectric/III-N barrier interface. The second slope with higher capacitance ( $\sim C_{ox}$ ) appears in the C-V characteristics at a larger forward gate bias. At this moment, electrons can communicate with the traps near the dielectric/III-N barrier interface via trapping/detrapping process [29].

Figure 1.6. Representative C-V curve of a GaN MIS-capacitor measured at 100 kHz with Ni/Au gate electrode.

As reported in the literature, the materials utilized for the gate insulator of GaN MIS-HEMTs includes Al<sub>2</sub>O<sub>3</sub> [30, 35], ZrO<sub>2</sub> [36, 37], HfO<sub>2</sub> [38], SiO<sub>2</sub> [39], SiON [40], SiN<sub>x</sub> [41, 42], Sc<sub>2</sub>O<sub>3</sub> [43], MgCaO [44, 45]. In addition, various dielectric/III-nitrides interface passivation techniques have been proposed, such as plasma nitridation [46, 47], ultra-thin AlN [48, 49], SiN<sub>x</sub> [50], or crystalline oxide interlayer [51, 52]. Among the gate insulator candidates, silicon nitride (SiN<sub>x</sub>) has a band gap of 5.3 eV and has a type II staggered band alignment with GaN (E<sub>g</sub>=3.4 eV) and Al<sub>0.3</sub>Ga<sub>0.7</sub>N (E<sub>g</sub>=4.2 eV) [53]. The large conduction band offsets (2.0 eV with GaN and 2.3 eV

with  $Al_{0.3}Ga_{0.7}N$ , respectively) allow low gate leakage current under a forward gate bias. Furthermore,  $SiN_x$  can form a good interface with III-nitrides by passivating the nitrogen vacancies, Ga dangling bonds and suppressing the Ga–O bonds formation [42]. In addition,  $SiN_x$  is a mature dielectric material that has high breakdown field and is being widely used in Si-CMOS industry. Therefore,  $SiN_x$  gate insulator has attracted great research interests.

For example, Moens et al. have demonstrated CMOS-compatible 650 V rated depletion mode (D-mode) AlGaN/GaN MIS-HEMTs on Si using in situ metalorganic chemical vapor deposited (MOCVD) SiN<sub>x</sub> as a gate dielectric and passivation layer on the access region [54]. The devices showed a good  $V_{th}$  stability ( $\Delta V_{th} < 400 \text{ mV}$ ) at a high working temperature of 200 °C, as well as low dynamic R<sub>on</sub> (<20%, V<sub>DS</sub>=600 V) by using gate/source field plate structures and PECVD SiN<sub>x</sub>/polyimide passivation layers. However, in situ MOCVD SiN<sub>x</sub> cannot be utilized as a gate insulator of gate-recessed MIS-HEMTs. Hua et al. have realized high-performance and reliable enhance-mode (E-mode) GaN MIS-FETs by adopting ex situ 2-nm-thick low-temperature (300 °C) PECVD SiN<sub>x</sub> interfacial layer and 15-nm-thick high-temperature (780 °C) low pressure chemical vapor deposited (LPCVD) SiN<sub>x</sub> as the gate insulator stack [50]. The thin PECVD-SiN<sub>x</sub> interfacial layer protected the etched GaN surface from Ga and N atoms out-diffusion, as well as oxidation, during the initial stage of high-temperature LPCVD process. The subsequent LPCVD-SiN<sub>x</sub> layer ensured the high bulk quality of the gate insulator stack owing to the high process temperature. However, either in situ MOCVD approach (>1000 °C) or ex situ LPCVD (> 700 °C) approach raises the thermal budget of device fabrication. High temperature causes unwanted high thermal stress due to the difference in thermal expansion coefficient of epitaxial layers and the underlying substrate. Furthermore, high temperature is not compatible with ohmic-first process

flow, as well as indium nitride (InN)-based MIS-HEMTs fabrication due to the InN decomposition (T<sub>decomposition</sub>>630 °C) [55].