Erik Jonsson School of Engineering and Computer Science

2012-12-20

# Performance and Stability of Solution-Based Cadmium Sulfide Thin Film Transistors: Role of CdS Cluster Size and Film Composition

A. L. Salas-Villasenor, et al.

© 2012 American Institute of Physics

## Performance and stability of solution-based cadmium sulfide thin film transistors: Role of CdS cluster size and film composition

A. L. Salas-Villasenor, I. Mejia, M. Sotelo-Lerma, B. E Gnade, and M. A. Quevedo-Lopez

Citation: Appl. Phys. Lett. 101, 262103 (2012); doi: 10.1063/1.4773184

View online: http://dx.doi.org/10.1063/1.4773184

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v101/i26

Published by the American Institute of Physics.

#### **Related Articles**

On reverse gate leakage current of GaN high electron mobility transistors on silicon substrate Appl. Phys. Lett. 102, 113510 (2013)

Bias stress effect in polyelectrolyte-gated organic field-effect transistors Appl. Phys. Lett. 102, 113306 (2013)

Bandgap engineering of group IV materials for complementary n and p tunneling field effect transistors Appl. Phys. Lett. 102, 113106 (2013)

Performance enhancement of poly(3-hexylthiophene) organic field-effect transistor by inserting poly(methylmethacrylate) buffer layer Appl. Phys. Lett. 102, 111607 (2013)

Bias stress effect in polyelectrolyte-gated organic field-effect transistors APL: Org. Electron. Photonics 6, 50 (2013)

#### Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

#### ADVERTISEMENT

### Performance and stability of solution-based cadmium sulfide thin film transistors: Role of CdS cluster size and film composition

A. L. Salas-Villasenor, <sup>1</sup> I. Mejia, <sup>1</sup> M. Sotelo-Lerma, <sup>2</sup> B. E Gnade, <sup>1</sup> and M. A. Quevedo-Lopez <sup>1,a)</sup>

<sup>1</sup>Department of Materials Science and Engineering, University of Texas at Dallas, Richardson, Texas 75080, USA

(Received 25 October 2012; accepted 10 December 2012; published online 27 December 2012)

Improved carrier mobility and threshold voltage ( $V_T$ ) stability in cadmium sulfide (CdS) thin film transistors (TFTs) were studied and attributed to larger grain clusters in thicker CdS films rather than individual crystallite size. Non-zero  $V_T$  shifts ( $\sim 200\, \text{mV}$ ) in thicker films are attributed to the presence of cadmium hydroxide [Cd(OH)2] at the dielectric/CdS interface resulting from the chemical bath deposition process used to deposit the CdS films.  $V_T$  and mobility analyses indicate that clusters of CdS grains have a larger impact on TFT performance and stability than the presence of impurities in the bulk of the CdS. TFTs using this fabrication method achieved mobilities of  $\sim 22\, \text{cm}^2/\text{Vs}$  with  $V_T$  of 7 V and  $\Delta V_T$  of  $< 200\, \text{mV}$  after testing. The maximum processing temperature is  $100\,^{\circ}\text{C}$  which makes this process compatible with flexible substrates. ©  $2012\,$ American Institute of Physics. [http://dx.doi.org/10.1063/1.4773184]

A relatively simple fabrication procedure, low deposition temperature, and the possibility to use virtually any substrate makes chemical bath deposited cadmium sulfide (CdS) semiconducting films attractive for the fabrication of thin film transistors (TFTs) for large area applications. Although CdS TFT performance is better than a-Si:H, its electrical stability is not well understood. However, to enable the design of stable circuits, the TFTs must be electrically stable when subjected to many operating cycles under atmospheric conditions and standard electrical bias. Several studies have reported the stability behavior of multiple types of TFTs. 1-11 In organic TFTs, a pronounced shift in the threshold voltage (V<sub>T</sub>) under negative gate bias stress has been reported and identified as hole bipolaron formation.<sup>2</sup> Instabilities due to the movement of mobile ions under electrical stress have also been reported.<sup>3,4</sup> Variation in mobility ( $\mu$ ) due to the oxidation of the semiconductor layer and V<sub>T</sub> shift induced by trap sites at grain boundaries and the interface between the semiconductor layer and the gate dielectric surface have also been reported. Inorganic TFTs, such as hydrogenated amorphous Si (a-Si:H) TFTs, are also plagued by low electron mobility ( $\sim 1 \text{ cm}^2/\text{V}$  s) and well-known instabilities with respect to bias stressing<sup>6</sup> during light exposure.<sup>7</sup> TFTs based on amorphous oxide semiconductors, such as InGaZnO, are being used due to their higher electron mobility. Accurate and repeatable control of this complex material in mass production can be difficult and requires ultra-high vacuum deposition equipment. In order for ZnO-based TFTs to become pervasive, it is also crucial to overcome the problems of voltage dependent stability and reliability. 10 Previously, we reported on CdS TFTs with high mobility fabricated using a shadow mask process<sup>11</sup> as well as an approach to integrate CdS and pentacene transistors using photolithography to

demonstrate CMOS circuits fabricated at temperatures below 100 °C. 12

In this letter, we describe several factors that impact performance and V<sub>T</sub> stability of CdS-based TFTs fabricated using chemical bath deposition (CBD). In particular, we studied the impact of CdS cluster size evolution and the influence of Cd(OH)<sub>2</sub> and CdCN<sub>2</sub> impurities on the stability and performance of TFTs fabricated with the resulting CdS films. The CdS clusters are made up of multiple CdS crystals agglomerating together. We determined that mobility is highly sensitive to cluster size and not directly related to individual CdS grain size. This behavior is different to other systems where an increase in grain size results in increased mobility. 13-15 Grain boundaries can act as charge traps. Typically, improved TFT performance observed in some systems is generally associated to an increase in grain size. It has been reported that when the grain size is above a critical value, the carrier mobility is relatively independent of the crystallite size.<sup>14</sup> No reports on the effect of cluster size in these systems were found in the literature. For the CdS films reported here, there is no change in the individual CdS crystal size as function of film thickness. However, there is an increase in the cluster size as the film thickness increases, resulting in improved carrier mobility. We also identified Cd(OH)<sub>2</sub> at the dielectric/semiconductor interface as responsible for the non-zero V<sub>T</sub> shift observed in the CdS films. CdCN2 impurities have a minimal impact on V<sub>T</sub> instability and mobility.

The CdS-TFTs studied here were fabricated in a bottom-gate, top-contact configuration. All devices were fabricated on a heavily doped silicon wafer (p-type: boron; <0.005  $\Omega\,\mathrm{cm}$ ), which is also used as gate electrode. A 90-nm thick HfO2 dielectric film was deposited using atomic layer deposition (ALD) and the CdS semiconducting active layer was immediately deposited using a cadmium chloride/sodium citrate/thiourea system at  $70\,^{\circ}\mathrm{C}$ , described elsewhere.  $^{11,12}$

<sup>&</sup>lt;sup>2</sup>Department of Polymer and Materials Science, University of Sonora, Hermosillo, Mexico

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: mquevedo@utdallas.edu. Telephone: 1 -(940) 453-9939.

After deposition, the CdS films were cleaned in an ultrasonic bath with methanol, rinsed with distilled water, and then dried with N<sub>2</sub> gas. In order to grow the CdS films with different thicknesses, the deposition process was repeated five consecutive times with fresh solutions used for every deposition. <sup>16</sup> The deposition time was approximately 25 min for each deposition. For source/drain electrodes, 100 nm aluminum was deposited by e-beam through a shadow mask on top of the semiconductor layer. Channel width (W) and channel length (L) were  $500 \,\mu\text{m}$  and  $40 \,\mu\text{m}$ , respectively. Scanning electron microscopy (SEM) was performed to evaluate the morphological differences as a function of CdS thickness. Fourier transform infrared (FTIR) spectroscopy studies were used to investigate the chemical composition and to identify the presence of hydroxyl groups and/or any other species present in the resulting CdS films. Electrical characteristics of the TFTs were evaluated using current–voltage (I-V) measurements at room temperature with a 4200 Keithley semiconductor characterization system under dark conditions. The saturation and linear transfer curves were measured by applying a  $V_{DS}$  voltage of  $+20 \,\mathrm{V}$  or  $+1 \,\mathrm{V}$ , respectively. The gate voltage was swept from -5 V to +20 V. The electrical measurement sequence used in this letter is described as follows; first, the  $(I_D\hbox{-} V_G)$  characteristics were measured three consecutive times, followed by the output characteristic  $(I_D\hbox{-} V_D)$  measurements. Then, the same  $(I_D\hbox{-} V_G)$  sequence was used again to evaluate the  $V_T$  stability of the CdS-TFTs. We note that after the second  $I_D\hbox{-} V_G$  sweep, the threshold voltage shows no substantial changes. Although no  $V_T$  shift is observed after the 2nd swept, the  $V_T$  shift reported here is extracted from the  $V_T$  change between the 1st and 6th  $I_D\hbox{-} V_G$  measurement.

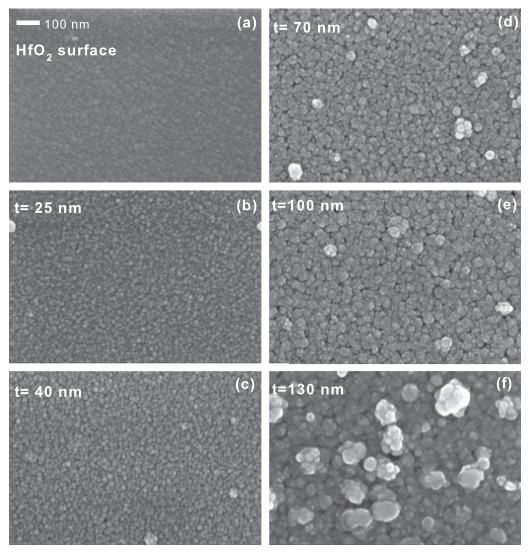

The evolution of the CdS surface morphology was analyzed as a function of film thickness. Figure 1 shows SEM images of the CdS films as function of thickness. There is a clear monotonic increase in cluster size as the thickness of the CdS films increases from 25 nm to 130 nm. This is expected since additional CdS growth time leads to larger clusters with the concomitant reduction in cluster boundary density. Test was used to evaluate the cluster size. We note that these clusters are constituted by CdS crystallites of ~22 nm and that the crystallite size remains constant throughout the entire CdS thickness evaluated, as shown later in this letter.

FIG. 1. SEM images of the CdS samples showing how the cluster size increases by increasing the CdS film thickness where (a) ALD HfO<sub>2</sub> layer, (b) t = 25 nm CdS, (c) t = 40 nm CdS, (d) t = 70 nm CdS, (e) t = 100 nm CdS, and (f) t = 130 nm CdS. t refers to CdS film thickness.

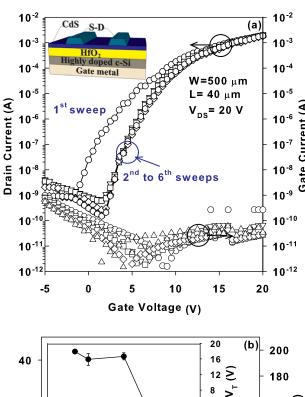

Device stability was investigated by measuring the change in  $V_T$  after consecutive  $I_D\text{-}V_G$  sweeps. The CdS-TFT structure used for these studies is shown in the inset of Figure 2(a). Figure 2(a) shows the gate current and the typical shifts observed in the transfer characteristics of the CdS–TFTs. The data shown in Figure 2(a) correspond to 100 nm thick CdS. The  $V_T$  shift was extracted between the 1st and the 6th sweep (no additional  $V_T$  shift was observed after the 6th sweep). Field-effect mobility  $(\mu_{sat})$  was calculated from the last sweep using the slope of the linear portion of the  $I_D^{-1/2}$  vs.  $V_G$  curve. The following equation was used for the calculations:  $^{18}$

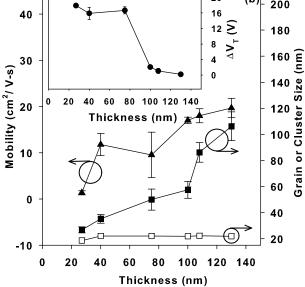

FIG. 2. (a)  $I_D$ - $V_G$  transfer characteristics showing  $V_T$  shift between the 1st and 6th sweep for 100 nm CdS TFTs measured in the saturation regime ( $V_{DS} = 20 \, V$ ). Inset shows a schematic cross section of the transistor used in this analysis. (b) Dependence of mobility ( $\mu_{sat}$ ), cluster ( $\blacksquare$ ), and grain size ( $\square$ ) with CdS film thickness. Grain size is independent of CdS film thickness, as determined by XRD. Inset shows threshold voltage ( $\Delta V_T$ ) shift reduction as function of CdS film thickness (nm).

$$I_D = \frac{W}{2L} C_i \mu_{sat} (V_G - V_T)^2,$$

(1)

where  $V_G$  is the gate voltage, W is the channel width, L is the channel length and  $C_i$  is the capacitance per unit area of the gate dielectric.

Leakage current remains low ( $\sim 10^{-11} A$ ) for these devices regardless of the thickness of the CdS film (Figure 2(a)). Mobilities were as high as  $22.0 \, \mathrm{cm^2/V}$  s for the thicker films and as low as  $1.2 \, \mathrm{cm^2/V}$  s for the thinnest CdS films. Threshold voltage shifts are typical for organic and inorganic low temperature TFTs devices.  $^{1-7,19}$  Gundlach  $^{19}$  and Ismail  $^{20}$  refer to these large initial shifts as an irreversible  $V_T$  shift because  $V_T$  does not recover to its initial value after several minutes. It is important to note that the initial  $V_T$  shift must be considered when extracting device parameters from the transfer curves. In the case of the devices described here,  $\mu_{\rm sat}$  is extracted from the last measurement, where the transfer curve remains stable.

Figure 2(b) shows the evolution of mobility, CdS cluster (■) and grain size (□) with film thickness. The inset in Figure 2(b) shows that the V<sub>T</sub> shift decreases as the CdS thickness increases. Figure 2(b) also shows that there is a monotonic increase in cluster size with thickness. Therefore, thinner films have smaller clusters, which result in a higher density of cluster boundaries that act as charge traps. Hence, the higher V<sub>T</sub> shift in thinner films is likely due to the higher density of cluster boundaries. The increase in mobility with CdS thickness observed in Figure 2(b) is also consistent with the increased cluster size. Cluster boundaries act as additional sites that scatter charge carriers. Larger cluster sizes result in a lower number of cluster boundaries, i.e., less scattering sites; thus, an increasing mobility is observed. 13-15 It is important to note that the CdS crystallite size, as determined using XRD, remains constant with film thickness as can shown in Figures 2(b) and 3(a). The large difference in intensity of the (002) peak is due to the thickness difference. This clearly indicates that the CdS cluster size has a larger impact on device performance and stability. Next, we evaluated the impact of impurities resulting from the CBD process.

Bulk defects in the CdS are likely to be present in the CdS films as a result of the CBD deposition process. 21-24 To study the presence of impurities in the CdS films, FTIR analyses were carried out using a Nicolet 6700: Thermo Fisher Scientific Inc., spectrometer in the range of 4000–400 cm<sup>-1</sup>. Each spectrum was obtained using 500 scans with 4 cm<sup>-1</sup> resolution. The FTIR spectra of the CdS thin films are shown in Figure 3(b). The broad absorption band in the range from 3600 to 3000 cm<sup>-1</sup> is attributed to OH<sup>-</sup> stretching.<sup>21</sup> C-H bonds are also observed at  $\sim 2950 \,\mathrm{cm}^{-1}$ . The peak at 2400 cm<sup>-1</sup> is attributed to S-H stretching. This S-H bond is only observed in thicker CdS films suggesting that is likely present in the bulk of CdS film. The CBD technique is an alkaline aqueous solution; therefore, the solution contains OH ions. Thus, the presence of OH in the FTIR results is not unexpected. Since no increase in the OH<sup>-</sup> peak with film thickness (Figure 3(b)) is observed, it is likely that this OH is located at the interface between the dielectric and the CdS

FIG. 3. (a) XRD spectra for different thickness of the CdS films show an increased intensity for thicker films. (b) FTIR absorption spectra of CdS film of different thicknesses showing three region:  $3600-3000\,\mathrm{cm}^{-1}$  attributed to OH $^-$  stretching at the dielectric/CdS interface,  $2200\,\mathrm{cm}^{-1}$  attributed to the C-N stretching vibrations of cyanamide in the bulk of the CdS film, and  $2400\,\mathrm{cm}^{-1}$  attributed to S-H in the bulk of the CdS films.

films. The presence of  $OH^-$  at the interface will generate interface traps with the associated shift in  $V_T$ .

The peak at about 2200 cm<sup>-1</sup> is attributed to the carbonnitrogen (C-N) stretching vibrations of cyanamide or thiocyanate. <sup>21–24</sup> Some groups have also proposed cadmium cyanamide, CdCN<sub>2</sub>, as a possible impurity phase in the CBD grown CdS films, <sup>21–24</sup> which could be understood from the decomposition reaction of thiourea during the initial stages of the CBD as follows:

$$SC(NH_2)_2 + 2OH^- \rightarrow S^{2-} + CdCN_2 + 2H_2O,$$

(2)

which in the presence of excess thiourea in the latter stages of the deposition undergoes the heterogeneous reaction

$$CdCN_2 + S^{2-} \rightarrow CdS + CN_2^{2-},$$

(3)

where  $S^{2-}$  is provided by the thiourea hydrolysis in the alkaline solution. This reaction has been proposed for the growth of CdS thin films by CBD. The Figure 3(b), we can observe that there is a monotonic increase in the C-N bonding with the increase of the CdS film thickness, also suggesting its presence in the bulk of the CdS. The C-N groups are likely resulting from the excess of thiourea used in the CBD reaction reported here. Since  $V_T$  shift reduces with increasing CdS film thickness, we can conclude that the presence of the C-N bonds does not directly affect the  $V_T$  shift. However, the non-zero shift of  $V_T$  in our devices, even for thick CdS films, can be attributed to hydroxyl groups at the dielectric/CdS interface.

In summary, high mobility ( $\sim$ 22 cm²/V s) and low V<sub>T</sub> (1.3 V) is achieved in TFTs fabricated using solution-based CdS films. Mobility and V<sub>T</sub> stability are improved in thicker CdS films due to a larger cluster size. A larger V<sub>T</sub> shift in thinner films is attributed to smaller clusters with the concomitant increase in cluster boundary density. C-N groups in the bulk of the CdS films have a reduced role in film performance and stability, whereas the residual V<sub>T</sub> shift in thicker films (200 mV) is attributed to the presence of Cd(OH)<sub>2</sub> at the interface between the dielectric and CdS.

The authors would like to thank CONACyT project 158281, the AFOSR project FA9550-10-1-0183, and the Army Research Lab for partial support of this work.

<sup>&</sup>lt;sup>1</sup>C. Goldmann, C. Krellner, K. P. Pernstich, S. Haas, D. J. Gundlach, and B. Batlogg, J. Appl. Phys. 99, 034507 (2006).

<sup>&</sup>lt;sup>2</sup>A. Salleo, F. Endicott, and R. A. Street, Appl. Phys. Lett. **86**, 263505 (2005).

<sup>&</sup>lt;sup>3</sup>D. Knipp, R. A. Street, A. Völkel, and J. Ho, J. Appl. Phys. 93, 347 (2003).

<sup>4</sup>S. J. Zilker, C. Detcheverry, E. Cantatore, and D. M. de Leeuw, Appl. Phys. Lett. 79, 1124 (2001).

<sup>&</sup>lt;sup>5</sup>D. Kumaki, T. Umeda, and S. Tokito, Appl. Phys. Lett. **92**, 093309 (2008).

<sup>6</sup>M. J. Powell, C. van Berkel, I. D. French, and D. H. Nichols, Appl. Phys. Lett. **51**, 1242–1244 (1987).

<sup>&</sup>lt;sup>7</sup>D. L. Staebler and C. R. Wronski, Appl. Phys. Lett. **31**, 292–294 (1977).

<sup>&</sup>lt;sup>8</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature (London) 432, 488 (2004).

<sup>&</sup>lt;sup>9</sup>J. K. Jeong, J. H. Jeong, H. W. Yang, J. Park, Y. Mo, and H. D. Kim, Appl. Phys. Lett. **91**, 113505 (2007).

<sup>&</sup>lt;sup>10</sup>W. S. Kim, Y. K. Moon, K. T. Kim, S. Y. Shin, B. D. Ahn, J. H. Lee, and J. W. Park, Thin Solid Films **519**, 6849–6854 (2011).

<sup>&</sup>lt;sup>11</sup> A. L. Salas-Villasenor, I. Mejia, J. Hovarth, H. N. Alshareef, D. K. Cha, R. Ramirez-Bon, B. E. Gnade, and M. A. Quevedo-Lopez, Electrochem. Solid-State Lett. 13, H313–H316 (2010).

<sup>&</sup>lt;sup>12</sup>I. Mejia, A. L. Salas-Villasenor, A. Avendano-Bolivar, J. Horvath, H. Stiegler, B. E. Gnade, and M. A. Quevedo-Lopez, IEEE Electron Device Lett. 32, 1086 (2011).

<sup>&</sup>lt;sup>13</sup>G. Horowitz and M. E. Hajlaoui, Synth. Met. **122**, 185 (2001)

<sup>&</sup>lt;sup>14</sup>C. Kim, A. Facchetti, and T. J. Marks, Science 318, 76 (2007).

- <sup>15</sup>D. Guo, S. Entania, S. Ikedaa, and K. Saiki, Chem. Phys. Lett. 429, 124

- <sup>16</sup>C. D. Gutierrez-Lazos, E. Rosendo, A. I. Oliva, M. Ortega, P. Bartolo-Perez, H. Juarez, T. Diaz, G. Garcia, and M. Rubin, Thin Solid Films 518, 5387-5390 (2010).

- <sup>17</sup>M. Weis, K. Gmucova, V. Nadazdy, E. Majkova, D. Hasko, D. Taguchi, T. Manaka, and M. Iwamoto, Jpn. J. Appl. Phys., Part 1 50, 04DK03 (2011).

- <sup>18</sup>S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. (Wiley, New York, 1981).

- <sup>19</sup>D. J. Gundlach, K. P. Pernstich, G. Wilckens, M. Gruter, S. Haas, and B. Batlogg, J. Appl. Phys. **98**, 064502 (2005).

<sup>20</sup>A. G. Ismail and I. G. Hill, Org. Electron. **12**, 1033–1042 (2011).

- <sup>21</sup>B. Malinowska, M. Rakib, and G. Durand, Sol. Energy Mater. Sol. Cells 86, 399 (2005).

- <sup>22</sup>A. Kylner and M. Wirde, Jpn. J. Appl. Phys., Part 1 **36**, 2167–2175 (1997).

- <sup>23</sup>R. N. Bhattacharya, K. Ramanathan, L. Gedvilas, and B. Keyes, J. Phys. Chem. Solid 66, 1862 (2005).

- <sup>24</sup>W. D. Park, Trans. Electr. Electron. Mater. **11**, 170 (2010).