# CONDITION MONITORING FOR DISCRETE PACKAGED INSULATED GATE BIPOLAR TRANSISTORS IN POWER CONVERTERS

by

Syed Huzaif Ali

# APPROVED BY SUPERVISORY COMMITTEE:

| Dr. Bilal Akin, Chair   |  |

|-------------------------|--|

|                         |  |

|                         |  |

| Dr. Mehrdad Nourani     |  |

| Di. Weindad Nodram      |  |

|                         |  |

|                         |  |

| Dr. Ghanshyamsinh Gohil |  |

|                         |  |

|                         |  |

| Dr. Hoi Lee             |  |

| 21, 1101 200            |  |

Copyright 2018

Syed Huzaif Ali

All Rights Reserved

# CONDITION MONITORING FOR DISCRETE PACKAGED INSULATED GATE BIPOLAR TRANSISTORS IN POWER CONVERTERS

by

SYED HUZAIF ALI, BE, MS

# **DISSERTATION**

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT DALLAS

August 2018

#### ACKNOWLEDGMENTS

I am indebted to my advisor, Dr. Bilal Akin, who provided me encouragement and support throughout the course of my PhD studies. During my study, his technical comments provided me with necessary guidance. I consider myself to be privileged for my successful PhD completion under his supervision.

I would like to thank Dr. Mehrdad Nourani, Dr. Ghanshyamsinh Gohil, and Dr. Hoi Lee for their support as well as for serving as my dissertation committee members. Truly, without their valuable comments, and suggestions I could not have completed my dissertation.

I would like to further thank all the administrative assistants of the electrical engineering department. I am also thankful to my colleagues, particularly, Mr. Enes Ugur, Mr. Kudra Baruti, and Mr. Fei Yang, for their contributions to this project. I am also highly indebted to Dr. Serkan Dusmez from Texas Instruments for his tremendous support and encouragement at every step while we worked together in the same laboratory. I would like to express my appreciation to Mr. Anant Kamath from Texas Instruments for his valuable guidance. I also thank Priority Labs for their failure and acoustic analysis reports.

I would also like to express my deepest gratitude to my family. All of my achievements are the beautiful result of their immense support and love.

This work has been supported by the TXACE/SRC under Grant TASK 1836.154.

July 2018

CONDITION MONITORING FOR DISCRETE PACKAGED INSULATED GATE BIPOLAR

TRANSISTORS IN POWER CONVERTERS

Sved Huzaif Ali, PhD

The University of Texas at Dallas, 2018

Supervising Professor: Dr. Bilal Akin

Extensive utilization of insulated gate bipolar transistor (IGBTs) in the power converters has

significantly increased concerns over its reliability. Failure of such critical component eventually

cause unexpected shut downs and even lead to catastrophic faults resulting in huge economic

loss. So, tools for incipient fault diagnosis and aging prognosis have to be utilized for reducing

the risk of faults and accidents. Yet, established tools are not mature enough and there exist a

major reliability gap exist in condition monitoring of IGBTs. In order to improve current

prognostic and diagnostic tools, this dissertation investigates ongoing aging induced degradation

and corresponding shifts in electrical parameters for IGBTs. Such useful electrical parameters

are referred as aging precursors which are obtained after extensive thermal aging tests. Based on

the aging test results, aging precursors are identified and an in-situ condition monitoring circuit

has been proposed as well. Due to low component count, the proposed circuit is cost effective

and can be easily integrated to conventional gate driver circuits. Based on the data

measurements, further remaining useful lifetime estimation for IGBTs have been carried out as

well. It is conceived that such tools lay foundations for smart-energy conversion systems which

vi

are self-capable in evaluating the degradation information using aging precursors to prevent imminent failures in the system. Briefly, this dissertation discusses:

- o identification and characterization of aging precursors,

- o development of innovate and easy-to-integrate condition monitoring circuit

- development of remaining useful lifetime estimation tool based on the monitored data for advancing smart power conversion systems.

# TABLE OF CONTENTS

| v  |

|----|

| vi |

| xi |

| xv |

| 1  |

| 1  |

| 1  |

| 3  |

| 4  |

| 5  |

| 7  |

| 7  |

| 9  |

| 9  |

| 10 |

| 12 |

| 13 |

| 16 |

| 18 |

| 20 |

| 27 |

| 27 |

|    |

|          |     | 3.1.1 Aging Test Setup Overview                                                             | 28 |

|----------|-----|---------------------------------------------------------------------------------------------|----|

|          |     | 3.1.2 Temperature Control                                                                   | 31 |

|          |     | 3.1.3 Upper T <sub>j</sub> Limit for Highly Accelerated Aging Test                          | 32 |

|          |     | 3.1.4 Test Procedure for Parametric Device Characterization                                 | 33 |

| ,        | 3.2 | Parametric i-V Characterization                                                             | 34 |

|          |     | 3.2.1 Failure Analysis                                                                      | 39 |

| <i>.</i> | 3.3 | V <sub>th</sub> and V <sub>ce,on</sub> Characterization at Different Thermal Stress Levels  | 41 |

|          |     | 3.3.1 Scheme # 1                                                                            | 44 |

|          |     | 3.3.2 Scheme # 2                                                                            | 49 |

| <i>.</i> | 3.4 | Challenges of $V_{\text{ce,on}}$ and Benefits of Using $V_{\text{th}}$ as Failure Precursor | 55 |

| <i>.</i> | 3.5 | Conclusion                                                                                  | 58 |

|          |     | ER 4 CONDITION MONITORING CIRCUIT BASED ON IDENTIFIED A                                     |    |

| 2        | 4.1 | Background                                                                                  | 59 |

| 2        | 4.2 | Brief Discussion on Identified Failure Precursors                                           | 62 |

| 2        | 4.3 | Issues in Measurement of $V_{th}$ and $V_{ce,on}$ Measurements                              | 65 |

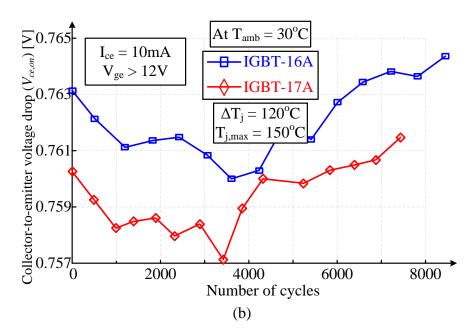

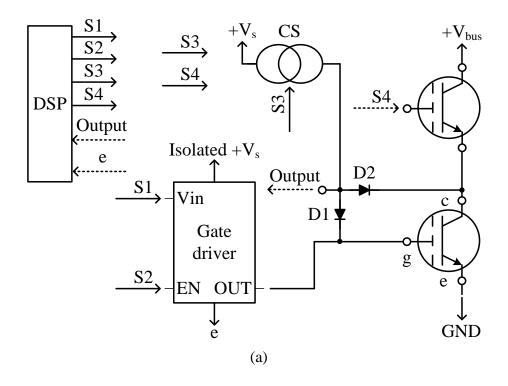

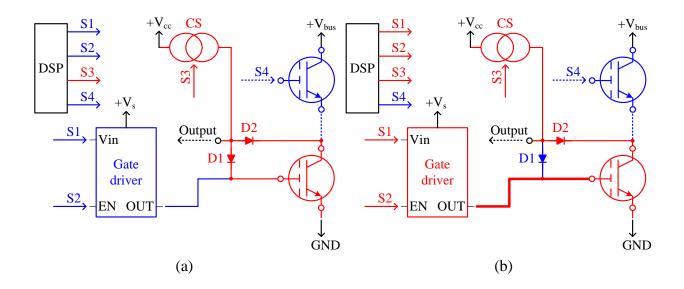

| 2        | 4.4 | Proposed Circuit Description                                                                | 68 |

|          |     | 4.4.1 V <sub>th</sub> Measurement Mode                                                      | 70 |

|          |     | 4.4.2 V <sub>ce,on</sub> Measurement Mode                                                   | 71 |

|          |     | 4.4.3 Normal Operation                                                                      | 71 |

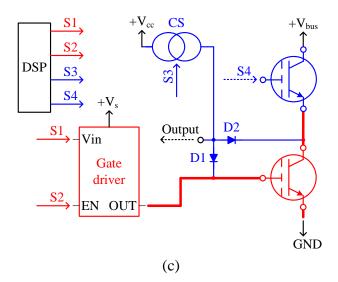

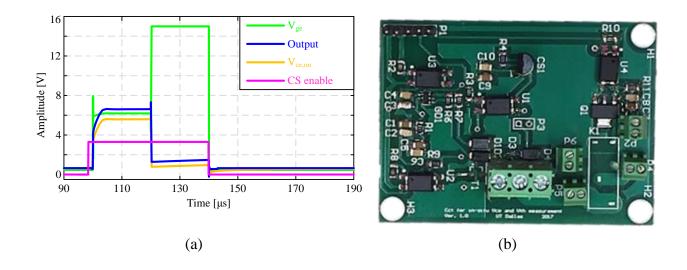

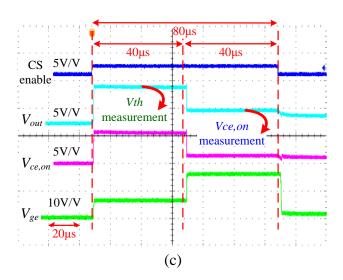

| 2        | 4.5 | Discussion on Results from Proposed Circuit                                                 | 71 |

| 2        | 4.6 | Conclusion                                                                                  | 76 |

| СНА      | PTE | ER 5 REMAINING USEFUL LIFETIME ESTIMATION                                                   | 78 |

|          | 5.1 | Motivation                                                                                  | 78 |

| 5.2    | Accelerated Aging Test Procedure and Results for PT, NPT and TGFS                          |

|--------|--------------------------------------------------------------------------------------------|

| 5.3    | Test Results at Reduced Temperature Levels                                                 |

| 5.4    | Challenges in Modelling IGBT Lifetime using Estimated $T_j$ and Proposed Approach 86       |

| 5.5    | Generic Behavior of IGBT under Thermal Stress and IGBT's Lifetime Estimation 88            |

| 5.6    | Remaining Useful Lifetime Prediction Based on V <sub>ce,on</sub> using Gaussian Process 91 |

| 5.7    | Conclusion                                                                                 |

| СНАРТІ | ER 6 SUMMARY                                                                               |

| REFERE | NCES                                                                                       |

| BIOGRA | PHICAL SKETCH111                                                                           |

| CURRIC | CULUM VITAE                                                                                |

# LIST OF FIGURES

| 1.1.  | Percentage distribution of reported sub-system failure events in PV systems                                                                                                  | 2  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2.  | Industry wide survey regarding reliability concerns in power converters; (a) distribution of failure prone components and (b) share of different power semiconductor devices |    |

| 1.3.  | Sources of stress for power electronic systems                                                                                                                               | 3  |

| 1.4.  | Proposed fault and aging detection system.                                                                                                                                   | 4  |

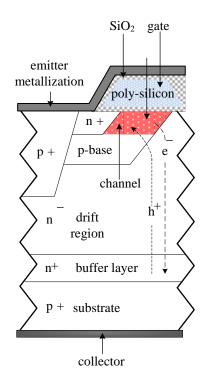

| 2.1.  | Structure for PT IGBT.                                                                                                                                                       | 10 |

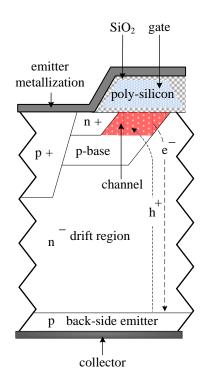

| 2.2.  | Structure for NPT IGBT.                                                                                                                                                      | 11 |

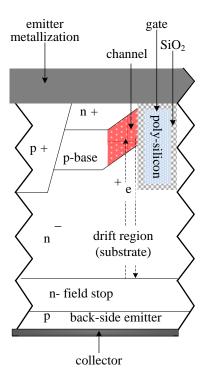

| 2.3.  | Structure for TGFS IGBT.                                                                                                                                                     | 12 |

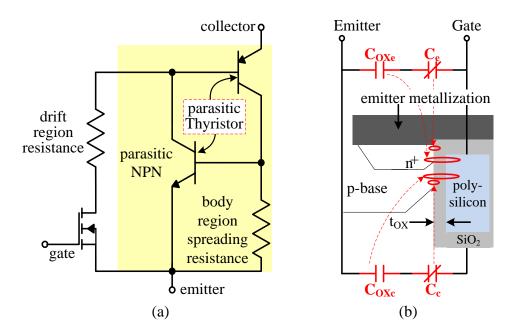

| 2.4.  | Simplified circuit model for (a) MOSFET-BJT equivalent circuit and (b) gate-or capacitances.                                                                                 |    |

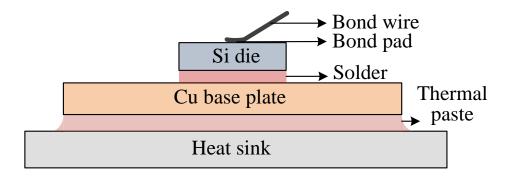

| 2.5.  | Typical discrete package structure of an IGBT.                                                                                                                               | 17 |

| 2.6.  | Steps of gate-oxide degradation.                                                                                                                                             | 19 |

| 2.7.  | Bond wire lift-off different IGBT samples; (a) Lift-off after power cycling test (b) magnified image of another sample showing lift-off pattern                              |    |

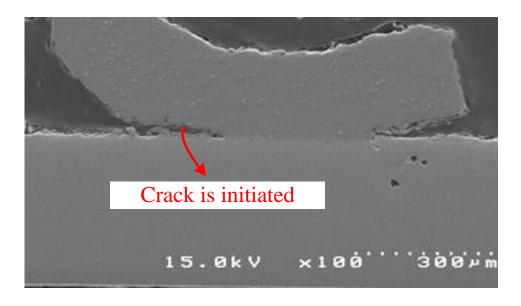

| 2.8.  | Cross-sectional image of crack initiation in the bond wire                                                                                                                   | 22 |

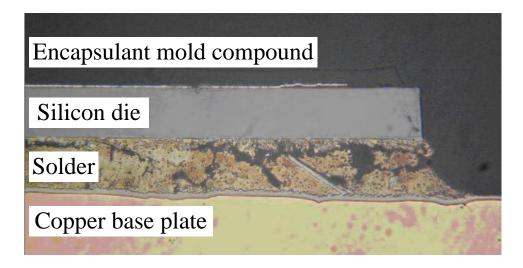

| 2.9.  | Large voids and crack in the die-attach solder layer                                                                                                                         | 24 |

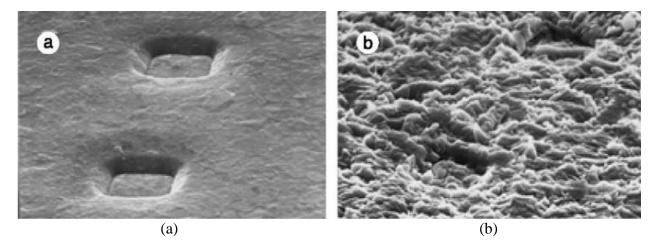

| 2.10. | Aluminum grain boundary reconstruction (a) before power cycling and (b) after pocycling                                                                                      |    |

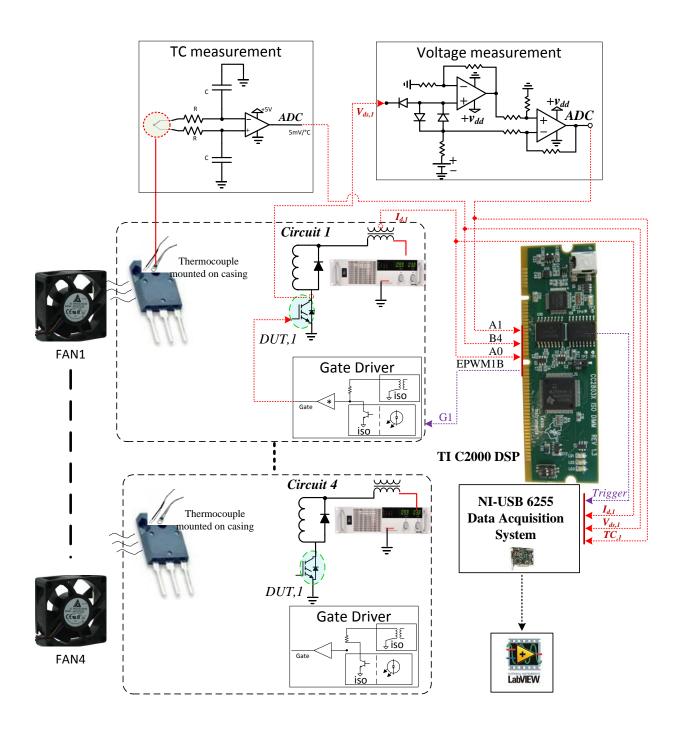

| 3.1.  | Circuit schematic for designed aging testbed for IGBTs.                                                                                                                      | 29 |

| 3.2.  | Actual photograph of designed aging testbed for IGBTs along with the curve tracer                                                                                            | 31 |

| 3.3.  | Variation in breakdown voltage with respect to aging.                                                                                                                        | 35 |

| 3.4.  | Variation in gate leakage current with respect to aging                                                                                                                      | 35 |

| 3.5.  | Variation in gate resistance with respect to aging                                                                                                                           | 36 |

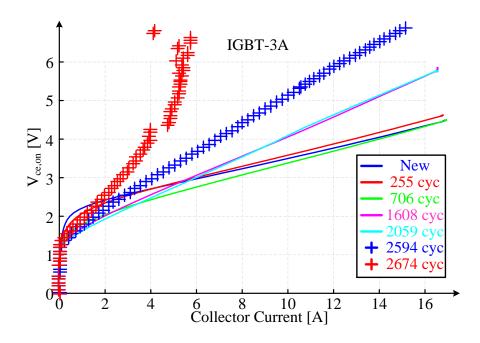

| 3.6.  | Variation in on-state collector-emitter voltage drop at different collector current with respect to aging                                                                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

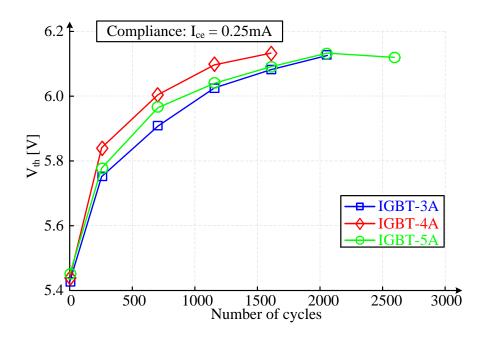

| 3.7.  | Variation in gate threshold voltage with respect to aging                                                                                                                                                                                                                                                                                               |

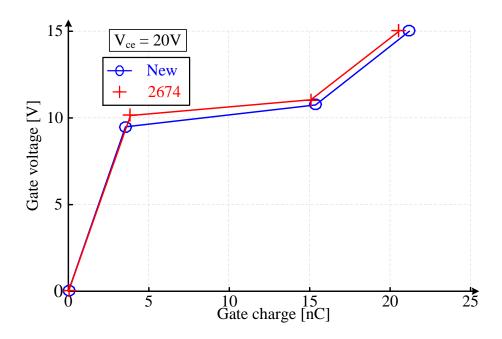

| 3.8.  | Comparison of gate charge at different gate voltages for new (before aging) and aged DUT                                                                                                                                                                                                                                                                |

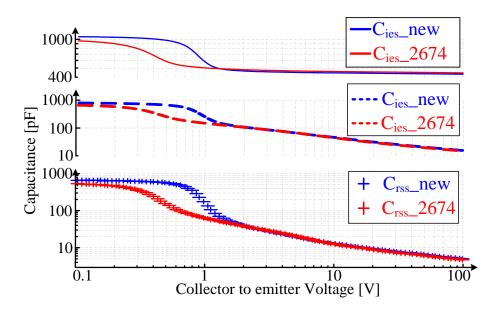

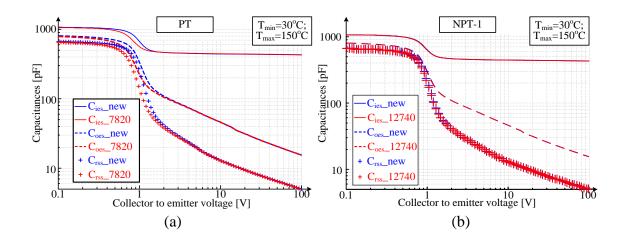

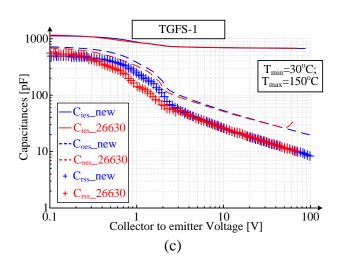

| 3.9.  | Comparison of parasitic capacitance at different collector-emitter voltages for new (before aging) and aged DUT                                                                                                                                                                                                                                         |

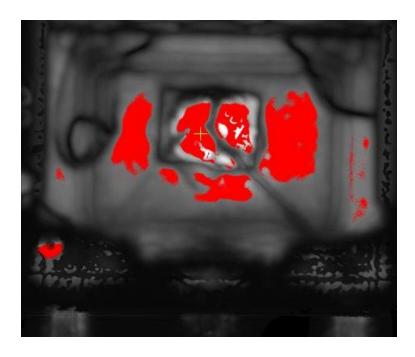

| 3.10. | C-SAM result for failed DUT with red spots indicating large voids in the die-attach layer and no significant bond-wire issues                                                                                                                                                                                                                           |

| 3.11. | T-SAM result for failed DUT with dark spot obscuring die showing significant delamination in the package at multiple layers                                                                                                                                                                                                                             |

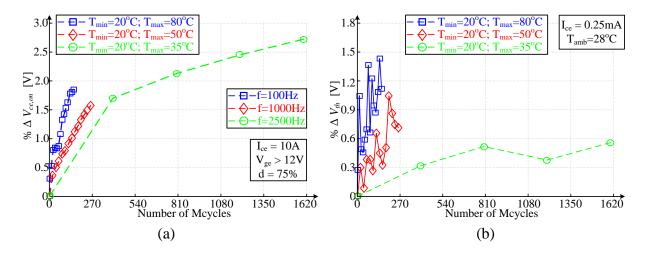

| 3.12. | Scheme # 1 aging test results for PT (maximum $T_j < 80^{\circ}$ C); (a) $V_{ce,on}$ measurements at $I_{ce} = 5$ A and (b) $V_{th}$ measurements at $I_{ce} = 0.25$ mA. Note: Mcycles = million cycles45                                                                                                                                               |

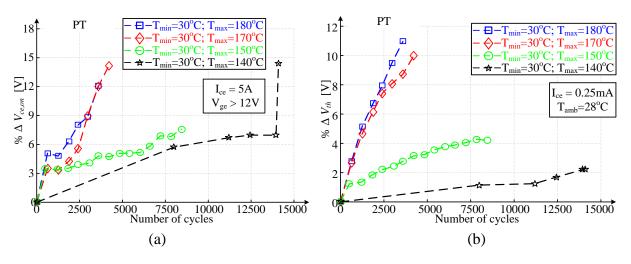

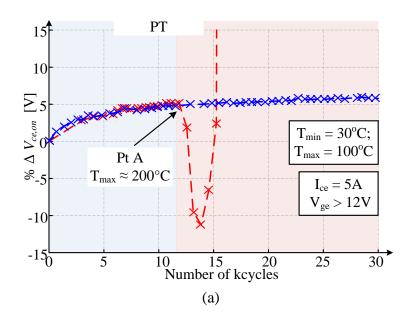

| 3.13. | Scheme # 1 aging test results for PT (maximum $T_j < 180^{\circ}$ C); (a) $V_{ce,on}$ measurements at $I_{ce} = 5$ A and (b) $V_{th}$ measurements at $I_{ce} = 0.25$ mA                                                                                                                                                                                |

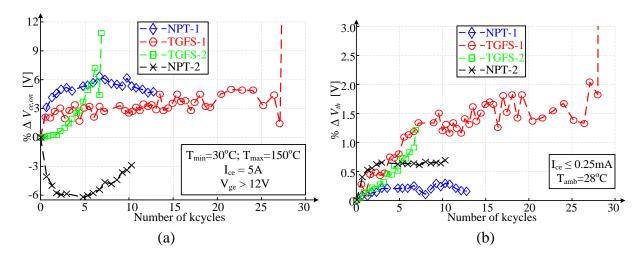

| 3.14. | Scheme # 1 aging test results for NPT and TGFS (maximum $T_j = 150$ °C); (a) $V_{ce,on}$ measurements at $I_{ce} = 5$ A and (b) $V_{th}$ measurements at $I_{ce} = 0.25$ mA                                                                                                                                                                             |

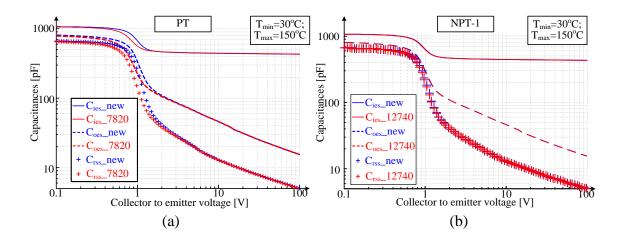

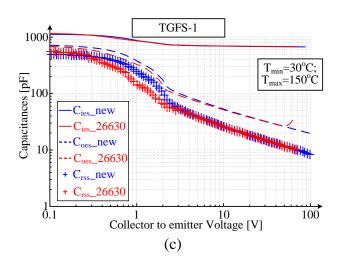

| 3.15. | Scheme # 1 comparison of new and aged parasitic capacitances at f=1MHz for; (a) PT, (b) NPT-1 and (b) TGFS-147                                                                                                                                                                                                                                          |

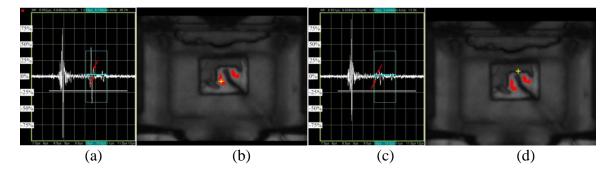

| 3.16. | After aging CSAM results for one PT DUT from Scheme # 1; (a) frequency response over die adjacent to bondpad, (b) its CSAM image with red spots showing delamination around bondpad, (c) frequency response over possible delamination site in mold compound and (d) its corresponding CSAM image with dark spots showing delamination at mold compound |

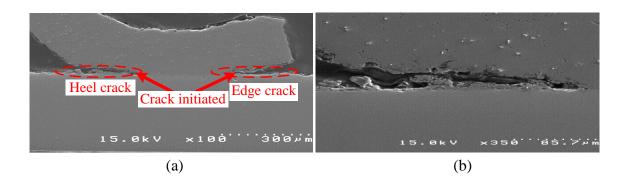

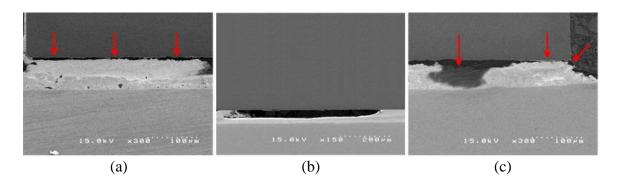

| 3.17. | Bond-wire to die cross-section examination snapshot; (a) complete bond pad snapshot, (b) zoomed-in at heel crack snapshot and (c) zoomed-in at bond-wire edge crack48                                                                                                                                                                                   |

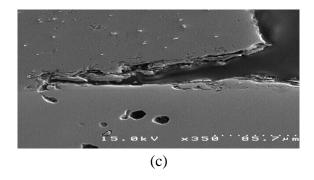

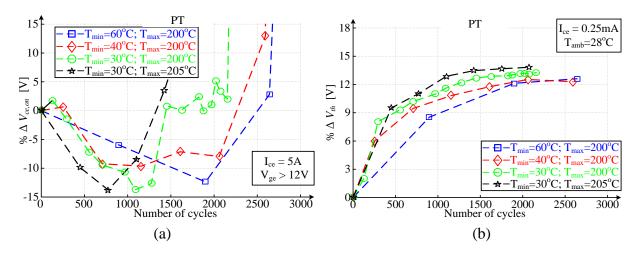

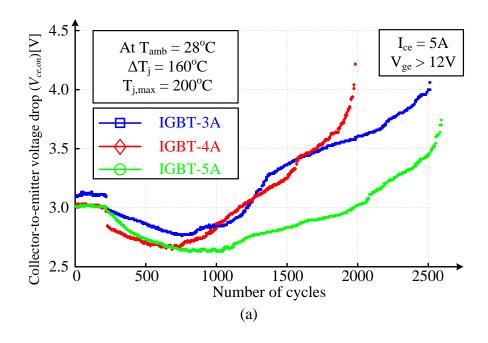

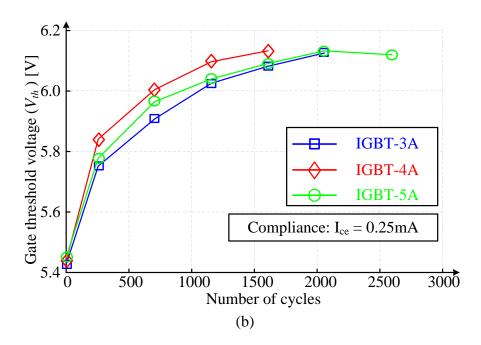

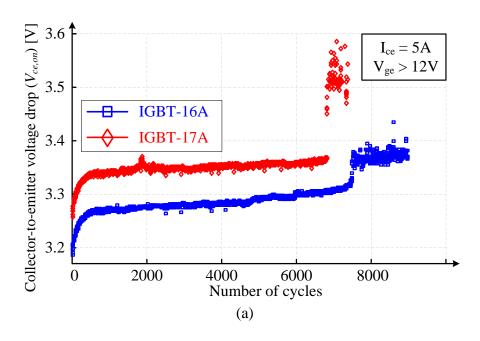

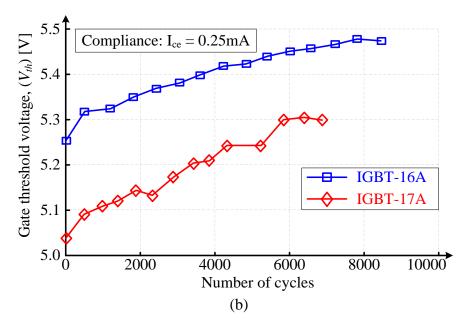

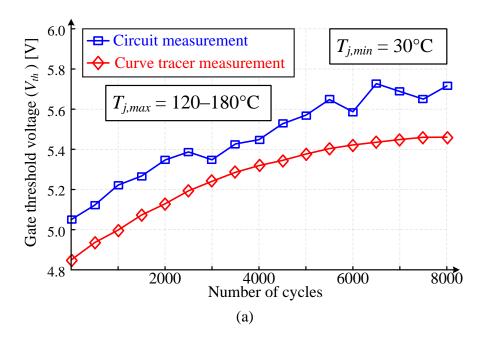

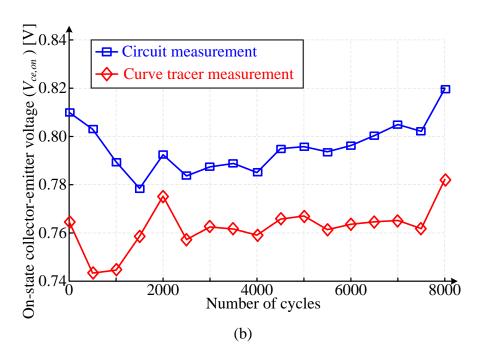

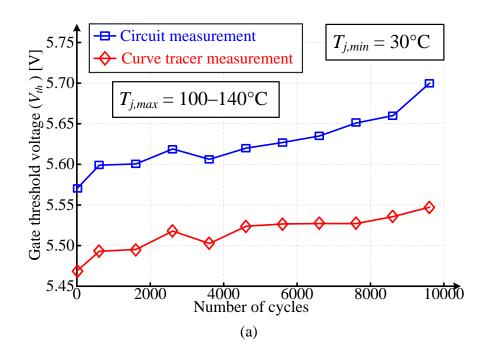

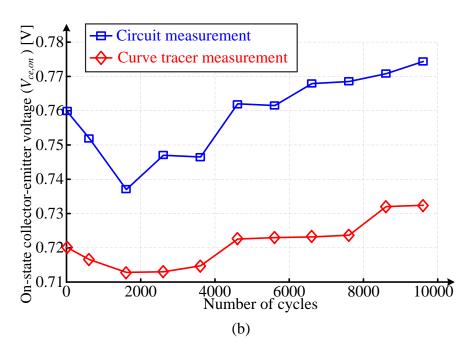

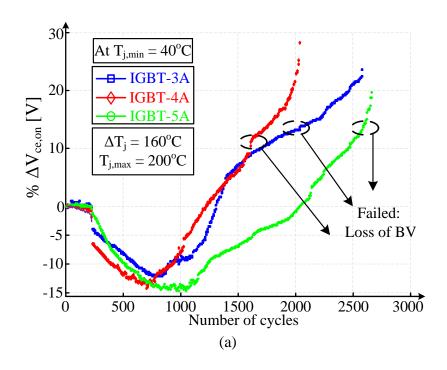

| 3.18. | Scheme # 2 aging test results for PT; (a) $V_{ce,on}$ measurements at $I_{ce} = 5$ A and (b) $V_{th}$ measurements at $I_{ce} = 0.25$ mA                                                                                                                                                                                                                |

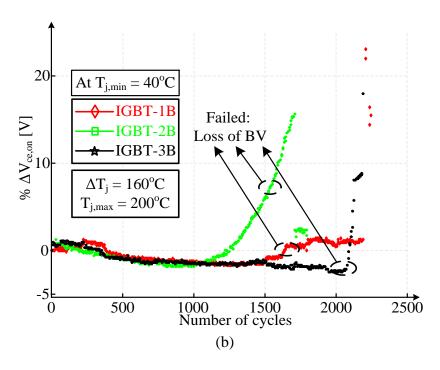

| 3.19. | Scheme # 2 aging test results for NPT and TGFS; (a) $V_{ce,on}$ measurements at $I_{ce} = 5$ A and (b) $V_{th}$ measurements at $I_{ce} = 0.25$ mA50                                                                                                                                                                                                    |

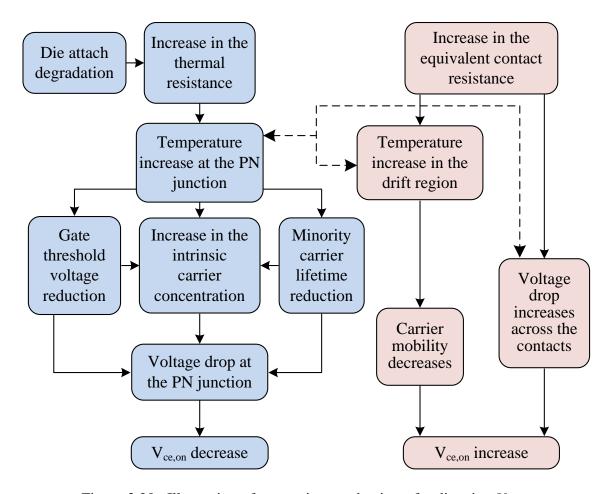

| 3.20. | Illustration of competing mechanisms for dictating $V_{ce,on}$                                                                                                                                                                                                                                                                                          |

| 3.21. | Scheme # 2 comparison of new and aged parasitic capacitances at f=1MHz for; (a) PT, (b) NPT-1 and (b) TGFS-1                                                                    |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3.22. | SAM results for one PT DUT; (a) damped acoustic frequency response for CSAM, (b) CSAM snapshot for DUT and (c) TSAM snapshot for DUT54                                          |  |  |

| 3.23. | Solder die-attach layer cross-sectioning images; (a) Left edge delamination, (b) central void and (c) right edge delamination                                                   |  |  |

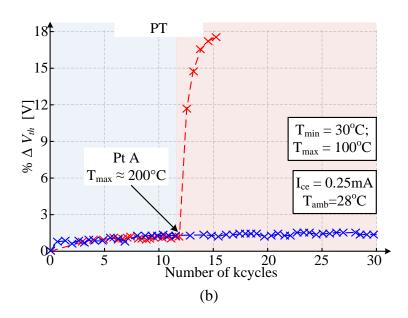

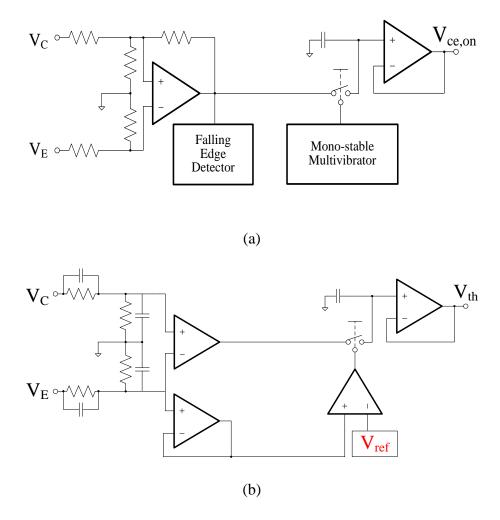

| 3.24. | Test emulating failure in cooling sub-system; (a) $V_{ce,on}$ measurements at $I_{ce} = 5$ A and (b) $V_{th}$ measurements at $I_{ce} = 0.25$ mA.                               |  |  |

| 4.1.  | Simplified circuit schematic proposed in [66] for monitoring; (a) $V_{ce,on}$ and (b) $V_{th}$ 61                                                                               |  |  |

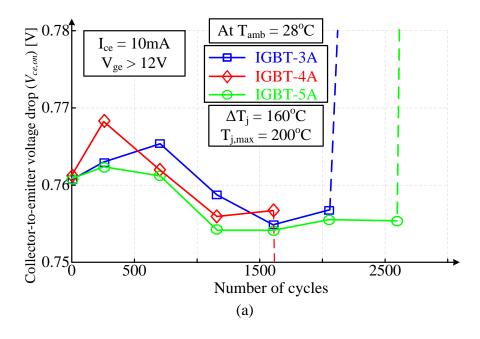

| 4.2.  | Induced thermo-electric stress aging test results for above thermal SOA limit; (a) $V_{ce,or}$ and (b) $V_{th}$                                                                 |  |  |

| 4.3.  | Induced thermo-electric stress aging test results for below thermal SOA limit; (a) $V_{ce,or}$ and (b) $V_{th}$                                                                 |  |  |

| 4.4.  | $V_{ce,on}$ measurements at $I_{ce}$ =10mA (a) above SOA thermal limit (b) below SOA thermal limit                                                                              |  |  |

| 4.5.  | Proposed circuit; (a) schematic, (b) timing diagram for control signals,69                                                                                                      |  |  |

| 4.6.  | Illustration of operation for proposed circuit; (a) $V_{th}$ measurement mode, (b) $V_{ce,or}$ measurement mode and (c) normal gate driver operation                            |  |  |

| 4.7.  | Results of prototype circuit; (a) simulation, (b) actual prototype snapshot containing both the gate driver and aging circuit, (c) oscilloscope waveforms for new IGBT sample72 |  |  |

| 4.8.  | Comparative results between proposed circuit and curve tracer for above SOA case; (a) $V_{th}$ and (b) $V_{ce,on}$                                                              |  |  |

| 4.9.  | Comparative results between proposed circuit and curve tracer for below SOA case; (a) $V_{th}$ and (b) $V_{ce,on}$                                                              |  |  |

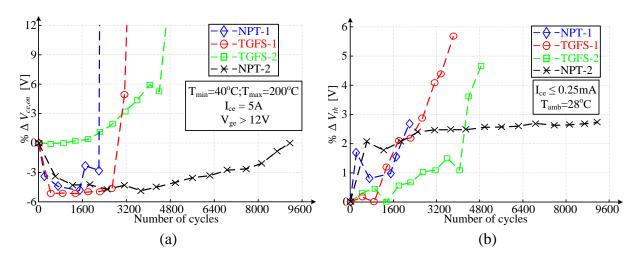

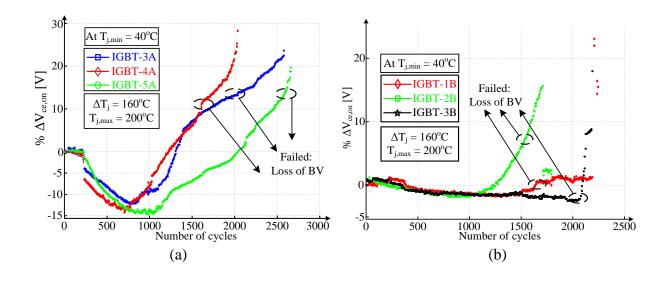

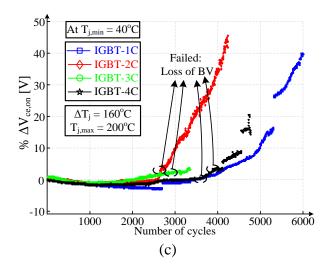

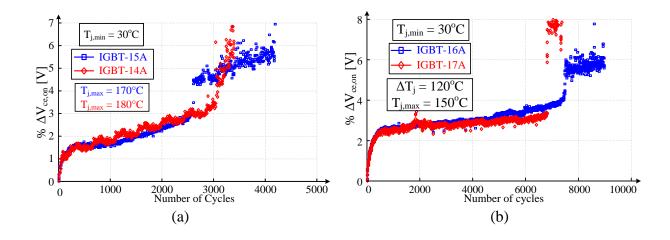

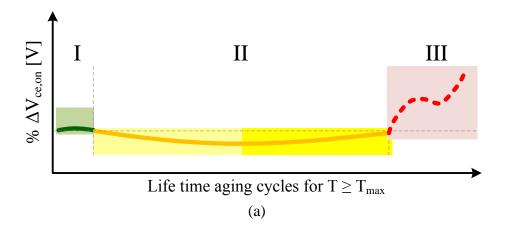

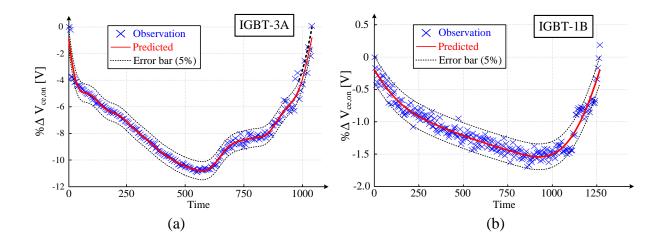

| 5.1.  | $\%\Delta V_{ce,on}$ drop measurement for; (a) A-series, (b) B-series and (c) C-series                                                                                          |  |  |

| 5.2.  | % $\Delta V_{ce,on}$ measurement for extended A- series device samples at a) $\Delta T_j$ =140°C and (b) $\Delta T_j$ =205°C84                                                  |  |  |

| 5.3.  | % $\Delta V_{ce,on}$ for PT IGBT at reduced maximum temperature limits; a) $T_{j,max}$ =180°C, (b) $T_{j,max}$ =150°C and (c) $T_{j,max}$ =140°C.                               |  |  |

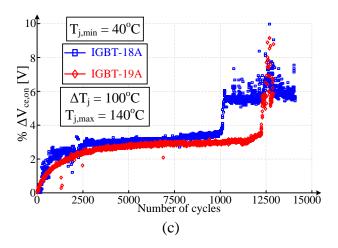

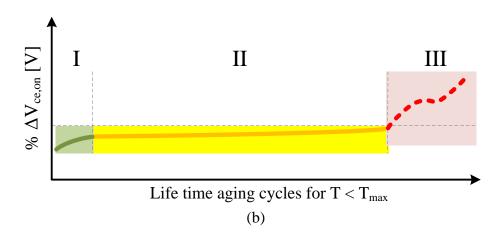

| 5.4. | Generic variations in $\%\Delta V_{ce,on}$ during IGBT lifetime; for (a) T $\geq$ T <sub>j,max</sub> = 200°C and (b) for T $<$ T <sub>j,max</sub> = 200°C89                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

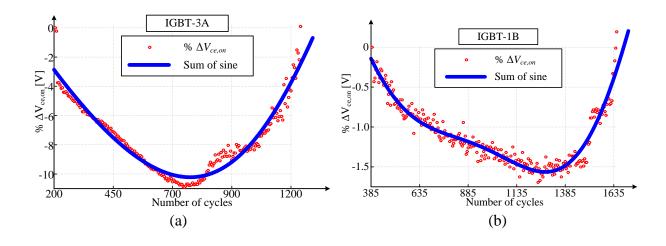

| 5.5. | Empirical model using sinusoidal functions; a) IGBT-3A, (b) IGBT-1B and (c) IGBT-2C91                                                                                                               |

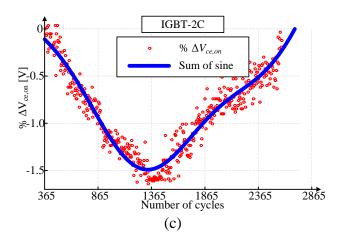

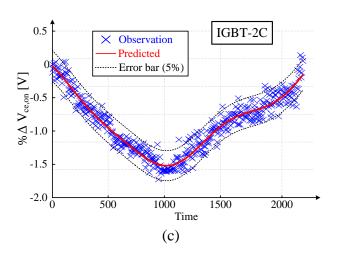

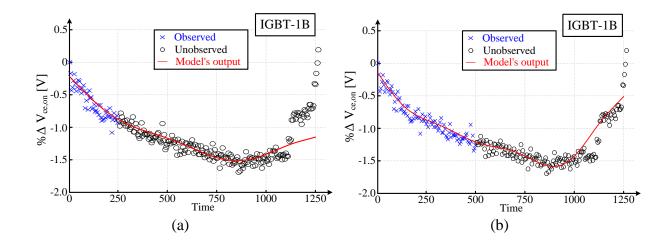

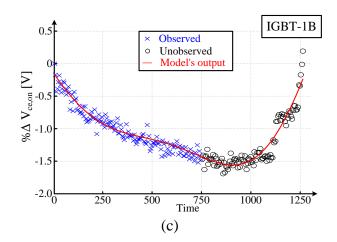

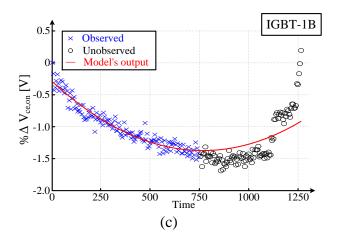

| 5.6. | GPR based curve fitting with square exponential covariance kernel using all training data samples and no prior knowledge for: (a) IGBT-3A, (b) IGBT-1B and (c) IGBT-2C95                            |

| 5.7. | GPR based curve fitting with square exponential covariance kernel using all training data samples and no prior knowledge for: (a) IGBT-3A, (b) IGBT-1B and (c) IGBT-2C96                            |

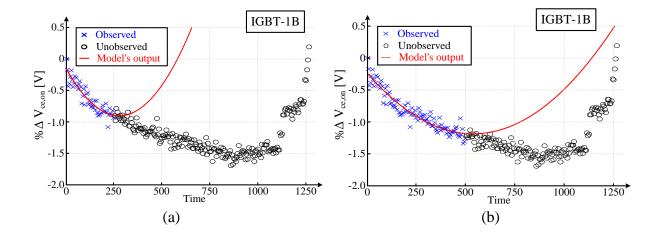

| 5.8. | A polynomial model has been used to fil $\%\Delta V_{ce,on}$ using the ML estimator after observing: (a) 50 points, (b) 100 points and (c) 150 points                                               |

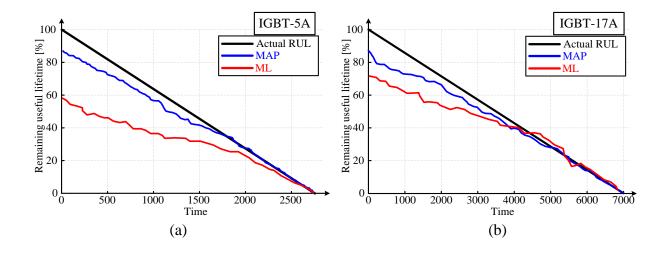

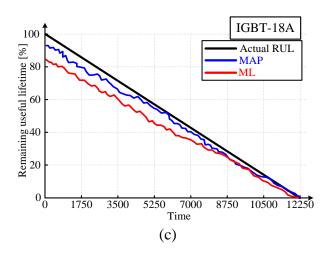

| 5.9. | Absolute % error in RUL estimation stated for three different devices using GPR with prior knowledge (MAP estimator) and without prior knowledge (ML) for (a) IGBT-5A (b) IGBT-17A and (c) IGBT-18A |

# LIST OF TABLES

| 2.1. | General comparison table for few power semiconductor devices.                                            | 9  |

|------|----------------------------------------------------------------------------------------------------------|----|

| 2.2. | IGBT device technologies comparison.                                                                     | 13 |

| 2.3. | Sources of stress for common package related failures.                                                   | 20 |

| 3.1. | Summary of device condition after failure for first set of devices.                                      | 34 |

| 3.2. | Summary of applied thermal stress testing schemes.                                                       | 43 |

| 3.3. | General EoL behavior for DUTs classified w.r.t. to tested scheme                                         | 44 |

| 5.1. | DUTs condition after cycling at $\Delta T_j = 160^{\circ}\text{C}$ ( $T_{j,max} = 200^{\circ}\text{C}$ ) | 81 |

| 5.2. | DUTs condition after cycling at at different $\Delta T_j$ .                                              | 83 |

| 5.3. | Summary of device failures at low thermal swings.                                                        | 86 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation

Today, the growing demands of energy consumption require efficient and reliable sources of energy delivery and power conversion. In this connection, most modern power electronic converters utilize efficient active and passive components, pioneering circuit design techniques and sophisticated system integration methods. Yet, with high degree of dependence on power converters for energy conversion in our daily lives, their reliability is a major concern.

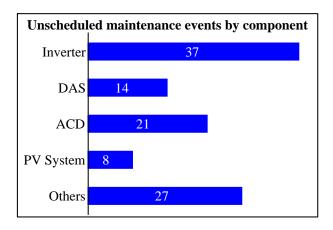

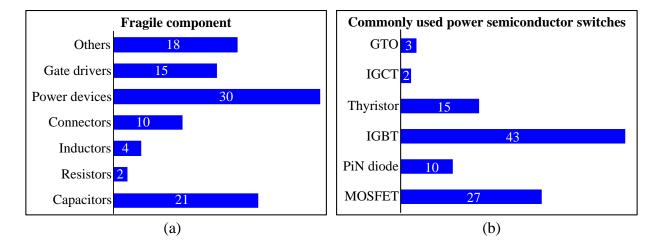

Considering the example of renewable energy based power generation systems, five years of maintenance data for different installed PV systems has been presented in [1]. Based on the data, it has been highlighted that inverters are the most failing sub-system beside data acquisition systems (DASs), ac disconnects (ACDs), PV system and other components as shown in Figure 1.1. In a separate power electronics industry wide survey, it has been concluded that power switching devices are one of most frequently failing components in power converters behind capacitors as shown in Figure 1.2 (a) [2]. Understandably, as their operation could cease without the switching devices, early failure and aging discovery in switching devices is crucial for their reliable operation for incessant power delivery.

# 1.2 Background

Predominantly, insulated gate bipolar transistors (IGBTs) are the most widely used switching devices for low and medium power level power converters in renewable energy systems, hybrid electric vehicles and industrial motor drives etc. as shown in Figure 1.2 (b) [2]. During

Figure 1.1. Percentage distribution of reported sub-system failure events in PV systems.

Figure 1.2. Industry wide survey regarding reliability concerns in power converters; (a) distribution of failure prone components and (b) share of different power semiconductor devices.

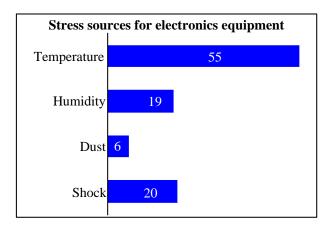

operational life, IGBTs may undergo severe on-field stresses triggering different aging mechanisms which can lead to catastrophic failures. Among different stress types, high cyclic temperature has been shown as the highest contributor to device aging in Figure 1.3 [3].

Figure 1.3. Sources of stress for power electronic systems.

Several reliability studies have been performed and different statistical models have been presented for analyzing device aging as well. Yet, operational conditions are often unpredictable and comprehensive testing for different scenarios is required to improve statistical models for estimating aging and imminent failures in devices. Furthermore, high degree of variability in device specification also exists among different batches so, lot of effort is required to test and estimate failure time for different applications.

## 1.3 Problem Description

Today, IGBT is considered to the industry's workhorse for switching power. At the same time, it is prone to high degree of wear and aging within the power converters as it suffers from induced thermomechanical and electrical stress during its operation. Its rapid utilization has raised significant reliability concerns due to operational uncertainties and limited on-field data. Modern advanced controllers which monitor variety of power converters' electrical signals for control purposes but these controllers significantly lack in gathering reliability information about the

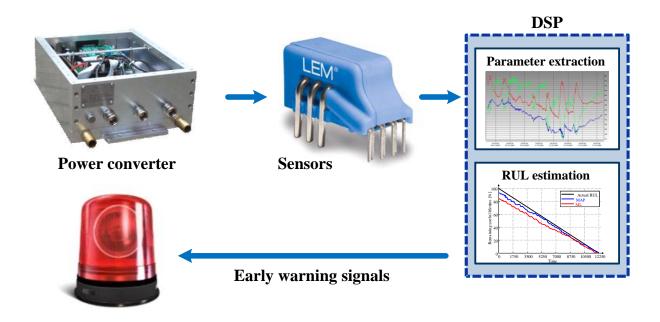

Figure 1.4. Proposed fault and aging detection system.

installed components particularly, IGBTs. The current state-of-art includes redundancy to avoid catastrophic failures and/ or protect the system after the failure. In order to move forward, a fault and aging detection system is needed which can monitor device aging, estimate its remaining useful lifetime (RUL) in the real-time based on prior aging test data for real-life operating conditions. The same has been illustrated in the Figure 1.4.

## 1.4 Aims and Objectives

The main objectives of this study have been summarized as following:

- To characterize electrical parameters using accelerated aging test beds at cyclic thermal stress to determine aging signatures or aging precursors.

- O To develop on-line aging precursor monitoring tools for examining state-of-health of IGBTs within the power converters.

To devise data driven approach for estimating the RUL of IGBTs based on the observed on-field aging precursors' information

#### 1.5 Outline of the Dissertation

The chapter wise outline is given below:

- In Chapter 2, structural details for different types of discrete package IGBTs have been introduced. Also, the extrinsic, intrinsic failures and the associated aging mechanisms discussed in the literature are reviewed. Moreover, details for accelerated aging test setup are introduced and *i-V* characteristics results from aging test at variety of stress levels are presented. Furthermore, the underlying physical phenomena responsible for the parametric variations with respect to aging are investigated in the light of scanning acoustic microscope (SAM) analysis results.

- In Chapter 3, condition monitoring tools are introduced. A brief literature review about existing methods is presented as well. Based on the shortcomings in the existing methods, a novel circuit is presented. The proposed circuit is not only cost-effective but provides fast aging precursors monitoring in the order of microseconds and occupies small real estate on the printed circuit board (PCB). Furthermore, simulation and experimental results are presented as well to corroborate the efficacy of the proposed circuit.

- O In Chapter 4, a data driven RUL estimation model based on Gaussian Process Regression (GPR) is presented. The model uses the IGBT's actual aging information instead of relying on junction temperature for RUL estimation. It takes the observed aging precursor information and estimates the RUL of aging sample device. It is shown through results

that by training the model using the aging test results from chapter 2, drastically improves the RUL estimation results compared to conventional algorithms.

o In Chapter 5, the summary of the dissertation is presented.

#### **CHAPTER 2**

#### IGBT DEVICE STRUCTURE AND AGING MECHANISMS

## 2.1 Power Semiconductor Revolution and IGBT

Since 1950, pnpn stacked layer silicon controlled rectifiers dominated the power electronics industry. Among the SCR family, Thyristor has been the most famous one. Although, Thyristor can provide both high voltage blocking (in kV) and high current conduction (in kA) capability but require additional control/ power circuit for its current commutation which restricts its widespread deployment. To some extent power bipolar junction transistor (BJT) for low voltage applications serve as good alternative but its high gate current driving requirements degrades the overall efficiency. Moreover, in order to sustain high blocking voltage (BV), BJT have been fabricated with low intrinsic gain (ratio of control input and power output).

In 1970's, the introduction of vertical power metal oxide silicon field effect transistor (MOSFET) ushered a new era in power electronics industry. Power MOSFET unlike the BJT is a majority carrier device and can switch significantly at higher speeds which have could not have been achieved using existing BJT technology. High switching speed limited only by parasitic capacitances enabled realization of various different circuit topologies. Power MOSFETs improved the system efficiencies without compromising the switching speeds only for low voltage applications. In order to sustain higher BV, thicker device need to be fabricated but at the cost of significantly higher conduction loss compare to that of BJT of the same die size. Thus, a newer type of device has been sought which can provide benefits from both devices.

In 1982, Baliga reported a new device named as insulated gate rectifier (IGR) which later became insulated gate bipolar transistor (IGBT) [4]. He combined the insulated gate FET for the input control and power BJT as a HV switch in one single device. IGBT actually filled the gap by providing much needed compromise between BJT and Power MOSFET device characteristics. An IGBT can provide high BV and conductivity modulation just like power BJT at higher power levels as well as require simpler gate drive circuits just like MOSFETs. Moreover, unlike power BJT, it can operate at higher switching frequencies as well.

Today, IGBT structural design, size and performance have improved significantly but still it resembles the same structure proposed by Baliga. Briefly, an IGBT device cell is constructed in a similar fashion as to an n-channel type double diffused vertical construction power MOSFET. The p+ collector layer replaces the n+ drain and is the major exception between the two devices. Thus, a vertical PNP bipolar junction transistor is formed whose base current is controlled by the n-channel FET. The n-channel is further controlled by providing suitable gate-emitter voltage above gate threshold voltage. An IGBT compared to the power MOSFET has

- bipolar device characteristics which means minority carriers are injected in to n-drift region to assist majority carrier transport allowing for higher current densities and require more time during transients (turn-on and turn-off times) and

- characteristic diode-voltage drop which increases logarithmically with respect to its current.

A brief comparison among power BJT, power MOSFET and IGBT is presented in Table 2.1. Further details about different IGBT structures are presented in the next section.

Table 2.1. General comparison table for few power semiconductor devices.

| Characteristics     | Thyristor                   | Power Bipolar                | <b>Power MOSFET</b> | IGBT                 |

|---------------------|-----------------------------|------------------------------|---------------------|----------------------|

| Cost                | Low                         | Low                          | Medium              | High                 |

| Voltage rating      | High above 10kV             | Less than 1kV                | Around<br>1.4kV     | High<br>above<br>2kV |

| Current rating      | Around<br>10kA              | < 500A                       | Around 500A         | Around 1.5kA         |

| Switching Speed     | >500µs                      | >10µs                        | <10ns               | <10µs                |

| Control requirement | Complex commutation circuit | High continuous base current | Low gate current    | Low gate current     |

| Input Impedance     | Low                         | Low                          | High                | High                 |

| Output Impedance    | Low                         | Low                          | Medium              | Low                  |

# 2.2 Commonly Used IGBT Device Structures

## 2.2.1 Punch-Through (PT) IGBT

Among the most successful device structures for IGBTs, punch-through (PT) IGBTs are the oldest surviving technologies introduced into the market. Its device manufacturing relies on depositing of a thin n+ layer (buffer layer) upon the p+ substrate. On top of n+ layer, a separate n-drift layer is grown by epitaxy process. Furthermore, similar to D-MOSFET double diffusion for p and n wells by ion implantation and/ or diffusion processes take place as well. Lastly, the emitter and gate metallization are formed.

The structure is called punch-through because the e-field can penetrate through the entire drift region and extend into the buffer layer during the forward blocking mode (absence of gate control voltage). The buffer layer captures the injected minority carriers from p+ substrate at

Figure 2.1. Structure for PT IGBT.

faster recombination rate than the drift layer thereby helps in reducing the switching time. Since,  $V_{ce,on}$  is inversely proportional to higher recombination rate or shorter minority carrier lifetimes, the buffer layer thickness has to be adjusted accordingly. There exists another trade-off between the drift layer's thickness for sustaining higher blocking voltage and the associated conduction losses so it has to be controlled carefully during epitaxial growth.

# 2.2.2 Non-Punch-Through (NPT) IGBT

Non-punch-through (NPT) is another famous structure for IGBT. The main advantage with NPT is the positive temperature coefficient (tempco) of its  $V_{ce,on}$  so, it can be easily paralleled for

Figure 2.2. Structure for NPT IGBT.

higher current application without any complex thermal coupling mechanisms. Figure 2.3 shows the general structure of a typical NPT IGBT. Instead of p+ substrate, manufacturing of NPT IGBT starts with lightly doped n substrate which is lightly doped with acceptor (p-type) impurity to form collector. Similar to PT IGBT manufacturing, p and n wells are formed by ion implantation and/or diffusion processes followed by gate and emitter metallization. Since thick n substrate is used to support high BV without punch through, expensive epitaxial buffer layer is not required. The absence of additional buffer layer for rapid sweeping of minority carriers thicker layer slightly degrades the turn-off characteristics and also thicker drift layer (substrate) increases the conduction losses.

Figure 2.3. Structure for TGFS IGBT.

## 2.2.3 Trench Gate Field Stop (TGFS) IGBT

It is evident that PT provides lower switching and conduction losses whereas NPT has the beneficial positive tempoo for easy paralleling option. So, different variants have been introduced over the time to utilize the benefits of both device structures. In this connection, trench gate field stop (TGFS) structure, is one of the most widely used device structure.

Its manufacturing is similar to NPT yet there are two major differences. The first and noticeable difference is gate structure. In the previous designs, the gate lies flat on top of the device substrate however, for TGFS, it is almost completely buried inside the deep well (or trench as the structure name suggests). The second difference is the n type field stop layer. The

Table 2.2. IGBT device technologies comparison.

| Characteristics          | PT       | NPT                                                  | TGFS     |

|--------------------------|----------|------------------------------------------------------|----------|

| Cost                     | Low      | Lowest                                               | High     |

| Switching losses         | Low      | Highest (with no lifetime killing technique)  Lowest |          |

| Leakage current          | High     | Low                                                  | Lowest   |

| $V_{ce,on}$              | Low      | High                                                 | Lowest   |

| Tempco for $V_{ce,on}$   | Negative | Positive                                             | Positive |

| Chip size                | Largest  | Small                                                | Smallest |

| Short-circuit protection | Low      | High                                                 | Low      |

doping concentration in field stop layer is at least ten times lower to that found in the PT structure.

The main advantage of trench encapsulated gate is higher cell package ratio and removal of JFET effect by improved channel utilization and conductivity. Moreover, thinner n- substrate can sustain the high BV in the presence of field stop layer. Also, field stop layer speeds up recombination rate of the minority carriers comparable to that of PT IGBTs. Hence, the TGFS IGBTs provides the option of paralleling of multiple devices with lower on-state losses and faster turn off capability. The benefits of TGFS technology are compared with PT and NPT technologies in Table 2.2.

# 2.3 Physical IGBT Structure

In order to understand physical phenomena responsible for electrical parametric shift, simplified IGBT structure types and analytical expression for both  $V_{ce,on}$  and  $V_{th}$  are briefly discussed. An equivalent MOSFET-BJT of IGBT is shown in Figure 2.4 (a). Similarly, a detailed gate capacitance equivalent circuit is shown in Figure 2.4 (b). It can be seen that IGBT generally

Figure 2.4. Simplified circuit model for (a) MOSFET-BJT equivalent circuit and (b) gate-oxide capacitances.

provides the benefit of both MOSFET by using low power gate control and BJT by providing same conductivity modulation at high power levels within a single die. Yet, IGBTs are also prone to latch-up due to parasitic Thyristor of the structure. In order to eliminate the parasitic Thyristor, the voltage drop across base spreading resistance has to be kept to minimum so that the parasitic NPN transistor is not turned on. Further details about PT, NPT and TGFS internal device structure are given in Fig, 3 (a) - (c).

Using the model shown in Figure 2.4 (a),  $V_{ce,on}$  of an IGBT can be given as:

$$V_{ce,on} = V_{pn} + V_{NB} + V_{MOS} + V_{contact}$$

(2.1)

where  $V_{pn}$  is the p<sup>+</sup>-n<sup>-</sup> junction drop,  $V_{drift}$  or  $V_{NB}$  is the drift region (n<sup>-</sup>-layer) drop,  $V_{MOS}$  is the MOSFET region drop and  $V_{contact}$  electrical contact resistance drop. Further detailed analytical analysis can be found in [5].

In order to better understand the given results and associated discussions presented later in this paper, it important to note that  $V_{ce,on}$  temperature coefficient (tempco) is defined as a function of its collector current. Between different IGBT structures, the PT shows a negative tempco for much broader range of collector current compared to that of NPT and TGFS. Contrarily, NPT and TGFS display negative tempco for much smaller collector current values and are well suited for thermally-coupled parallel solution [6].

On the other hand,  $V_{th}$  of the IGBT can be defined as [5]:

$$V_{th} = V_{FB} + 2\sqrt{\phi_F^2 + 2\frac{q\epsilon_s N_A \phi_F}{C_{ox}}}$$

(2.2)

where  $V_{FB}$  is the flat band voltage of Si/SiO<sub>2</sub> interface,  $\Phi_F$  is the half contact potential, q is the charge of single electron,  $\varepsilon_s$  is the permittivity of Silicon,  $N_A$  denotes the acceptor type doping concentration of channel and  $C_{ox}$  is the gate oxide capacitance in per unit length. It is important to note that unlike other parameters in the Eq. 2.2 which remain more or less constant over IGBT lifetime, the degradation in gate oxide capacitance causes a significant impact on the  $V_{th}$ .

Gate oxide capacitance can be further divided into its constituting capacitances as well. Using the model shown in Figure 2(b), gate-emitter ( $C_{ge}$ ) and gate-collector ( $C_{gc}$ ) capacitances can be determined using following relationship [7]:

$$C_{ge} = \frac{C_{oxs}C_e}{C_{oxc} + C_e} + \frac{C_{oxc}C_c}{C_{oxc} + C_c}$$

(2.3)

$$C_{gc} = \frac{C_{ox}C_{dep}}{C_{ox} + C_{dep}} \tag{2.4}$$

where  $C_{oxe}$  and  $C_{oxc}$  denote the oxide layer capacitance with  $n^+$  and p regions respectively. Also,  $C_e$  and  $C_c$  represent the depletion layer capacitance for  $n^+$  and p regions respectively and  $C_{dep}$  represent the depletion layer capacitance under the oxide layer where  $C_{ox}$  is the oxide capacitance per unit area. However, it is difficult to measure these capacitances directly so, manufacturers typically specify parasitic capacitances of the IGBT. The parasitic capacitances mentioned in the datasheet generally include  $C_{ies}$ ,  $C_{oes}$  and  $C_{res}$  which define input, output and reverse gate capacitances, respectively. Following relationship can be used to estimate components of the total gate oxide capacitance:

$$C_{qc} = C_{res}; C_{qe} = C_{ies} - C_{res}; C_{ce} = C_{oes} - C_{res}$$

$$(2.5)$$

# 2.4 IGBT Reliability and Aging Mechanisms

As discussed in the introduction, catastrophic failures can take place in case of IGBT failures which results in costly shutdowns of the overall system. Through continuous monitoring not only costly shutdowns can be eliminated but also system availability can be improved. Although variety of failures in IGBT can occur which are probably triggered by different aging mechanism however, the main sources of stress remain the same. In fact during on field operation IGBTs are subjected to a variety of electrical as well as mechanical stresses which impact the device age condition and lead to potential failure.

Almost, every IGBT device is manufactured such that it can last for millions of cycles before substantial devices degradation occurs under given operating conditions yet, on-field failure data suggests otherwise. So, to determine the aging mechanisms and understand fatigue

Figure 2.5. Typical discrete package structure of an IGBT.

process, accelerated aging tests are employed. Furthermore, it is evident that aging tests and corresponding reliability data are required during the designing stage to ensure the reliability of IGBT devices in the power converters [8].

Based on the literature review, failure mechanisms can be classified in to two distinct groups; intrinsic and extrinsic failures. As shown in Figure 2.5, from reliability point of view, failures within the Si die are considered intrinsic whereas and failures in the rest of the package are considered extrinsic failures. The intrinsic failures are predominantly related to electrical stresses and can be either instantaneous or time-dependent failures. Yet, both can result in to short-circuit or open-circuit of IGBTs. The most commonly reported intrinsic failure mechanism is the time dependent di-electric breakdown. On the other hand, extrinsic failures are generally related to all other failures occurring within the package. It is understandable that the package comes in direct contact to the harsh environment conditions and therefore is subjected to failures due to excessive environmental stresses and wear-out. Moreover, bond-wire issue, solder delamination, Aluminum reconstruction are the commonly reported extrinsic failures.

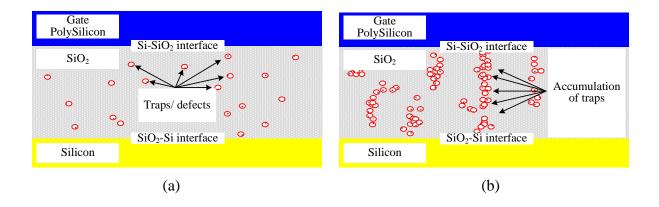

#### 2.4.1 Intrinsic Failures

Gate-oxide degradation is one of the primary degradation mechanisms especially at elevated operating temperatures. Typically, gate-oxide (or Silicon Dioxide in case of IGBT) properties are altered in the presence of strong electric field. Such changes may also occur under lower electric field (applied over a longer period of time) and/or thermal degradation of gate-oxide [9]. Primarily, gate-oxide breakdown occurs due to the defects formation or traps within the oxide layer. As the traps density exceeds the percolation threshold (beyond critical limit for insulator to act like a conductor), the defects begin to accumulate and overlap one another to form a current leakage path through the previously insulating oxide layer.

Even in pristine IGBT devices thermally generated defects formation can take place. It is so because silicon dioxide like every real oxide is not a perfect insulator having some finite conductivity especially at high electric fields. Notably, these defects may be pre-existing particularly for devices manufactured using thermally grown oxide process. Nevertheless, conduction through the insulator may be detrimental as it heats the oxide more inducing further formation of traps. Once the percolation threshold is exceeded, the overlapping traps form a current leakage path and this formation is commonly referred as soft breakdown in the literature. Beyond soft breakdown, thermal runaway effect is also possible to yield more defects. This increased trap density leads to further conduction and eventual oxide meltdown [10]. Upon melting, oxygen may be released and conductive Si filaments may be formed. This catastrophic failure mode is classified as a hard breakdown [11]. Once conducting pathway is established, gate leakage current increases for both on and off states which was previously negligibly low.

Figure 2.6. Steps of gate-oxide degradation.

Particularly in hard breakdown cases, gate current may increase by almost hundred to million times in the on and off states, respectively [12, 13]. The steps of gate oxide degradation are illustrated in Figure 2.6. More details about traps formation can be found in [14].

Hot electrons affect the gate oxide characteristics in similar fashion. Electrons (and holes) which gain sufficiently high kinetic energy under large potential difference applied across collector-emitter terminals and generate electron-hole (e<sup>-</sup>-h<sup>+</sup>) pairs in the transistor channel due to impact ionization are termed as "hot carriers" or simply hot electrons [15, 16]. The generated

Table 2.3. Sources of stress for common package related failures.

| Failure mechanism                                 | Type of stress                                                                                 |

|---------------------------------------------------|------------------------------------------------------------------------------------------------|

| Bond wire issue (lift-offs and cracks)            | Maximum temperature swing, mean temperature and rising and falling slope temperature           |

| Die attach solder joints issue (cracks and voids) | Maximum temperature swing, mean temperature, rising and falling slope temperature and humidity |

| Aluminum metallization reconstruction             | Mean temperature and current density                                                           |

e<sup>-</sup>h<sup>+</sup> pair dissociates in the channel; while the hole moves to the substrate, the electron impacts the gate oxide and leads to trap formation. These charged traps can directly alter gate threshold voltage and affect the transistor operation. Moreover, hot electrons have been shown to reduce the time to gate-oxide breakdown [17].

# 2.4.2 Extrinsic Failures

Almost all extrinsic failure mechanisms are related to package which occur due to environmental stresses [18]. Capturing of extrinsic failures in early stages is generally easier than some of the intrinsic failures because the degradation due to underlying aging mechanisms accrue over a period of time. Mostly, temperature related stresses are held responsible for majority of package related failures. Most commonly reported extrinsic failure and corresponding aging mechanisms are briefly described in the following subsections. Table 2.3 provides the summary of the responsible electro-mechanical stresses for failure mechanisms [19].

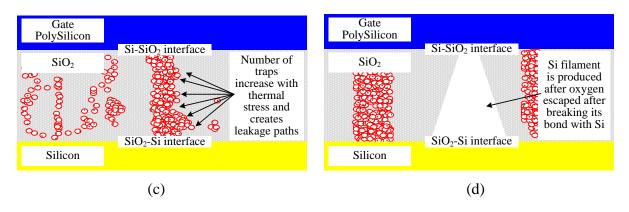

Figure 2.7. Bond wire lift-off different IGBT samples; (a) Lift-off after power cycling test and (b) magnified image of another sample showing lift-off pattern.

### **Bond-wire Fatigue**

Bond wire lift-off is one of the most commonly reported failure mechanism especially under low temperature swing [20], [21]. Wire bond connections are most susceptible to thermomechanical stresses due to their presence in close vicinity of die and junction. During switching operation at rated current, the chip undergoes severe thermal stress due to heat generated as the result of power losses. So, the wire bonds are also exposed to almost the same temperature swing like the chip. This condition is further aggravated by the varying spatial thermal gradient within the die due to inherent uneven heating. Moreover, thermal gradients are coupled with the CTEs mismatch between the aluminum metal wire bond (~22ppm/K) and the silicon semiconductor chip (~4ppm/K).

Figure 2.8. Cross-sectional image of crack initiation in the bond wire.

The wire bond failure may start from bond wire tail or heel. Cracks appear alongside the perimeter of aluminum grains. The wire-bonding process is generally produces deformation in the wire material. Particularly, small grains are formed built in the interface region (contact with the bond pad) during the following system soldering process. The grain size in the wire center is much larger than in the welded zone [22]. Typically, small sized grains exist at the periphery of the bond wire whereas larger grain sizes prevail in the center due to the process. So, the crack is initiated once the wire could not to contain local strain. Figure 2.7 shows crack in the bond wire of an aged IGBT [23]. The wire bond becomes weaker with every thermal cycle in a self-accelerating manner. As the crack reaches the center of the bonding region, the electromechanical contact breaks down [24]. In Figure 2.8, bond-wire lift-off has been shown for two different IGBTs.

#### **Die-attach Solder Joint Failure**

Solder joint degradation is another failure mechanisms commonly reported for IGBT devices. The primary reason for solder degradation is the mismatch between CTEs of different metals and/or alloys (Al, Cu and Si). The power loss generated in a switching cycle needs to be rapidly dissipated from the chip in to the ambience. The losses induced heat produces temperature gradients along the vertical and lateral dimensions of the package such that the product of temperature gradients and CTEs mismatch causes thermomechanical stresses across all the layers in the package creating fatigue problems. Even with closely matched CTEs, the varying temperature gradients could still cause the solder degradation. Figure 2.9 shows one example of solder issues [25].

Discrete package contains only one die and the die is directly soldered to copper back plate (base plate). Additionally, the CTEs at both the interfaces rarely match which make these interfaces more prone to fatigue [23]. Once the solder degradation starts, creepage leads to forming voids and cracks in the solder layer [26, 27]. This unevenness of the solder layer increases the thermal resistance from the die to the base plate [28, 29] as well.

It was reported that for lead-tin alloy soldered onto copper metallization, different intermetallic phases are formed near copper layer and center of the solder layer which may be rich in tin or lead [30]. Upon thermal accelerated aging test, the periodic temperature swing produces shear stress across the package. Since, copper rich intermetallic phases are more brittle, thermomechanical fatigue crack spread more in them. Particularly, these cracks progresses from the edge where the shear strain is maximum to the center which is relatively under less strain. It is so because at the corners attached materials can easily expand due to spatial temperature

Figure 2.9. Large voids and crack in the die-attach solder layer.

gradient however, near the attachment interface the expansion is constricted leading to cracking under fatigue.

Moreover, Voids and cracks formation offer hindrance to heat flow from the chip to the ambience through the heat sink. Reduction in active surface area for heat transfer increases the thermal impedance. As more heat is accumulated within the package layers, the die temperature continue to rise which could lead to catastrophic burn-out failures and secondary breakdown. Due to lead health hazards, new lead-free solder (e.g. soft solders) have been introduced. Comparison of lifetime for lead-tin and lead free Terminal solder joint alloys was studied by Feller et al. [31]. Also, crack initiation and ensuing growth were observed for both solder types. Analysis in [32] indicates that cyclic lifetime of the die-attach bonding has a strong dependence on the variability between die bond thicknesses for tested samples.

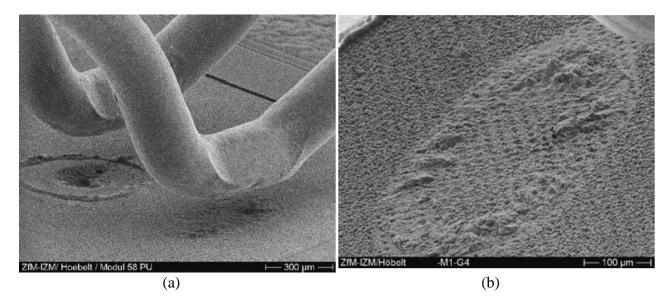

Figure 2.10. Aluminum grain boundary reconstruction (a) before power cycling and (b) after power cycling.

### **Aluminum Metallization Reconstruction**

Periodic tensile and compressive thermomechanical forces are being exerted on the upper metallization surface under high cyclic thermal stress. There exist a significant mismatch between the top aluminum surface and the silicon semiconductor chip underneath it. Typically, for same amount of heat, aluminum metallization layer makes significant expansion (around 24 ppm/K) contrary to silicon chip which need to marginally expand (around 2-3 ppm/K) with rising temperature. As a result, the metallization layer is subjected to compressional stresses. Moreover, contact metallization layer has large grain structure. Upon experiencing such high level of thermal stresses beyond elastic limit, mechanically induced relaxation takes place which causes plastic deformation and aluminum grain boundary extrusion [30].

Ciappa [33] considers that the periodic compression stress due to rising junction temperature in excess of 110 °C causes plastic deformation of grains. Plastic deformation then leads to the extrusion of aluminum grain boundaries. As a result, the metallization surface

becomes rough and dull non-reflective surface. However, during the cooling phase (removal of thermal stress) tensile stress is generated. If the temperature makes significantly large swing, these tensile stresses may go beyond the elastic limit of aluminum and cavitation effects at the grain boundaries can occur. Nevertheless, under continued stress, such effects reduce density of contacting material thereby increasing the electrical contact resistance [34]. Also, such mechanisms can create cracks in the metallization layer surface. Figure 2.10 shows images of top aluminum surface before and after degradation [30].

#### CHAPTER 3

# IDENTIFICATION OF SUITABLE AGING PRECURSORS<sup>1, 2</sup>

As discussed in previous chapter, every IGBT is manufactured for delivering maximum performance for at least few hundred million operational cycles which may correspond to 10 to 20 years of service lifetime depending on the exact operating conditions. So, to investigate the effects of thermomechanical stresses in short period of time, accelerated aging (temperature and power cycling) tests is a recognized industrial practice. Consequently, a custom aging setup has been developed for executing a variety of temperature induced aging.

In this chapter, initially, details about the accelerated aging setup for IGBTs are presented [35]. Later, variations in electrical characteristics collected by an automated state-of-art curve tracer at regular interval during aging tests for tested device samples are presented [36]. Based on the exhaustive tests results, suitable aging precursors are identified. Also, failure analysis results have been discussed in this chapter as well.

### 3.1 Highly Accelerated Aging Test

Through accelerated aging tests, fatigue process can be speed up [37, 38]. It has been shown that the wear-out status of the power switches can be detected through electrically measurable quantities called "aging precursors" [39]. Therefore, prior knowledge on deviation in device

<sup>&</sup>lt;sup>1</sup> ©2016 IEEE. Reprinted with permission from S. H. Ali, S. Dusmez and B. Akin, "A comprehensive study on variations of discrete IGBT characteristics due to package degradation triggered by thermal stress," in Proc. of 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-6.

<sup>&</sup>lt;sup>2</sup> ©2016 IEEE. S. H. Ali, S. Dusmez and B. Akin, "Investigation of collector emitter voltage characteristics in thermally stressed discrete IGBT devices," in Proc. 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-6.

characteristics can provide significant information for accurately predicting their failures and real-time on-board prognosis [40, 41]. A comprehensive review on current fault diagnostic and protection methods is presented in [37], [42].

In literature, reliability of IGBT modules has been studied to great extent [43-45]. In contrast to discrete package devices, an IGBT module may contain several semiconductor chips, paralleled with the help of more than one bond-wire. The findings reported in the literature are variations in collector-emitter saturation voltage [43, 44], [46], thermal impedance [47, 48], turn off time [49], input, output and reverse transfer capacitances [44], change in phase and amplitude of ringing during turn-off [50] and gate threshold voltage [12]. Nevertheless, only a few studies focused on the discrete package IGBTs [39].

During these aging tests, main focus has been devoted to capture variations in the i-V characteristics and parasitic elements of IGBTs. Shifts in device characteristics, such as gate threshold voltage ( $V_{th}$ ), input/output/reverse capacitances ( $C_{ies}$ ,  $C_{oes}$  and  $C_{res}$ ), on-state collectoremitter voltage drop ( $V_{ce,on}$ ) and breakdown voltage ( $BV_{ces}$ ) for new and aged devices are investigated. Majority of these parameters require sensitive measurements, which are obtained through automated curve tracer. Due to the difficulties faced in the high-resolution measurements ( $\mu V$ , nA), these noise-sensitive measurements have been either omitted in previous papers or not discussed in detail.

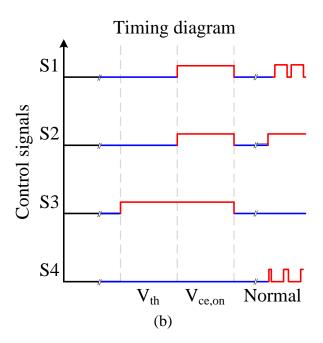

### 3.1.1 Aging Test Setup Overview

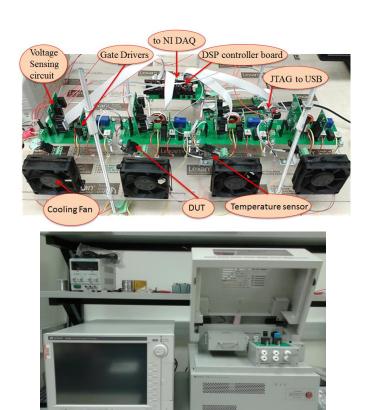

To inspect the effects of electro-thermal stresses on IGBTs in a shorter amount of time, a custom designed accelerated aging test setup is developed, whose schematic details are shown in Figure 3.1. Figure 3.2 provides the snapshot of actual aging test setup including the Keysight B1506a

Figure 3.1. Circuit schematic for designed aging testbed for IGBTs.

Power Device Analyzer (curve tracer). The developed test-bed comprises of four independent modules. Each module is designed in a modular fashion and has its own gate driver board, power supply and signal conditioning submodules. Individual fans are also installed for cooling the devices under test (DUT). All four modules are individually controlled by TI Delfino 28335 DSP controller board. An NI 6255 data-acquisition system (DAQ) is also connected to the computer for on-line monitoring and recording of  $V_{ce,on}$  voltage. Moreover, the curve tracer has been used as integral part of the setup. The curve tracer is employed at regular intervals during the aging test which takes a variety of electrical parameters measurements.

The signal conditioning sub-module measures the  $V_{ce,on}$ , collector current ( $I_{ce}$ ), and case temperature ( $T_c$ ) for temperature control purposes.  $V_{ce,on}$  has to be measured by a dedicated voltage sensing circuit, whose details are discussed in [51], to protect the DAQ from high voltage when DUT is at off-state. Moreover, it allows high resolution measurement of  $V_{ce,on}$  which is not possible with a voltage sensing circuit utilizing ubiquitous voltage dividing resistors.  $T_c$  is measured using K-type thermocouple attached to the bulk case of DUTs. All these signals are further sent to the DSP board for control purposes and also to the DAQ for data monitoring and recording.

Either of the continuous on/off and switching based cyclic test approaches can be implemented in the setup. DUTs are individually loaded with their own dedicated power supplies without adding any external load. Each power supply is operated as a current source to pump desired amount of current into the DUT during the heating cycle. Limiting the current manually removes the necessity for additional current control loops for each DUT in the DSP.

Figure 3.2. Actual photograph of designed aging testbed for IGBTs along with the curve tracer.

## **3.1.2** Temperature Control

A hysteresis temperature control is implemented in DSP software for each DUT. Basically, the switch is kept in on-state till the temperature reaches to defined upper limit. The DSP estimates the junction temperature of individual DUT from the conducted losses ( $V_{ce,on}$  and  $I_{ce}$ ), thermal impedance model ( $Z_{th}$ ), and  $T_c$  measurement in order to generate corresponding gating signals for the DUTs. After the upper limit for  $T_j$  is achieved, DSP turns off the corresponding DUT. Once the DUT is turned off, the corresponding cooling fan is engaged for faster cooling. Due to heat-transfer delays from package to thermocouple, measurement differences occur. These are modeled as thermal capacitance,  $C_{th}$  in the thermal model. Comparing with measurements by

FLIR E6 IR non-contact camera, these errors are corrected in the DSP software. Nevertheless  $T_c$  measurements are not available instantly due to sluggish response of thermocouples and create some  $T_j$  estimation so, fine tuning of controller and subsequent timing for gating pulses are performed through trial and error.

## 3.1.3 Upper $T_i$ Limit for Highly Accelerated Aging Test

It is well known that Silicon and other semiconductors offer intermediate conductivity (compared to typical conductors and insulators) at the room temperature. Moreover, pure (intrinsic) semiconductors contain equal distribution for electrons and holes but extrinsic semiconductors are doped with generally one dominant type-either electrons or holes to alter the electrical characteristics e.g. conductivity. For a given amount of thermal energy at a particular temperature, Si atoms contribute fairly small number of charge carriers and the overall conductivity depends on the amount of dominant charge carriers.

It is understandable that the device temperature impacts the electron-holes distribution in the power semiconductor and the devices' characteristics as well. So, the advantageous electrical characteristics of semiconductor for maintaining appropriate power control are guaranteed only within certain temperature range. As the temperature exceeds certain limit, Si atoms themselves generates comparable amount of charge carriers compared to the dominant ones [52]. So, device conductivity becomes uncontrollable and desirable power flow is compromised. Due to uncontrollable charge flow, thermal runaway is also inevitable. This thermal energy is referred as critical energy in the literature.

Typically, critical energy limit is determined by the semiconductor's bandgap energy. As a rule of thumb, 500 times the bandgap energy of Si which corresponds to ~ 300°C is considered

enough to cause thermal runaway [53]. For a device which does not experience any thermal failure, it shows typical characteristics upon cooling below 150°C (suggested by manufacturers). As explained earlier, the junction temperature and current is regulated to avoid heating the devices to the critical limits for DUTs.

#### 3.1.4 Test Procedure for Parametric Device Characterization

Initially, a number of 1200V / 11A power rating DUTs are subjected to relatively large temperature swings to observe the aging mechanisms. Based on these tests suitable aging precursors are determined. Each device sample was individually subjected to temperature swing of  $40\text{-}200^{\circ}C$ . It is ensured that the maximum  $T_j$  is well below the corresponding temperature limit for critical energy but at the same time yields faster results. During these high temperature tests, high degrees of gate-oxide and die-attach solder degradations in the DUTs are anticipated. During this test, one thermal cycle lasts for almost three minutes (45s and 110s for heating and cooling respectively). Thus, the consequences of these two aging mechanisms were observed before there was any significant damage on the bond-wires.

The test is stopped at regular intervals and DUTs are placed in the curve tracer for measuring aged device parameters. Also, control sample is used to ensure measurement accuracy. The measurements taken using curve tracer are 1)  $BV_{ces}$ , 2) gate currents, 3) gate resistance, 4)  $V_{ce,on}$ , 5)  $V_{th}$ , 6) gate charge and 6) parasitic capacitances. One important point to note is that all the curve tracer measurements are taken at ambient temperature ( $T_{amb} = 28^{\circ}$ C). After measurements are taken, all the DUTs are placed back into the setup for aging. This procedure is repeated for every DUT until it can no longer be turned ON or OFF by its corresponding gate driver. This is referred as "loss of gate control" in further discussion.

Table 3.1. Summary of device condition after failure for first set of devices.

| Device  | Number of cycles to failure (Nf) | Device description after failure                                                                                                                                |  |

|---------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGBT-3A | 2594                             | Always OFF → Open Circuit (cannot turn ON by the gate driver circuit), high leakage current, small G-to-E resistance but significantly higher C-to-E resistance |  |

| IGBT-5A | 2674                             |                                                                                                                                                                 |  |

| IGBT-4A | 2059                             | Always ON → Short Circuit (cannot turn OFF by the gate driver circuit), possible latch-up, high leakage current, small resistance between G-E or C-E terminals  |  |

The summary for each DUT after failure is presented in Table 3.1. In the next section, the results describing the general behavior of the tested samples are shown.

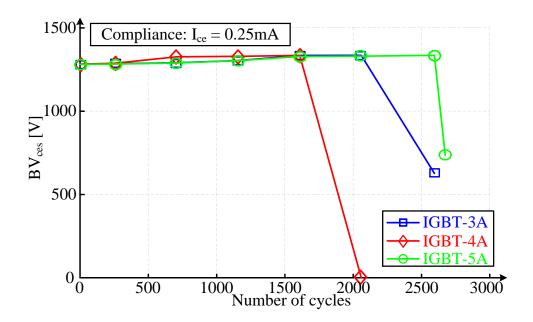

### 3.2 Parametric *i-V* Characterization

The *i-V* characteristics for DUTs from Table 3.1 are shown in Figures 3.3-3.7. Figure 3.3 shows the variation in  $BV_{ces}$  with aging. The compliance current for  $BV_{ces}$  measurement is 0.25mA. Almost a maximum of 16V positive increase can be seen from the value before aging. This is a negligible change considering the original BV capability > 1.2kV. Moreover, this increase in  $BV_{ces}$  can be attributed to lower carrier injection rate in breakdown region at elevated temperature [23].

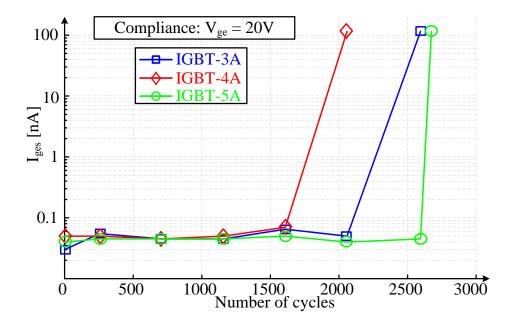

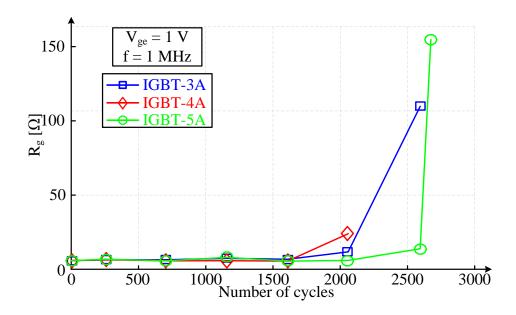

Similarly, variations in gate leakage current are shown in Figure 3.4. It is noticed that gate oxide degradation causes no consistent change in gate leakage currents. Similarly, consistent variation is not found for the gate resistance as is shown in Figure 3.5. Similar, to  $BV_{ces}$  measurements, the gate measurements also change significantly once the DUT reaches its end of life (EoL). Nevertheless, all of these parameters are important electrical characteristic of the

Figure 3.3. Variation in breakdown voltage with respect to aging.

Figure 3.4. Variation in gate leakage current with respect to aging.

Figure 3.5. Variation in gate resistance with respect to aging.

IGBT but from selecting aging precursor point of view, the inconsistent changes are not suitable. Yet, at the same time, these measurements can be used for fault detection and other condition monitoring purposes.

Similarly, the gradual increase in on-state voltage drop of IGBT-3A sample at different current levels for multiple aging intervals have been shown in Figure 3.6. It is worthwhile to note that below  $I_{ce} = 5 \text{A} \ V_{ce,on}$  decreases with number of aging cycles and sometime before failure rises above respective values before start of aging. On the contrary,  $V_{ce,on}$  for  $I_{ce} > 5 \text{A}$  a continuously rising trend has been shown. The steady increase in  $V_{ce,on}$  turns to sharp rise before failure suggests degradation of electrical and thermal resistances in the DUT package. The die attach solder is anticipated to be degraded which correspondingly cause  $V_{ce,on}$  decrease with negative tempco below certain  $I_{ce}$ . Detailed failure analysis results are discussed later in the chapter to confirm this hypothesis.

Figure 3.6. Variation in on-state collector-emitter voltage drop at different collector current with respect to aging.

Figure 3.7. Variation in gate threshold voltage with respect to aging.

Figure 3.8. Comparison of gate charge at different gate voltages for new (before aging) and aged DUT.

Figure 3.9. Comparison of parasitic capacitance at different collector-emitter voltages for new (before aging) and aged DUT.

Lastly, Figure 3.7 shows the variation in gate threshold voltage with respect to aging. Also, gate charge and parasitic capacitance variations are also shown in Figure 3.8 and 3.9 respectively, for better understanding and confirming of failure mechanisms. One plausible reason for the gate-oxide degradation is presence of defects and/or trapped charges in the insulator (gate-oxide) [54]. This hypothesis is strengthened by the fact that the gate charge has increased for the devices before failure. Since, the gate capacitances and gate-oxide are strongly interrelated so, it is expected that the degraded gate-oxide causes the change in gate capacitance as well. Further discussion on analytical relationship among parasitic capacitances and gate capacitance and their impact on  $V_{th}$  with aging is presented later in the chapter.

# 3.2.1 Failure Analysis

To shorten the device lifetime or achieving fast device failure, the *Tj* has been allowed to reach very high values which trigger multiple degradation mechanisms as discussed in the previous chapter. During the test, DUT generates heat for almost one minute and require cooling for almost two minutes. Ultimately, larger thermal swings coupled with long relaxation (cooling time) stress all the package layers. This causes more degradation in gate-oxide and die-attach solder joints than the bond-wires because of their larger lateral dimensions.

As shown in Table 3.1, DUTs lasted for less than 2500 cycles. Two failure modes are observed but generally, individual gate control for each DUT is lost before failure. Moreover, using a handheld multimeter, resistances between DUT terminals are noted as well. In order to confirm the earlier presented hypothesis, DUTs are sent to failure analysis laboratory.

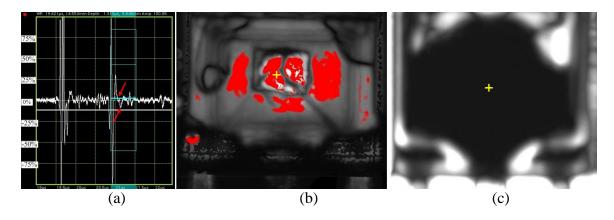

Figure 3.10. C-SAM result for failed DUT with red spots indicating large voids in the die-attach layer and no significant bond-wire issues.

The acoustic imaging analysis or C-SAM and T-SAM analyses are performed to inspect probable delamination and voids on the package layers. Both of these tests use ultrasonic transducers to transmit and receive high frequency audio signals. Since velocity of sound differs through *thin* and *thick* mediums, the analysis of time of flight/ time of arrival (ToF/ ToA) information for the received audio sample reveals possible voids in the analyzed samples. Particularly, C-SAM analyzes the ToF/ ToA for reflected audio signal time from the top surface of sample. Depending on the color scheme used in the graphical user interface (GUI) for automated C-SAM test, significant attenuation of audio signal is displayed as red spots. On the other hand, T-SAM uses two ultrasonic transducers to transmit and captures the refracted audio signals from the sample. As long as the audio signal traverses without any significant attenuation

Figure 3.11. T-SAM result for failed DUT with dark spot obscuring die showing significant delamination in the package at multiple layers.

clear images appear on GUI of T-SAM test. GUI identifies those locations as dark spot(s) where the transmitted audio signal experiences attenuation due to presence of thin air or voids.

C-SAM and T-SAM results for one of the aged DUTs are shown in Figure 3.10 and 3.11. The C-SAM result indicates that there are several large voids in die-attach layer. Also, the homogenous dark spots in T-SAM images confirm delamination. Furthermore, during cross section no bond-wire issues are observed.

# 3.3 $V_{th}$ and $V_{ce,on}$ Characterization at Different Thermal Stress Levels

In the previous section, both  $V_{th}$  and  $V_{ce,on}$  have been observed to show reliable and consistent variations. Moreover, in order to firmly validate the utility of both as aging precursors, it is necessary more aging test at different stress levels are performed. At the same time, to emphasize

that thermal stresses resulting from all different forms of temperature variations particularly; magnitude of temperature swing, mean temperature and slope of temperature cause severe impact on the IGBTs lifetime. Also, for ac-dc rectifiers and dc-ac inverters, both the mean  $T_j$  and cyclic  $T_j$  of the IGBTs increase whereas in dc-dc converters only mean  $T_j$  for the IGBTs rise above the ambient temperature during their operation [55]. So, it is necessary to stress the devices at variety of temperature levels.

Different thermal stress scenarios applied on DUTs are grouped in to two different schemes. In the first scheme, samples have been stressed within manufacturer's specified safe operating  $T_j$  limits (SOA) or slightly above it. Although majority of the tests carried out in this scheme falls into SOA limits, just one set of DUTs have been allowed to reach  $T_{j,max} = 180^{\circ}$ C (above the defined SOA). In the other test scheme, the high level of stresses has been applied by maintaining the maximum  $T_j$  well above SOA limits.

Multiple IGBT technologies are tested systematically in order to verify the aging trend. All the thermal stress test schemes have been applied for different IGBT technologies. IRG4PH20K (punch through, PT), IGW03N120H2 (non-punch through, NPT), IRG8P08N120KD (trench gate field stop, TGFS), STGW15H120F2 (trench gate field stop, TGFS) and HGTG5N120B (non-punch through, NPT) have been used as DUTs in this study. These samples are referred as PT (A-series), NPT-1 (B-series), TGFS-1 (C-series), TGFS-2 and NPT-2 respectively. Since PT produces more significant parametric variations than others, the

Table 3.2. Summary of applied thermal stress testing schemes.

| Test Scheme | Test number | Maximum $T_c$ cycle range | IGBT type    | $\begin{array}{c} Approximate \\ maximum \ t_{on} \ / \ t_{off} \end{array}$ |

|-------------|-------------|---------------------------|--------------|------------------------------------------------------------------------------|