# PREDICTABLE GPGPU COMPUTING IN DNN-DRIVEN AUTONOMOUS SYSTEMS

by

# Husheng Zhou

# APPROVED BY SUPERVISORY COMMITTEE:

| Cong Liu, Chair   |

|-------------------|

|                   |

|                   |

|                   |

|                   |

| Farokh B. Bastani |

|                   |

|                   |

|                   |

|                   |

| András Faragó     |

|                   |

|                   |

|                   |

|                   |

| Lingming Zhang    |

|                   |

Copyright © 2018

Husheng Zhou

All rights reserved

## PREDICTABLE GPGPU COMPUTING IN DNN-DRIVEN AUTONOMOUS SYSTEMS

by

# HUSHENG ZHOU, BS, MS

#### DISSERTATION

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

# DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

THE UNIVERSITY OF TEXAS AT DALLAS

December 2018

#### **ACKNOWLEDGMENTS**

First and foremost, I am deeply grateful to my advisor, Professor Cong Liu, for his incredible guidance, endless support and encouragement throughout my entire PhD life. He introduced me to the field of real-time systems. He taught me from scratch on how to do research from an idea to problem solving and presenting a paper. His passion in research always inspires me to be a better researcher.

I also would like to express my gratitude to all of my collaborators, Zheng Dong, Soroush Bateni, Yuchuan Liu, Xia Zhang, Yue Ma, Yuankun Zhu, and Mozi Chen. I am deeply indebted for their tremendous help, both in work and life. I cherish my time working with them. I am also grateful to my mentors of internship, Dr. Liana Fong and Dr. Wei Tan, for giving invaluable guidance during my summer intern at IBM T. J. Watson Research Center.

My life in Dallas would not be as easy and happy without my friends. I would like to particularly thank a number of my friends: Yufei Gu, Yangchun Fu, Junyuan Zeng, and friends in Plano Chinese Alliance Church. Friendships with them made all the difference in the past six years.

Finally, my family members have always been there for me with unconditional love and support. This dissertation is dedicated to my parents, my awesome wife, Ruohan Zhang, and my cute baby girl, Chloe Zhou.

October 2018

PREDICTABLE GPGPU COMPUTING IN DNN-DRIVEN AUTONOMOUS SYSTEMS

Husheng Zhou, PhD

The University of Texas at Dallas, 2018

Supervising Professor: Cong Liu

Graphics processing units (GPUs) are being widely used as co-processors in many domains to

accelerate general-purpose workloads that are data-parallel and computationally intensive, i.e.,

GPGPU. An emerging usage domain is adopting GPGPU to accelerate inherently computation-

intensive Deep Neural Network (DNN) workloads in autonomous systems. Such autonomous sys-

tems are usually time-sensitive, especially for autonomous driving systems. When driving along-

side human drivers, loss of life or property may result if the computing systems of the autonomous

vehicles fail to respond to events before its deadline. Much research has been conducted to algo-

rithmically optimize the accuracy and performance of deep neural networks, but limited attention

has been given to optimizing the execution of GPU-accelerated DNN workloads from the schedul-

ing angle, especially in a time-constrained multi-tasking environment.

Adopting GPGPU to accelerate DNN workloads in time-sensitive autonomous systems that are

often resource-constrained presents a series of challenges: (1) GPUs are designed to execute non-

preemptively, which may cause priority inversion; (2) How to optimize the execution of GPU-

accelerated DNN workloads at the system level in a real-time multi-tasking environment; (3) How

to simultaneously achieve two (often) conflicting goals in a resource-constrained embedded CPU-

GPU heterogeneous platform: timing predictability and energy efficiency, that are essential for any

DNN-based autonomous driving system.

vi

The goal of the research presented in this dissertation is to solve or remedy the aforementioned challenges. Specifically, we propose GPES, a runtime system that allows GPU executions to be interruptible and preemptable in a multi-tasking environment. We proposed  $S^3DNN$ , a systemic solution that optimizes the execution of DNN workloads on GPU in a soft real-time multi-tasking environment. We proposed PredJoule, a runtime system which presents a layer-based approach that controls the timing and optimizes energy efficiency by exploiting each layer's performance/energy characteristics. In addition to the runtime systems we proposed, we investigate the problem of mapping multiple applications implemented using kernel graphs in a heterogeneous system, and present a theoretical framework that formulates this problem as an integer program and a set of practically efficient mapping algorithms. Furthermore we present a reuse-based approach to further improve the predictability of GPU computing.

# TABLE OF CONTENTS

| ACKNO   | VLEDGMENTS                                           | V   |

|---------|------------------------------------------------------|-----|

| ABSTR.  | CT                                                   | vi  |

| LIST OF | FIGURES                                              | xii |

| LIST OF | TABLES                                               | ΧV  |

| CHAPT   | R 1 INTRODUCTION                                     | 1   |

| 1.1     | Graphics Processing Units                            | 3   |

| 1.2     | GPGPU Programming Model                              | 6   |

| 1.3     | Deep Neural Networks                                 | 8   |

| 1.4     | Contributions                                        | 9   |

| 1.5     | Organization                                         | 12  |

| CHAPT   | R 2 BACKGROUND AND RELATED WORK                      | 13  |

| 2.1     | Scheduling Algorithms for Heterogeneous Systems      | 13  |

| 2.2     | Runtime Engines for Heterogeneous CPU/GPU Processors | 13  |

| 2.3     | GPU Resource Management                              | 15  |

| 2.4     | Real-time DNN-Based Object Recognition               | 16  |

| 2.5     | Optimizing Energy While Meeting Timeliness           | 16  |

| 2.6     | Kernel Transformation                                | 18  |

| 2.7     | Managing GPUs in The Cloud                           | 18  |

| 2.8     | Computing Result Reuse                               | 18  |

| CHAPT   | R 3 PREEMPTIVE EXECUTION FOR GPGPU                   | 20  |

| 3.1     | A Case Study                                         | 20  |

| 3.2     | System Design and Implementation                     | 21  |

|         | 3.2.1 Kernel Execution Slicing                       | 22  |

|         | 3.2.2 Data Transfer Slicing                          | 27  |

|         | 3.2.3 Context Switch Scheduling                      | 29  |

|         | 3.2.4 Challenges and Limitations                     | 30  |

| 3.3     | Evaluation                                           | 31  |

|         | 3.3.1 Experimental Setup                             | 31  |

|              | 3.3.2  | Overhead due to kernel slicing                           | 32 |

|--------------|--------|----------------------------------------------------------|----|

|              | 3.3.3  | Overhead due to data slicing                             | 33 |

|              | 3.3.4  | Overhead of context switching                            | 34 |

|              | 3.3.5  | Multi-Tasking Performance                                | 35 |

|              | 3.3.6  | Non-real-time setting                                    | 39 |

|              | 3.3.7  | Defending against DOS Attacks                            | 40 |

| 3.4          | Summa  | ary                                                      | 41 |

| CHAPT<br>REA |        | STREAM SCHEDULING FOR GPU-ACCELERATED E DNN WORKLOADS    | 43 |

| 4.1          | Motiva | ution                                                    | 43 |

|              | 4.1.1  | GPU Usage Pattern For DNNs                               | 43 |

|              | 4.1.2  | Data Fusion                                              | 45 |

|              | 4.1.3  | Kernel Scheduling and Concurrency                        | 47 |

| 4.2          | Design | and Implementation of $S^3DNN$                           | 50 |

|              | 4.2.1  | Design Overview                                          | 50 |

|              | 4.2.2  | System-level Data Fusion                                 | 52 |

|              | 4.2.3  | Supervised Streaming and Scheduling                      | 55 |

| 4.3          | Evalua | tion                                                     | 62 |

|              | 4.3.1  | Experiment Setup                                         | 62 |

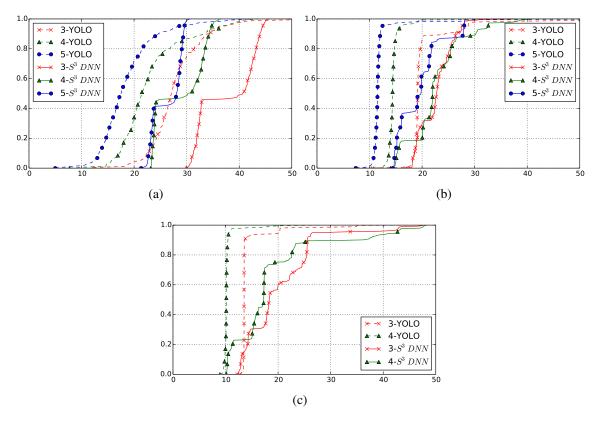

|              | 4.3.2  | Real-time performance                                    | 63 |

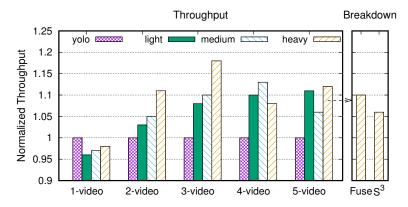

|              | 4.3.3  | Overall Throughput                                       | 64 |

|              | 4.3.4  | Assessing the Supervised Streaming and Scheduling Module | 65 |

|              | 4.3.5  | Multi-GPU scenarios                                      | 67 |

|              | 4.3.6  | Online Webcam-based Object Recognition                   | 69 |

| 4.4          | Summa  | ary                                                      | 69 |

| CHAPT<br>FOR | _      | ΓΙΜΙΝG-PREDICTABLE ENERGY OPTIMIZATION NEURAL NETWORKS   | 71 |

| 5.1          | Motiva | ntion                                                    | 71 |

|              | 5.1.1  | DNN-specific Energy Usage Patterns                       | 71 |

|              | 512    | Energy-Performance Relationship                          | 73 |

| 5.2          | Design  |                                                                          |

|--------------|---------|--------------------------------------------------------------------------|

|              | 5.2.1   | Uncertainty                                                              |

|              | 5.2.2   | Progress Tracker                                                         |

|              | 5.2.3   | Integration                                                              |

| 5.3          | Evalua  | tion                                                                     |

|              | 5.3.1   | System Setup                                                             |

|              | 5.3.2   | Generality                                                               |

|              | 5.3.3   | Detailed Latency/Energy Performance                                      |

|              | 5.3.4   | Adaptability With Interference                                           |

|              | 5.3.5   | Overhead                                                                 |

| 5.4          | Summa   | ary                                                                      |

| CHAPT        |         | TASK MAPPING IN HETEROGENEOUS SYSTEMS FOR FAST COMPLE-                   |

| TIO          |         |                                                                          |

| 6.1          | System  | Modeling and MIP Formulation                                             |

|              | 6.1.1   | System Model                                                             |

|              | 6.1.2   | An MIP Formulation                                                       |

| 6.2          | Case S  | tudies: What to Consider for Making Mapping Decisions                    |

| 6.3          | Practic | al Mapping Algorithms                                                    |

|              | 6.3.1   | Baseline Algorithm: Heterogeneity Ratio-based Mapping                    |

|              | 6.3.2   | Kernel Graph Structure Considerations                                    |

|              | 6.3.3   | Data Partitioning                                                        |

| 6.4          | Implen  | nentation and Evaluation                                                 |

|              | 6.4.1   | Implementation                                                           |

|              | 6.4.2   | Experimental Setup                                                       |

|              | 6.4.3   | Results                                                                  |

| 6.5          | Summa   | ary                                                                      |

| CHAPT<br>GPU |         | EXPLORING COMPUTATION AND DATA REDUNDANCY VIA PARTIAL UTING RESULT REUSE |

| 7.1          | Case S  | tudy                                                                     |

| 7.2          | CDITE   | Nacion 116                                                               |

|        | 7.2.1          | Overview                          |

|--------|----------------|-----------------------------------|

|        | 7.2.2          | Methodology                       |

|        | 7.2.3          | GRU Front-End                     |

|        | 7.2.4          | GRU Back-End                      |

| 7.3    | Implen         | nentation Details                 |

|        | 7.3.1          | Rewriting Algorithm               |

|        | 7.3.2          | Result Cache and Reuse            |

|        | 7.3.3          | Global object tracking            |

|        | 7.3.4          | Delay transfer                    |

| 7.4    | Evalua         | tion                              |

|        | 7.4.1          | Experimental Setup                |

|        | 7.4.2          | Spark Use Cases                   |

|        | 7.4.3          | Experiments with Micro-benchmarks |

| 7.5    | Related        | d Work                            |

| 7.6    | Summa          | ary                               |

| CHAPT  | ER 8           | CONCLUSION                        |

| REFERI | ENCES          |                                   |

| BIOGRA | APHIC <i>A</i> | AL SKETCH                         |

| CHRRIC | אוו וווי       | VITAE                             |

# LIST OF FIGURES

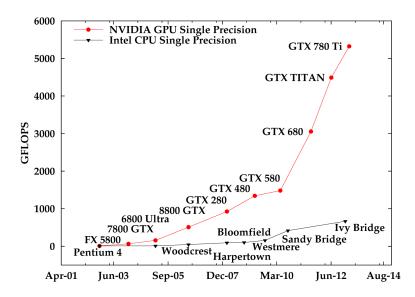

| 1.1  | Historical trends of CPU and GPU performance in GFLOPS                                                                                                                                       | 4  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

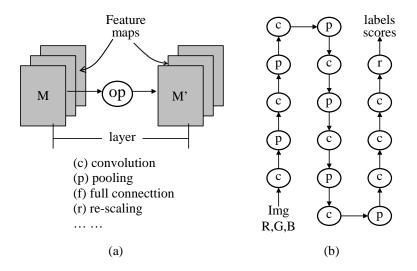

| 1.2  | (a) DNN layers are essentially array-based computations operated on lists of arrays often called feature maps. (b) A state-of-the-art DNN for object recognition, formed by connected layers | 8  |

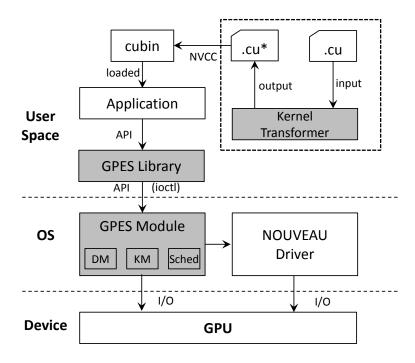

| 3.1  | GPES framework                                                                                                                                                                               | 22 |

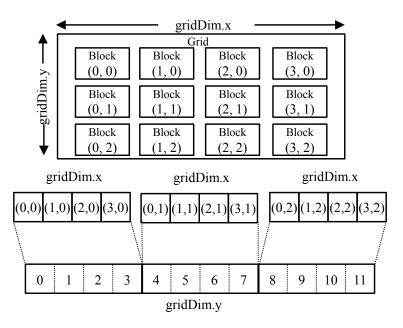

| 3.2  | A two dimensional grid is flattened to one dimension                                                                                                                                         | 24 |

| 3.3  | Kernel code transformation                                                                                                                                                                   | 25 |

|      |                                                                                                                                                                                              |    |

| 3.4  | Changes in GPU SASS due to kernel transformation                                                                                                                                             | 28 |

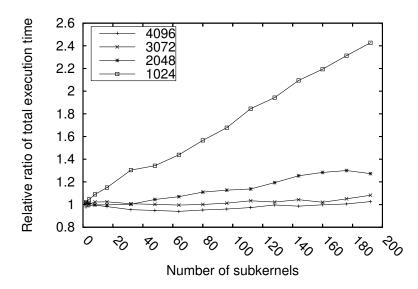

| 3.5  | Relationship between execution time and number of subkernels                                                                                                                                 | 32 |

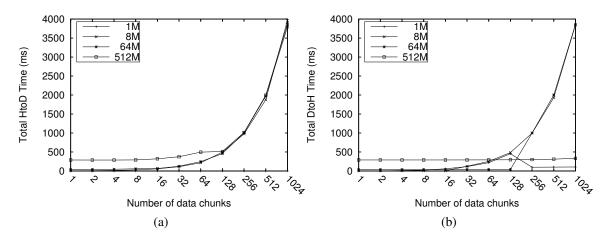

| 3.6  | Relationship between memory-copy time and number of chunks. (a) Host to device (b) Device to host                                                                                            | 34 |

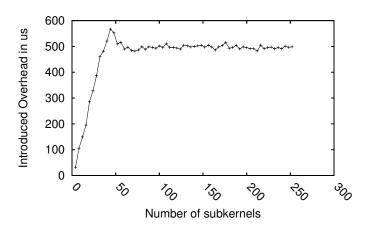

| 3.7  | Additional context switch overhead via kernel execution slicing                                                                                                                              | 35 |

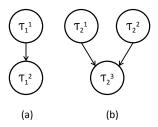

| 3.8  | Impact of kernel execution slicing. (a) Single kernel (b) Dependent kernels                                                                                                                  | 37 |

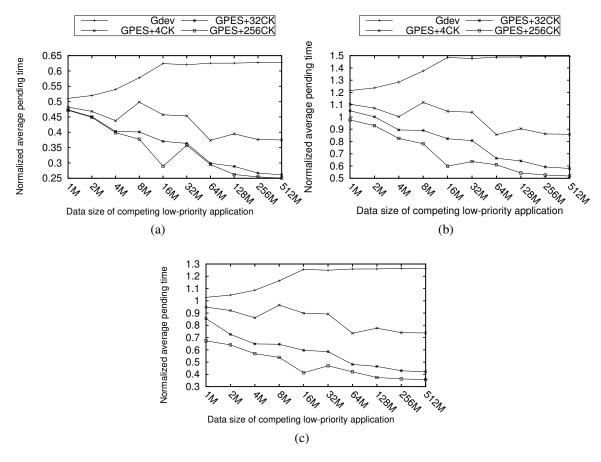

| 3.9  | Impact of data slicing (a) Computation-intensive (b) Data-intensive (c) Mixed                                                                                                                | 39 |

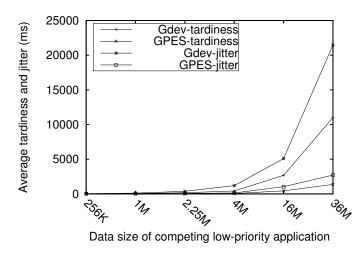

| 3.10 | Jitter and tardiness of image processing case under Gdev and GPES                                                                                                                            | 40 |

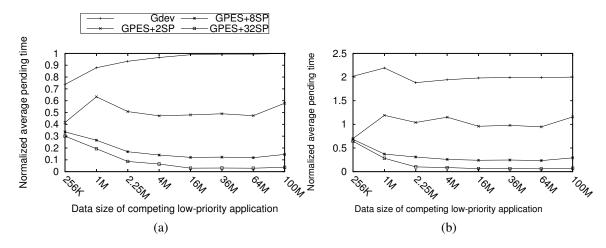

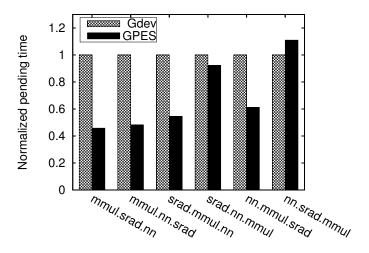

| 3.11 | Normalized pending time under Gdev and GPES                                                                                                                                                  | 41 |

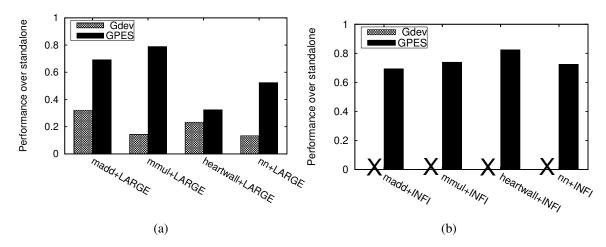

| 3.12 | Defending against malicious applications (a) LARGE (b) INFI. (An 'X' mark means that the normal application does not terminate and the performance cannot be measured.)                      | 42 |

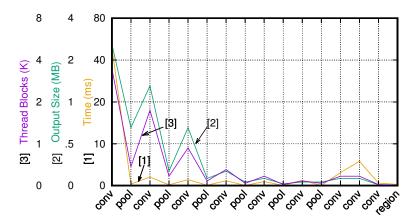

| 4.1  | Resource usage pattern of DNN workloads                                                                                                                                                      | 44 |

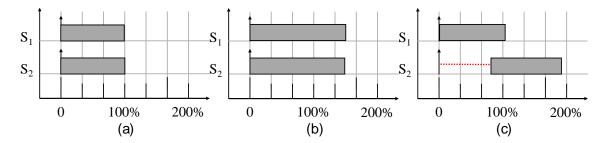

| 4.2  | Execution time of two streamed concurrent Kernels with different numbers of thread blocks: (a) small number (b) medium number (c) large number                                               | 47 |

| 4.3  | Concurrency under CUDA stream without supervised streaming (inset (a)) and with supervised streaming (inset (b))                                                                             | 49 |

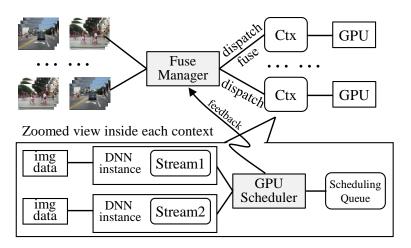

| 4.4  | Design overview of $S^3DNN$                                                                                                                                                                  | 51 |

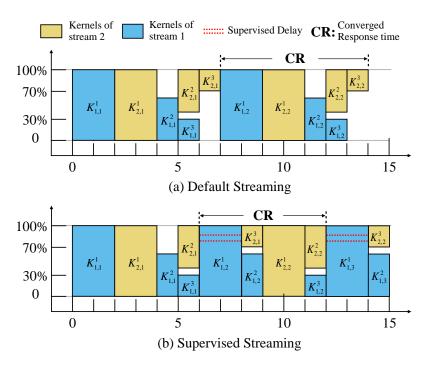

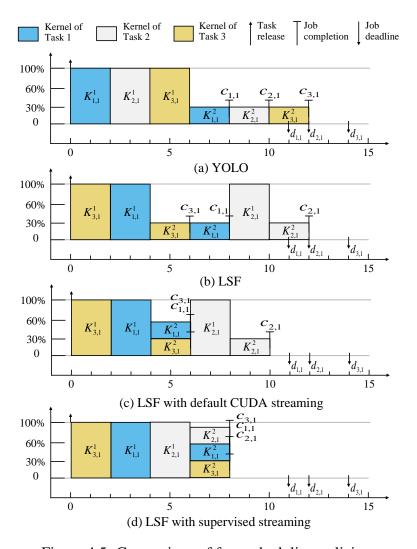

| 4.5  | Comparison of four scheduling policies                                                                                                                                                       | 56 |

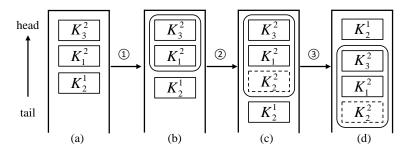

| 4.6  | Intuitive illustration of Algorithm 3 using the example given in Fig. 4.5 (d)                                                                                                                | 60 |

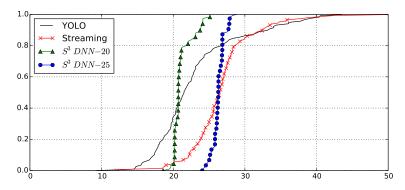

| 4.7  | CDF of FPS under (a) light (b) medium (c) customized DNN configurations. "3-yolo" ("3- $S^3DNN$ ") represents the FPS performance under YOLO ( $S^3DNN$ ) when there are three input vidoes  | 62 |

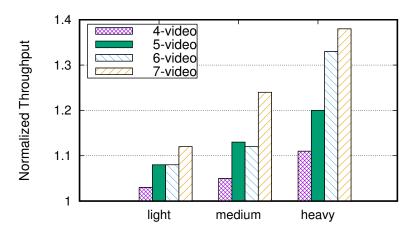

| 4.8  | Normalized throughput under light, medium, and heavy workloads using a variant                                                                                                               |    |

|      | number of videos                                                                                                                                                                             | 66 |

| 4.9  | streaming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\epsilon$ |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.10 | Performance under multi-GPU scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8          |

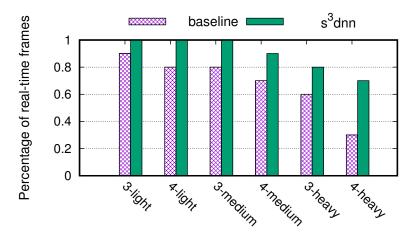

| 4.11 | Percentage of frames that meet their deadlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3          |

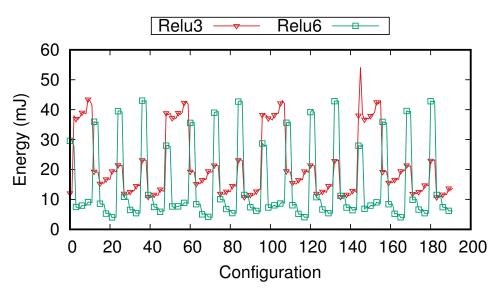

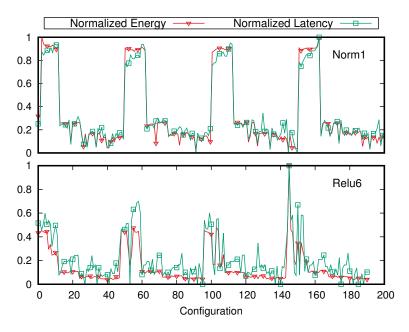

| 5.1  | Energy usage of Relu3 and Relu6 under different DVFS configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2          |

| 5.2  | The trailing effect for two layers. Layer 4 has a pronounced trailing effect while layer 18 does not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2          |

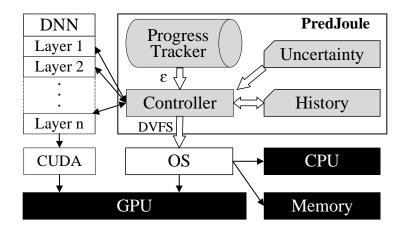

| 5.3  | Design overview of PredJoule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\epsilon$ |

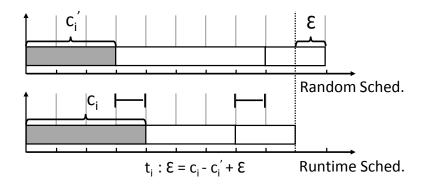

| 5.4  | Example illustration of the progress tracker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C          |

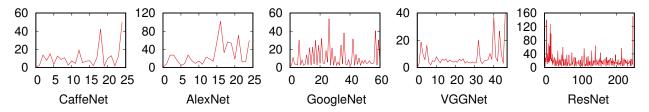

| 5.5  | Uncertainty for various neural networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4          |

| 5.6  | The average energy consumption of all five neural networks with tight / loose deadlines. 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6          |

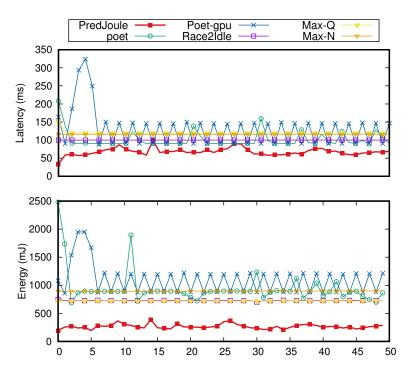

| 5.7  | Energy and latency of PredJoule compared to others for ResNet-100 over 50 iterations. 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8          |

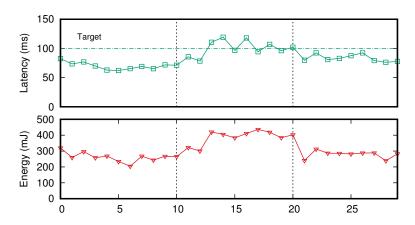

| 5.8  | Energy and latency of PredJoule when interference is present                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C          |

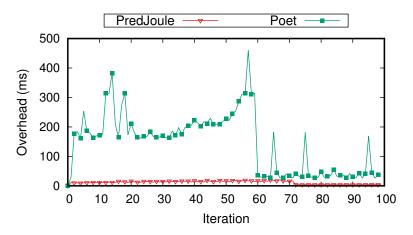

| 5.9  | Overhead of PredJoule vs. Poet for ResNet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1          |

| 6.1  | Kernel dependency graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8          |

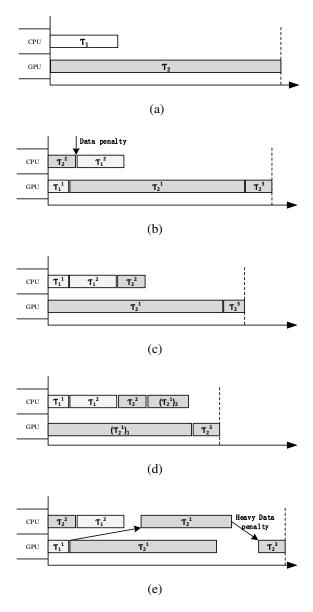

| 6.2  | (a) Application level mapping and (b) Kernel level mapping (c) Different map order (d) Data Partition (e) Bad data partition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ç          |

| 6.3  | Our scheduler implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16         |

| 6.4  | Experimental Hardware Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8          |

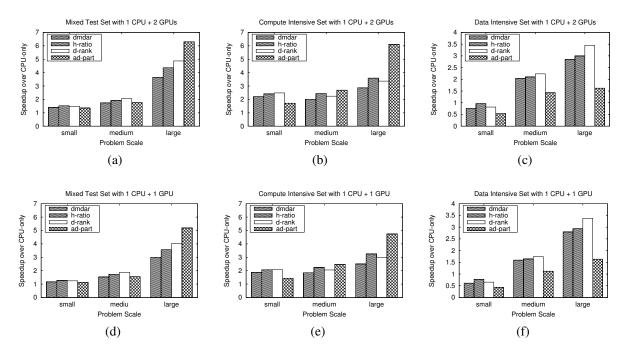

| 6.5  | Experimental results on the competition time. In all six graphs, the <i>x</i> -axis denotes the three tested scenarios where problem size scale is varied to be small, medium, and large (according to Table 6.4). The <i>y</i> -axis denotes the speedup each algorithm achieved upon the naive CPU-only mapping algorithm. Graphs in the first (second) row depict the results under the system configuration with one CPU and two GPUs (one CPU and one GPU). In the first (respectively, second and third) column of graphs, mixed (respectively, computation-intensive and data-intensive) workloads are assumed 10 | )Ç         |

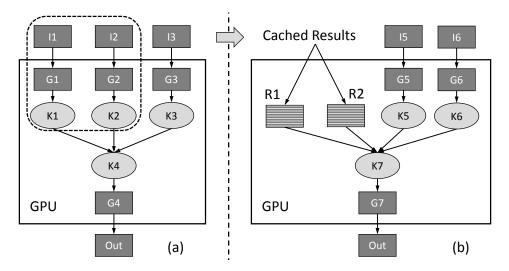

| 7.1  | GRU architecture consists of a rewriter and a library at the front-end, and a back-end service that runs in the cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5          |

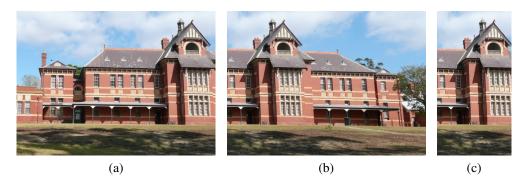

| 7.2  | Two similar images (a) (b) with same tile (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7          |

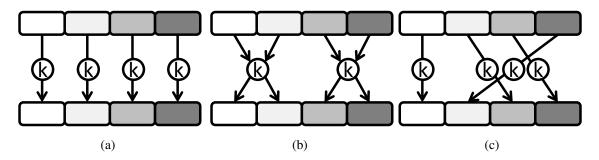

| 7.3  | Three example data parallel patterns: (a) Map (b) Partition (c) Scatter/Gather                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8          |

| 7.4  | Code segment of matrix multiplication program after transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ç          |

| 7.5  | Different functionalities share common sub-computation K1 and K2 that can be reused from previous cached results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21         |

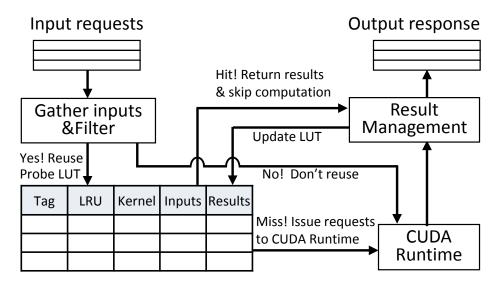

| 7.6  | Workflow of reuse engine                                                                                        |

|------|-----------------------------------------------------------------------------------------------------------------|

| 7.7  | Turnaround time (TAT) and GPU occupancy time (GOT) of three programs on two datasets with GRU off and on        |

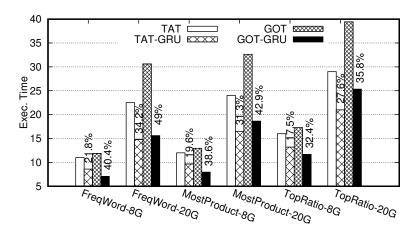

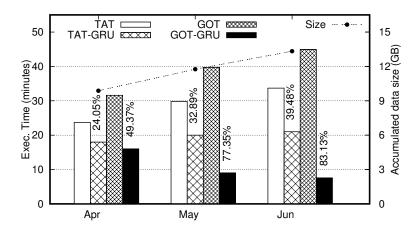

| 7.8  | Cumulative turnaround time and GPU occupancy time savings for opencloud trace dataset                           |

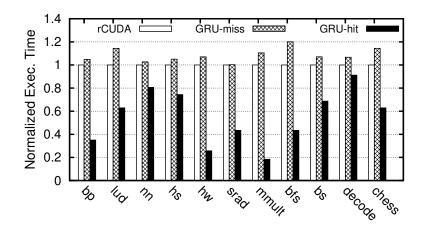

| 7.9  | Performance with respect to normalized execution time                                                           |

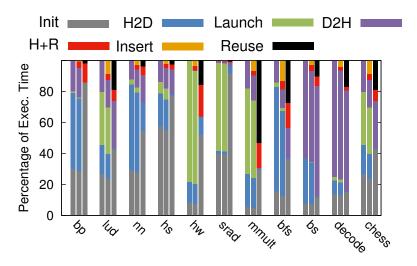

| 7.10 | The three histograms for each benchmark represent the breakdown under rCUDA, GRU-miss and GRU-hit, respectively |

# LIST OF TABLES

| 3.1 | tiplication under the NVIDIA proprietary driver (NV) and the Nouveau open source driver plus the Gdev module (Gdev) |

|-----|---------------------------------------------------------------------------------------------------------------------|

| 3.2 | Benchmarks used in evaluation                                                                                       |

| 4.1 | APT and pMiss of data fusion and base line                                                                          |

| 4.2 | Configuration of video numbers and FPS                                                                              |

| 5.1 | Uncertainty for an example DNN configuration                                                                        |

| 5.2 | Approximate Uncertainty for different layer types at different depths                                               |

| 5.3 | Method deadline misses for various DNNs                                                                             |

| 6.1 | Notation Summary                                                                                                    |

| 6.2 | Execution time of kernels                                                                                           |

| 6.3 | Comparison against IP                                                                                               |

| 6.4 | Benchmarks used in experiments                                                                                      |

| 7.1 | Movie recommendation using GPU-enabled Spark on two movieLens datasets with different partitioning                  |

| 7.2 | Reuse of non-identical data & computation                                                                           |

| 7.3 | Evaluated benchmarks                                                                                                |

#### **CHAPTER 1**

#### INTRODUCTION

Graphics processing units (GPUs) are being widely used as co-processors in many domains to achieve acceleration. They are particularly capable of executing data-parallel applications, due to their highly multi-threaded architecture and high-bandwidth memory. Along with the support of the CUDA (NVIDIA, 2011) programming model developed by NVIDIA, GPUs can be easily used for general-purpose computing in addition to dedicated graphics applications, i.e., GPGPU. Examples include adopting GPGPU to accelerate inherently computation-intensive Deep Neural Network (DNN) workloads.

Deep Neural Network is another very popular technique being widely applied in many autonomous systems for their state-of-the-art, even human-competitive accuracy in cognitive computing. One such domain is autonomous driving, where DNNs are used to map the raw pixels from on-vehicle cameras to the steering control decisions (Chen et al., 2015; NVIDIA, 2016). This DNN-driven approach is powerful because with limited training data from humans, the driving system can learn to drive by itself. Recent end-to-end learning frameworks make it even possible for DNNs to learn to self-steer from limited human driving datasets (Bojarski et al., 2016).

Such autonomous systems are usually time-sensitive, sometimes even need to meet hard real-time constraints (no task should violate its deadline, otherwise the entire system would fail). However, the GPGPU is mainly designed for accelerating particular high-performance applications, which may not be efficiently applicable for GPGPU in real-time multi-tasking environments. Once pieces of GPU-accelerated code, i.e., kernels, from different applications are loaded onto the GPU, they are dispatched by hardware scheduler. Such hardware-based scheduling will harm the response time of high-priority GPGPU tasks, since the hardware scheduler does not consider task priorities. Consequently, due to the asynchronous and non-preemptive nature of GPU processing, in multi-tasking environments, a task with higher priority or urgency (e.g., with a shorter deadline) may be blocked by lower priority tasks that have already started running on GPUs. This severely

harms the system's timing predictability and is a serious impediment limiting the applicability of GPGPU in autonomous systems.

In addition to preemption, the steps that map computations to different processing elements in a CPU-GPU heterogeneous platform is critical. This mapping problem is quite challenging due to a large size of the policy space. First of all, applications may demonstrate (sometimes significantly) different performance characteristics when executed on GPUs than CPUs. The mapping algorithm thus needs to consider such heterogeneity when making prioritization and mapping decisions. Moreover, most real world workloads are implemented using rather complex kernel graphs, where a kernel graph contains a number of data- or logical- dependent kernels. The precedence constraints among kernels require the mapping algorithm to consider: (i) the kernel graph structure and (ii) different data transfer costs among kernels if executed on different processors. Furthermore, for data-intensive kernels, data partitioning techniques need to be incorporated into the mapping algorithm because partitioning a kernel into threads that can be run on multiple devices in parallel improves the overall utilization.

Furthermore, for DNN specific workloads, existing research works focus on exploring the specific features of DNN to improve the single-tasking throughput at the algorithmic level (Redmon et al., 2016; Girshick et al., 2014; Girshick, 2015; Ren et al., 2015). There is a lack of research effort tackling these challenges from the critical system-level optimization perspective: how to optimize the execution of GPU-accelerated DNN workloads at the system level in a real-time multitasking environment. A critical objective is to guarantee real-time performance while maximizing system throughput and resource utilization to mitigate the inherent resource constraint imposed by most embedded hardware.

Last but not least, adopting inherently compute-intensive DNNs in often resource- and energy-constrained automobiles creates another challenge, due to the need of satisfying two (often) conflicting goals: timing predictability and energy efficiency. Timing predictability (i.e., meeting job latency requirement) is one of the most important tenets in certification required for autonomous

driving systems. The functional correctness of an automobile hinges crucially upon temporal correctness (e.g., performing object detection within a strict latency boundary to signal automatic brake requests). On the other hand, automobiles demand low energy consumption, due to their strict size, weight, and power (SWaP) requirements. Regrettably, timing predictability and energy efficiency are often in conflict. This is because the former requires reserving sufficient resources for guaranteeing latency even in the worst case; while the latter often desires allocating just enough resource that barely meets the needs of the current job.

This dissertation seeks to investigate aforementioned challenges of adopting GPU in DNN-driven atonomous systems, aiming at making GPGPU computings timing- and energy- predictable.

#### 1.1 Graphics Processing Units

GPUs were developed for dedicated 2D graphics rendering since 1970s. For two decades of years GPUs were "fixed function" hardware. This changed when the "programmable pipeline" appeared in 2001, which enabled programmers to customize their own rendering codes (namely "shaders") that were executed on the GPU. These successful shader languages include NVIDIAs "C for Graphics" (Cg) (NVIDIA, 2003), and the OpenGL Shading Language (GLSL) (Group, 2004). Empowered by shader languages and programmable GPUs, researchers began to exploit the generality of the programmable pipeline to solve general purpose computations, namely GPGPU (Harris, 2009). Recognizing the potential computational power of GPGPU, generalized languages and easy-to-use runtime environments were developed by major GPU vendors and software producers to allow general purpose programs to be executed on graphics hardware. Notable toolkits include the Compute Unified Device Architecture (NVIDIA, 2011), OpenCL (Group, 2008), and OpenACC (OpenACC, 2013).

Figure 1.1 shows the historical trends of CPU and GPU performance, where the x-axis is the time till August 2014 when this figure is used in the presentation of (Zhou et al., 2015), and the y-axis is the single precision peak performance in terms of billions of floating point operations

Figure 1.1: Historical trends of CPU and GPU performance in GFLOPS.

per second (GFLOPS). We observe that GPUs significantly outperform CPUs since June 2003, and this disparity becomes even larger. For example, NVIDIA's GTX Titan can perform at 4,500 GFLOPS in comparison to 672 GFLOPS for the Intel Ivy Bridge, which is more than 6 times. This performance trend shows the strong motivation of using GPUs to accelerate general purpose computing.

We briefly explain some GPU hardware related terminologies that will be frequently used in the rest of this dissertation.

**MP/SM, SP**: Streaming multiprocessor (MP or SM) is the internal unit of NVIDIA GPU hardware that performs the actual computations. NVIDIA GPU consists of several SMs, each of which is further divided into shader processors (SP). The number of SMs and SPs is product-specific. Lowend GPUs typically have one SM, and high-end GPUs have 15 or 16 SMs. Take NVIDIA GTX 480 for example, which is based on GF110 architecture, it has 15 SMs.

**Channel**: Each GPU context is associated with a GPU hardware channel. Internally, a channel is managed by channel engine which is a subarea of the MMIO (memory-mapped I/O) region. The channel engine maintains the status of GPU contexts including FIFO queues of GPU commands.

Command: Typically the GPU is controlled by the CPU using commands. The operating system and GPU driver maintain GPU *command buffers* which are accessible to both CPU and GPU. The CPU writes commands to them, while the GPU reads the commands from them. There are hundreds of commands defined by the architecture (e.g., Fermi or Kepler). For example, when copy data from the host to the device memory, we send a set of commands to the GPU, specifying the source and the destination virtual addresses together with the mode of direct memory access (DMA). A single GPU command is composed of GPU instructions and the values passed to the instructions. It represents atomicity operation. Commands are usually grouped as non-preemptive regions called *command group*. A tuple of size and command group address forms the packet written to command buffer.

**GPU page table** To enable multi-tasking on GPU, newer versions of GPUs since Fermi architecture (NVIDIA, 2010) support virtual addressing by assigning an address space to each application. An address space is defined by a GPU page table containing entries of mappings between virtual addresses and physical addresses. GPU kernels operate on virtual addresses which are transparently translated to physical addresses by a dedicated memory management unit (MMU). GPU page table is located in the PCI configurable space, which is accessible from both CPUs and GPUs.

**GPU Memory Hierarchy** To improve system throughput, NVIDIA GPUs typically feature several memory spaces and memory types. According to CUDA specifications, there are eight logical types of GPU memory and cache space.

**Global memory** GPU global memory is the largest area visible to all threads within the application (including the host), which is used to store input and output bulky data for GPU computations. The spatial isolation of global memory is managed by NVIDA proprietary driver which prevents a global memory object that belongs to one context from being accessed by another context.

**Shared memory (or SMEM)** GPU shared memory is a small yet fast memory type that resides on each SM. It can be directly operated by the GPU kernel code. It is visible to all threads within the same thread block. Its life duration is the same as the currently executing thread block while it is

flushed by GPU hardware only when the current context is destructed. It does not have any spatial isolation, which implies that data residuals on the SMEM can be accessed by other thread blocks within the same kernel or from different kernels.

**L1 cache** For each SM, there is a high speed cache named L1 cache, which is used for global memory load caching. It cannot be directly operated by GPU kernel code. However, in some GPU architectures (e.g., Fermi, Kepler), L1 cache and shared memory physically share the same hardware resources, making L1 cache readable by crafted GPU kernel code.

**Local Memory** GPU local memory is not a physical type of memory, but an abstraction of global memory, which is only used to hold automatic variables. Its scope is local to the thread and it resides off-chip.

**Register** GPU registers represent the fastest yet the smallest memory on GPU. As a rare resource, register pressure may severely detract performance. Register pressure occurs when there are not enough registers available for a given kernel. When this occurs, the data is "spilled over" using local memory.

#### 1.2 GPGPU Programming Model

GPGPU applications typically obey the following execution flow: (i) initializing the GPU device, (ii) allocating GPU device memory, (iii) transferring data from host memory to device memory, (iv) launching the computation work (kernel) on GPU, (v) copying results back to host memory, and (vi) freeing device memory and closing the device. We highlight some CUDA specific conceptual terminologies that will be frequently used in the rest of this dissertation.

**Context**: Context conceptually represents separate virtual address spaces on the GPU hardware. A context is either transparently or explicitly created for a CUDA application at the GPU device initialization stage. NVIDIA has provided the MPS (Multi-Process Service) feature in newer versions of CUDA to transparently merge multi-process CUDA applications into one context. However, the usage of MPS is limited by operating system (only supports Linux-based system), applications

(only supports 64-bit applications), GPU hardware (compute capability 3.5 or higher), and special configuration (set GPU to be exclusive to other processes). Moreover, MPS fails to consider DNN-specific characteristics since it is an application-oblivious approach and will blindly combine all of the processes assigned to it. In this dissertation, we assume a more common scenario, where different CUDA applications run on different contexts.

Thread, Warp, Block, Grid: The NVIDIA CUDA (NVIDIA, 2011) programming model consists of four levels of hierarchy. In Fermi or Kepler (NVIDIA, 2014) architecture, 32 threads make up a warp. Warps are the basic units of execution on the GPU. Threads in each warp are executed together. A group of warps stitch together to form a block. These blocks are combined to form a grid. A grid is corresponding to an execution kernel, thus in the rest of this dissertation, kernel launch and grid launch are interchangeable forms. When executing a kernel, the corresponding entire grid is mapped to one GPU device, blocks are mapped to SMs (MPs), and internally, computations are scheduled warp by warp. Notice that, in Fermi and Kepler architectures, grids from different kernels can execute on the same GPU device simultaneously, which is so called concurrent kernels. But such grids (kernels) must come from the same context. In CUDA programming, the programmer can control the number of threads within a block and the number of blocks within a grid.

CUDA stream: CUDA stream is a technique introduced by a newer version of CUDA (NVIDIA, 2015), which aims to hide the latency of memory copy and kernel launch from different independent operations. Its additional effect is the capability of enabling concurrent kernel execution which allows multiple kernels to execute on the same GPU simultaneously when each kernel cannot fully utilize the entire GPU device. A CUDA stream can be explicitly created by the programmer and bound to a kernel launch or data copy operation. To avoid confusion with data stream/video stream, when we talk about this technique, we use the term CUDA stream.

Figure 1.2: (a) DNN layers are essentially array-based computations operated on lists of arrays often called feature maps. (b) A state-of-the-art DNN for object recognition, formed by connected layers.

## 1.3 Deep Neural Networks

A DNN can be viewed as a dataflow graph, in which its nodes, or layers, are essentially array-based computations (as shown in Fig. 1.2(a)) (Redmon et al., 2016). Each layer takes a set of arrays, called *feature maps* as input and outputs a set of feature maps that will in turn be processed by subsequent layers belonging to the same DNN instance. Fig. 1.2(b) shows an illustration of a set of DNN layers used in YOLO (Redmon et al., 2016), which is a popular DNN framework aimed at real-time object detection. The letter within each cycle denotes the functionality performed by the corresponding layer: 'c' for convolution layer which convolves inputs by a convolution filter, 'p' for a max pooling layer which replaces each input array value by the maximum of its neighbors, 'f' for a fully connected layer which multiplies the feature maps by a weight matrix, and 'r' for a region layer, which is a layer specific to YOLO that is responsible for finding areas of interest in an image. In order to use a DNN for object detection, a pre-trained weight file is needed which is estimated from training data beforehand. Training an accurate weight file is an offline procedure that usually takes several days or weeks, done by "learning" features from large-scale

image datasets. In this dissertation, we are not concerned with improving the training process, rather, we focus on efficient execution of DNNs for real-time object detection.

DNN in Autonomous Driving. An autonomous driving system captures surrounding environmental data via multiple sensors (e.g., camera, Radar, Lidar) as inputs, processes these data with DNNs and outputs control decisions (e.g., steering). In this dissertation, we mainly focus on the steering angle component with camera inputs and steering angle outputs, as adopted in NVIDIA Dave (Bojarski et al., 2016). Convolutional Neural Network (CNN), which is efficient at analyzing visual imagery, is the most widely used DNN for steering angle decisions. Similar to regular neural networks, CNNs are composed of multiple layers and pass information through layers in a feed-forward way. Among all layers, the convolutional layer is a key component in CNNs, which performs convolution with kernels on the output of previous layers and sends the feature maps to successor layers. Different from another widely used DNN architecture – Recurrent Neural Networks (RNNs) which is a kind of neural network with feedback connections, CNN-based steering model makes steering decisions based only on the currently captured image. In the dissertation, we use DNN to represent both CNN and RNN without explicitly differentiating them.

#### 1.4 Contributions

We now present an overview of the contributions of this dissertation that support this thesis.

• Making GPU execution (partially) preemptive. We present an efficient GPGPU preemptive execution system (GPES), which combines user-level and driver-level runtime engines to reduce the pending time of high-priority GPGPU tasks that may be blocked by long-freezing low-priority competing workloads. GPES automatically slices a long-running kernel execution into multiple subkernel launches and splits data transaction into multiple chunks at user-level, then inserts preemption points between subkernel launches and memory-copy operations at driver-level. We implement a prototype of GPES, and use real-world benchmarks

and case studies for evaluation. Experimental results demonstrate that GPES is able to reduce the pending time of high-priority tasks in a multi-tasking environment by up to 90% over the existing GPU driver solutions, while introducing small overheads.

- Improving real-time performance of DNN workloads in real-time multi-tasking environment. We propose  $S^3DNN$ , a system solution that optimizes the execution of DNN workloads on GPU in a real-time multi-tasking environment, which simultaneously optimizes the two (sometimes) conflicting goals of real-time correctness and throughput.  $S^3DNN$  contains a governor that selectively gathers system-wide DNN requests to perform smart data fusion, and a novel supervised streaming and scheduling framework that combines a deadline-aware scheduler with the concurrency-enabled CUDA stream technique. To simultaneously maximize concurrency-induced benefits and real-time performance,  $S^3DNN$  explores a rather interesting and unique characteristic of DNN workloads, where multiple layers of a DNN instance often exhibit a gradually decreased GPU resource utilization pattern. We have fully implemented  $S^3DNN$  in a GPU-accelerated system and have conducted extensive sets of experiments evaluating the efficacy of  $S^3DNN$  under a wide range of system and workload scenarios. The results show that  $S^3DNN$  significantly improves upon state-of-the-art GPU-accelerated DNN processing frameworks, e.g., up to 37% and over 40% improvements in real-time performance and throughput, respectively.

- Optimizing energy efficiency of DNN workloads while meeting timeliness. We propose PredJoule, a timing-predictable energy optimization framework for running DNN workloads in a GPU-enabled automotive system. PredJoule achieves both latency guarantees and energy efficiency through a layer-aware design that explores specific performance and energy characteristics of different layers within the same neural network. We implement and evaluate PredJoule on the automotive-specific NVIDIA Jetson TX2 platform for five state-of-theart DNN models with both high and low variance latency requirements. Experiments show

that PredJoule rarely violates job deadlines, and can improve energy by 65% on average compared to five existing approaches and 68% compared to an energy-oriented approach.

- Improving throughput of multiple graph-struct applications by novel heterogeneous task mapping. We investigate the problem of computation and data mapping for multiple applications while minimizing the completion time in GPU-CPU heterogeneous systems, by presenting a theoretical framework that yields an optimal integer programming solution. Moreover, based upon several interesting measurements-based case studies, we design three practical mapping algorithms with low time complexity, each of which explores a specific set of factors that may affect the completion time performance. We evaluated the proposed algorithms by implementing them on a real heterogeneous system and using a large set of popular benchmarks for evaluation. Experimental results demonstrate that our proposed algorithms can achieve up to 30% faster completion time compared to the state-of-the-art mapping techniques, and can perform consistently well across different workloads.

- Improving throughput of clusters by reusing GPU computation results. We present GRU, an ecosystem that smartly manages and shares GPU resources through exploiting redundancy. GRU transparently interprets GPU-accelerated computing requests and memoizes results for potential future reuse. To enhance reusability, GRU implements a partial result reuse idea, where GPU computation requests even with different input data and functionality may become reusable with respect to each other. To guarantee correctness of partial reuse, GRU employs a compiler-assisted approach that analyzes general data parallel patterns that are reliable for the reuse purpose, and is capable of smartly recognizing such reusable data parallel patterns of incoming requests. We have fully implemented GRU and conducted extensive sets of experiments running micro-benchmarks on local machines and real-world applications including Spark-based uses cases in an AWS cluster. Evaluation results show that GRU is effective in identifying and eliminating redundant GPU computations, achieving up to 5x (2.5x) speedup for compute-intensive (data-intensive) benchmarks. In addition,

GPU-managed Spark observes a reduction of 25.3% (39.8%) on average with respect to turnaround time (GPU occupation time) over state-of-the-art solutions.

#### 1.5 Organization

The rest of this dissertation is organized as follows. In Chapter 2, we discuss several background topics, and prior work on predictable GPGPU scheduling in autonomous systems. In Chapter 3, we describe the design, implementation, and evaluation of our preemptive GPU execution framework, GPES. In Chapter 4, we present  $S^3DNN-$  a systemic solution that optimizes the execution of DNN workloads on GPU in a real-time multi-tasking environment. In Chapter 5, we presents PredJoule, a timing-predictable energy optimization framework for running DNN workloads in a GPU-enabled automotive system, which presents a layer-based approach that controls the timing and optimizes energy efficiency through exploiting each layer's performance/energy characteristics. In Chapter 6, we investigate the problem of mapping multiple applications implemented using kernel graphs in a heterogeneous system consisting of CPUs and GPUs, in order to achieve fast competition time. In Chapter 7, we present GRU, a GPU sharing, result memoization and reuse ecosystem for high performance and cloud computing, in order to further improve the predictability of GPU computing. We end in Chapter 8 with concluding remarks and a discussion of future work.

#### **CHAPTER 2**

#### BACKGROUND AND RELATED WORK

#### 2.1 Scheduling Algorithms for Heterogeneous Systems

The general problem of scheduling in heterogeneous systems has received much attention. A number of scheduling heuristics have been proposed for scheduling directed acyclic graph-based (DAG) applications in heterogeneous systems (Topcuouglu et al., 2002; Bittencourt et al., 2010; Zhao and Sakellariou, 2003; Arabnejad and Barbosa, 2014; Sakellariou and Zhao, 2004; Canon et al., 2008). These algorithms schedule a single DAG (Directed Acyclic Graph) of tasks onto heterogeneous processing units with varying speed for minimizing the completion time. Zhao et.(Zhao and Sakellariou, 2006) proposed multi-DAG scheduling by merging multiple DAGs into one DAG. However, such algorithms do not specifically target the CPU/GPU platform, and thus ignore several critical factors when making scheduling decisions, including non-preemptivity, data transfer cost among CPUs and GPUs, data partitioning. Moreover, these existing algorithms are mostly greedy in nature and do not provide a theoretical understanding of the mapping problem considered herein. Furthermore, such algorithms use simulation-based evaluation approach and have not been tested in real systems.

#### 2.2 Runtime Engines for Heterogeneous CPU/GPU Processors

For heterogeneous CPU/GPU platforms, a number of runtime systems have been developed to perform task scheduling. PTask (Rossbach et al., 2011) focuses on eliminating performance interference of GPU sharing. TimeGraph (Kato et al., 2011) and others (Verner et al., 2011) provides prioritization and isolation capabilities in GPU resource management. Harmony (Diamos and Yalamanchili, 2008) schedules translated CUDA code on various devices. Qilin (Luk et al., 2009) provides an adaptive mapping to automatically partition tasks on a CPU and a GPU. SKMD (Lee

et al., 2013) transparently translates single OpenCL (Group, 2008) kernel into variations and executes them on multiple GPUs simultaneously. The aforementionned runtime systems either focus on single kernel or do not consider kernel affinities. Some other runtime systems focus on task dataflow parallelism: OmpSs (Bueno et al., 2011), DirectShow (Linetsky, 2001), Hydra (Weinsberg et al., 2008), StreamIt (Thies et al., 2002), IDEA (Currey et al., 2013), Liquid Metal (Huang et al., 2008), Lime (Auerbach et al., 2010). However, these systems do not focus on scheduling multiple graphs onto heterogeneous processors for minimizing the completion time.

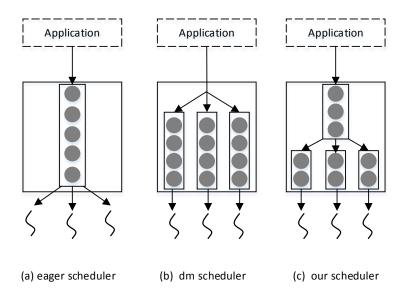

The StarPU (Augonnet, Thibault, Namyst, and Wacrenier, Augonnet et al.) runtime system provides programmers with a portable interface for dynamically mapping tasks onto heterogeneous processors (CPUs and GPUs). It integrates development tuning and sampling with several predefined task scheduling strategies (National institute for research in computer science and control, 2008) as plugins. These include the eager scheduler that uses the minimum-completion-timefirst policy (Topcuouglu et al., 2002), the dm scheduler that performs an HEFT-based scheduling policy, and several variations of the dm scheduler. Among all pre-defined schedulers, the best one is the dmdar (deque model data aware ready) scheduler. The dmdar scheduler is similar to the dm scheduler, but takes data transfer time into account and sorts tasks on a per-worker queue basis. Sc\_hypervisor (Hugo et al., 2013) is an extension based on StarPU, which supports co-execution of multiple applications each using the StarPU runtime system. It focuses on partitioning approaches, which split computing resources into isolated sets, and then apply existing StarPU schedulers on each set. However, the StarPU runtime system does not focus on designing efficient mapping algorithms to minimize the completion time, but rather contributes in providing a portable interface for programmers to easily utilize GPUs. The StarPU pre-defined schedulers are mainly designed to handle the single application scenario and use simplified criterion to make mapping decisions.

#### 2.3 GPU Resource Management

A number of runtime systems have been developed to perform GPU task scheduling. Qilin (Luk et al., 2009) provides an adaptive mapping to automatically partition tasks on a CPU and a GPU. StarPU (Augonnet, Thibault, Namyst, and Wacrenier, Augonnet et al.) runtime system provides programmers with a portable interface for dynamically mapping tasks onto heterogeneous processors (CPUs and GPUs). The aforementioned runtime systems are implemented at user-level and focus on heterogeneous systems without considering interference among multiple applications on the same GPU.

PTask (Rossbach et al., 2011) focuses on eliminating performance interference of GPU sharing. TimeGraph Kato et al. (2011) and Gdev (Kato et al., 2012) provide prioritization and isolation capabilities in GPU resource management. GDM (Wang et al., 2014) enhances GPU memory management by introducing a staging area in host memory for each process. These works are implemented at OS-level, and also propose scheduling algorithms for different applications sharing GPU resources. Specifically, Gdev and Timegraph make enhancements on kernel scheduling between contending applications. However, they can not handle the priority inversions caused by long-running or non-terminating kernels. Furthermore, GPES utilizes different interrupt schema compared to these work. More detailed differences between GPES and Gdev and TimeGraph are described in Sec. 3.2.3.

RGEM Kato et al. (2011) and PKM (Basaran and Kang, 2012) are two GPGPU engines which provide responsive and preemptive support for GPGPU tasks in a multi-tasking environment. However, they are implemented at user-level, thus lacking the view of the whole operating system. Moreover, in order to utilize their engine, GPGPU applications are required to be rewritten with the interfaces they provide. This may put much burden on end-programmers. Also, they have to know all applications before hand and then compile them into one single process, which does not reflect a real multi-tasking environment with dynamically coming applications. In contrast, GPES

does not need the source code of GPGPU applications. Also, it can transparently provide preemption and prioritization support for dynamically coming applications. To the best of our knowledge, GPES is the first piece of work which supports preemptive computation and memory-copying in a practical multi-tasking environment.

#### 2.4 Real-time DNN-Based Object Recognition

DNNs have been extensively adopted in object detection for their impressive improvements in detection accuracy (Krizhevsky et al., 2012; Jia et al., 2014), which is the core function of many image/video processing applications. With GPU-accelerated platforms, DNN-based object recognition is now capable of processing vision workloads in real-time, either through algorithmic optimization (Redmon et al., 2016; Girshick et al., 2014; Girshick, 2015; Ren et al., 2015), or trading throughput with accuracy (Chen et al., 2015a; Han et al., 2016).

#### 2.5 Optimizing Energy While Meeting Timeliness

The problem of optimizing energy while meeting hard or soft real-time constraints has received much attention in the literature (Farrell and Hoffmann, 2016; Hoffmann, 2015; Baek and Chilimbi, 2010; Sorber et al., 2007; Bini et al., 2009; Dudani et al., 2002; Heo et al., 2011; Huang et al., 2009; Imes et al., 2015; Hoffmann, 2014; Mishra et al., 2015). Despite various manipulation mechanisms in detail, these works mostly study simplified workload models (e.g., the well-studied sporadic independent task model (Mok, 1983) or approximate applications where accuracy can be traded for performance and/or energy).

A recent set of works (Farrell and Hoffmann, 2016; Hoffmann, 2015) have been proposed to explore the specific domain of approximate applications, where accuracy can be exploited for trading performance and energy. For instance, MEANTIME (Farrell and Hoffmann, 2016) seeks to minimize energy consumption while achieving timing predictability, with the core idea of trading

off accuracy for meeting deadlines. Other works such as Green (Baek and Chilimbi, 2010) and Eon (Sorber et al., 2007) seek to tailor behavior online to balance between accuracy and energy goals. CoAdapt (Hoffmann, 2014) allows users to prioritize two out of three goals in terms of performance, power, and accuracy, which then provides soft guarantees in those two prioritized dimensions while optimizing the third.

State-of-the-art research on optimizing energy efficiency for DNNs can be categorized into three categories: hardware approaches, DNN model optimization, and runtime approaches. Hardware approaches aim to optimize basic computations used in DNNs (e.g., convolution, matrix multiplication) (Chen et al., 2016; Han et al., 2016; Umuroglu et al., 2017; LiKamWa et al., 2016; Reagen et al., 2016; Chi et al., 2016; Shafiee et al., 2016; Albericio et al., 2016) through developing efficient hardware acceleration solutions. Model optimization approaches seek to compress or prune DNN models prior to execution (Han et al., 2015; Yang et al., 2017; Jaderberg et al., 2014; Kim et al., 2015; Romero et al., 2014; Xue et al., 2014; Chen et al., 2015; Han et al., 2015). Runtime approaches include offloading partial or entire DNN workloads to remote servers (Kang et al., 2017; Huynh et al., 2017; Bhattacharya and Lane, 2016; Chen et al., 2015b; Xu et al., 2017), and performing runtime approximation which trades performance with accuracy (Lane et al., 2016; Han et al., 2016). To the best of our knowledge, none of these works simultaneously consider timing correctness and energy efficiency by using native DVFS.

Different from all these works on optimizing latency and energy efficiency, PredJoule represents a system solution that can achieve timing predictability while minimizing energy for running DNN workloads. A unique contribution of PredJoule is to explore dramatically different performance/energy characteristics of DNNs through developing a layer-based approach. This allows the system to smartly identify the best configuration for running each layer, such that timing can be tightly controlled on a per-layer basis while achieving the most energy saving by considering each layer's performance/energy characteristics.

#### 2.6 Kernel Transformation

Lee et al. propose SKMD (Lee et al., 2013) which transparently translates a single OpenCL (Group, 2008) kernel into variations and executes them on multiple GPUs simultaneously. Elastic Kernel (Pai et al., 2013) rewrites the kernel source code and reshapes the Kernel Grid to use N:1 logical-to-physical mapping scheme. We implement kernel source transformation to slice a kernel into multiple subkernels and share the same idea of flattening workgroups as SKMD, but the goal of our technique is fundamentally different from those techniques: SKMD transforms kernels to distribute the workloads of a single kernel on multiple devices; Elastic Kernel uses kernel transformation to enable concurrent execution of different kernels; whereas we slice kernels to make the long-running kernel interruptible for better preemption. Furthermore, the source-to-source transformation technique is just a small (optional) part of our system, because we implement a novel and better kernel code rewriting technique as an alternative.

## 2.7 Managing GPUs in The Cloud

Current approaches for GPU management in the cloud are classified into I/O pass-through (AMAZON, 2006), API-remoting (Duato et al., 2010; Giunta et al., 2010; Lagar-Cavilla et al., 2007; Shi et al., 2012), para-virtualization (Dowty and Sugerman, 2009; Gottschlag et al., 2013; Suzuki et al., 2014) and full-virtualization (Suzuki et al., 2014; Tian et al., 2014; Malka et al., 2015; Zhou et al., 2015), the latter two being two different implementations of the device emulation technique. However, these works do not exploit the idea of GPU computing result reuse.

#### 2.8 Computing Result Reuse

The concept of CPU-based computation reuse has been proposed in the programming language and computer architecture communities. Compiler-assisted approaches (Sodani and Sohi, 1997;

Conners and Hwu, 1999; Connors et al., 2000; Ding and Li, 2004) seek to reuse intermediate results at CPU instruction level. Function-level memoization (Michie, 1968; Pugh and Teitelbaum, 1989) is used to avoid re-executing functions by caching the results of prior function calls. Moreover, frameworks are proposed to reuse redundant computations at a higher level for the emerging incremental data processing field. For example, Spark (Zaharia et al., 2010), Percolator (Peng and Dabek, 2010), and CBP (Logothetis et al., 2010) provide programmers with facilities to store and reuse states across successive runs; while DryadInc (Popa et al., 2009), Nectar (Gunda et al., 2010), Haloop (Bu et al., 2010), Incoop (Bhatotia et al., 2011), CIEL (Murray et al., 2011), and Shredder (Bhatotia et al., 2012) are systems that reuse prior computing results. On GPU-incurred reuse, Arnau et al. (Arnau et al., 2014) presented a hardware memoization approach to eliminate redundant fragment shader executions on a mobile GPU. Different from these works, PredJoule focuses on GPGPU and efficiently realizing the partial GPU computing result reuse idea at a GPU kernel launch granularity.

#### **CHAPTER 3**

#### PREEMPTIVE EXECUTION FOR GPGPU<sup>1</sup>

#### 3.1 A Case Study

Due to the asynchronous and non-preemptive nature of GPU processing, in multi-tasking environments, tasks with high priorities may be blocked by low-priority tasks. Such priority inversions may occur due to either kernel execution blocking or data transfer blocking. In a real-time system, this may cause deadline misses.

We conduct a measurements-based case study to show the impact of the non-preemptive kernel execution and data transfer blocking on real applications in practice, using two best available GPGPU drivers in a multi-tasking environment: the NVIDIA proprietary driver (NVIDIA, 2011), and the Nouveau open source driver (FREEDESKTOP, 2012) plus Gdev (Kato et al., 2012) which is a GPGPU run-time and resource management engine that manages GPUs as first-class computing resources. We measure the performance of running a video processing application heartwall (Che et al., 2009) competing with mmul (matrix multiplication). Heartwall processes a medical video frame by frame. A single frame processing consists of a memory-copying operation and a kernel launch. We assign the highest CPU priority to the heartwall application by viewing it as a high priority task, and assign low CPU priority to the mmul application as low priority task. The average processing time (memory-copy and kernel launch) of single iteration in heartwall is 380ms. It is set to execute periodically at an interval of 500ms. Mmul has variable processing time depending on its data size. It is configured to execute repeatedly with three sizes: small (256KB), medium (4MB) and large (16MB). Each combination executes for 500 seconds in total to impose high workloads on the entire system. We report the relative jitter and tardiness in the same manner

<sup>&</sup>lt;sup>1</sup>©2015 IEEE. Reprinted, with permission, from Husheng Zhou, Guangmo Tong, and Cong Liu. "GPES: A Preemptive Execution System for GPGPU Computing", In Proceedings of the 21st IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS15). DOI:10.1109/RTAS.2015.7108420

Table 3.1: Jitter and tardiness of video processing application when competing with matrix multiplication under the NVIDIA proprietary driver (NV) and the Nouveau open source driver plus the Gdev module (Gdev)

|                | small      | medium     | large       |

|----------------|------------|------------|-------------|

| NV tardiness   | 1169.64 ms | 4387.7 ms  | 6130.77 ms  |

| NV jitter      | 1188.13 ms | 4523.22 ms | 6483.90 ms  |

| Gdev tardiness | 426.24 ms  | 2678.97 ms | 6726.78 ms  |

| Gdev jitter    | 1197.11 ms | 5095.33 ms | 12705.99 ms |

as (Kenna et al., 2011). Jitter is the deviation from the true periodicity of a periodic frame play-back, which quantifies the smoothness of a video. If a frame i starts displaying at time  $t_i$  and the actual period between two frames is p, then its relative jitter is  $|t_i - (t_{i-1} + p)|$ . Tardiness represents the delay of completion.

As listed in Table 3.1, the jitter and tardiness on both drivers are significant, particularly when competing against *mmul* application with large data sizes. It is clear from this case study that current existing GPGPU drivers lack mechanism to make high-priority tasks preemptive when competing with long-freezing low-priority tasks. This lack of support motivates us to develop GPES, as described next.

#### 3.2 System Design and Implementation

In this section we present the design and implementation of GPES, which aims to make tasks on GPU more preemptive and interruptible in multi-tasking environments. We implement GPES based on Gdev (Kato et al., 2012) which is open-source and publicly available. The software stack of GPES consists of a kernel transformer, a user-space library and an OS module. As depicted in Fig. 3.1, the shadowed rectangles represent the components of GPES. The kernel transformer performs automatic source-to-source transformation to kernel source code. The GPES library is a wrapper of driver APIs and provides CUDA API interfaces, where kernel execution slicing and data slicing are implemented. These two components are implemented at user space. The GPES

Figure 3.1: GPES framework

module performs the actual functionality of memory-copy, kernel launch, scheduling, and interrupt handling. GPES module is implemented at OS space.