# DESIGN APPROACHES FOR ENHANCING PHOTOVOLTAIC PERFORMANCE OF SILICON SOLAR CELLS SENSITIZED BY PROXIMAL NANOCRYSTALLINE QUANTUM DOTS

by

Natis Shafiq

| APPROVED BY SUPERVISORY COMMITTEE: |

|------------------------------------|

|                                    |

|                                    |

|                                    |

| Yves J. Chabal, Chair              |

|                                    |

|                                    |

| Jiyoung Kim                        |

|                                    |

|                                    |

| Anton V. Malko                     |

|                                    |

|                                    |

|                                    |

| Chadwin D. Young                   |

Copyright 2017

Natis Shafiq

All Rights Reserved

# DESIGN APPROACHES FOR ENHANCING PHOTOVOLTAIC PERFORMANCE OF SILICON SOLAR CELLS SENSITIZED BY PROXIMAL NANOCRYSTALLINE QUANTUM DOTS

by

NATIS SHAFIQ, BS, MS

### **DISSERTATION**

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY IN

MATERIALS SCIENCE AND ENGINEERING

THE UNIVERSITY OF TEXAS AT DALLAS

August 2017

#### **ACKNOWLEDGMENTS**

First and foremost, I would like to extend my deepest and most sincere gratitude to my mentor and advisor, Dr. Yves J. Chabal. He has supported and patiently mentored me during this time. I am ever grateful to him for providing me guidance towards finishing my dissertation. He has been a great and motivating mentor. I have learned tremendously from his wisdom and I wish to carry that forward in my life. I will be forever in debt to him for all the support, both academically and philosophically, he has provided during my PhD.

Secondly, I would like to express my sincere gratitude to Dr. Anton V. Malko, who has patiently co-advised me in this project. He has given me the opportunity to work in an exciting problem and provided necessary guidance to move forward. I am ever grateful for his support.

I would also like to thank my committee members, Dr. Jiyoung Kim and Dr. Chadwin D. Young, for agreeing to lend their expertise in finalizing my dissertation. I am thankful for their suggestions and feedback.

I deeply acknowledge the funding received from Department of Energy (DOE) and National Science Foundation (NSF) to continue my research.

Also, I would like to extend my heartfelt appreciation to Dr. Sara Rupich, Dr. Weina Peng and Dr. Jeff Veyan. Specially, Dr. Rupich has been very helpful and cooperative during my course of PhD. I have learned enormously from her outstanding presentation and writing skills. I would also like to thank Dr. Julia Hsu, Dr. Jason Slinker and Dr. Manuel Quevedo for giving me the opportunity to work in their labs. I would also like to thank Dr. Yuri Gartstein, Dr. Richard Chapman and Dr. Benjamin Lee (NREL) for their insightful suggestions and feedback. Also, I would like to extend my earnest gratitude to my friend and colleague, Dr. Liang Xu, who helped

with some of the electrical measurements. My deepest appreciation to all my friends and lab members. They have contributed vastly to enrich my life in many ways.

I am ever grateful to Dr. Gordon Pollack for enduring my questions in UTD clean room. He has been very patient and helped tremendously during my long hours in the clean room. I have had the pleasure to know and get trainings from Dr. Roger Robbins. I am very thankful for that. All the clean room staffs at UTD are extremely knowledgeable and helpful. It has been a great honor to get an opportunity to work with them.

Special thanks to Ashley Willess and other Materials Science and Engineering staffs at UTD for being extremely helpful and efficient.

At this moment, I would like to say thanks to my family members. They have been extremely supportive through this testing time of my life. My mom and dad have always kept faith on my abilities and endured the long absence for the sake of my advancement. I cannot put words to show my gratitude towards their sacrifices. So, I dedicate my dissertation to them. Also, I would like to thank my younger brother, Sabit, who has been very courageous and looked after my parents during this time. His presence is a blessing in my life.

My PhD has not been a smooth ride. There were times when I got demotivated, lost confidence and eventually life became stagnant. My loving wife, Tassnim Zaman, stood beside me during these times. She showed enormous courage and channeled her patience to me. She endured all the uncertain times with me. I wouldn't be able to finish my PhD without her continuous and selfless support. You have been my best friend and loving companion. Thanks for everything.

July 2017

DESIGN APPROACHES FOR ENHANCING PHOTOVOLTAIC PERFORMANCE OF

SILICON SOLAR CELLS SENSITIZED BY PROXIMAL

NANOCRYSTALLINE QUANTUM DOTS

Natis Shafiq, PhD The University of Texas at Dallas, 2017

Supervising Professor: Yves J. Chabal

Energy transfer (ET) based sensitization of silicon (Si) using proximal nanocrystal quantum dots

(NQDs) has been studied extensively in recent years as a means to develop thin and flexible Si

based solar cells. The driving force for this research activity is a reduction in materials cost. To

date, the main method for determining the role of ET in sensitizing Si has been optical

spectroscopic studies. The quantitative contribution from two modes of ET (namely,

nonradiative and radiative) has been reported using time-resolved photoluminescence (TRPL)

spectroscopy coupled with extensive theoretical modelling. Thus, optical techniques have

established the potential for utilizing ET based sensitization of Si as a feasible way to develop

novel NQD-Si hybrid solar cells. However, the ultimate measure of the efficiency of ET-based

mechanisms is the generation of electron-hole pairs by the impinging photons. It is therefore

important to perform electrical measurements. However, only a couple of studies have attempted

electrical quantification of ET modes. A few studies have focused on photocurrent

measurements, without considering industrially relevant photovoltaic (PV) systems. Therefore,

there is a need to develop a systematic approach for the electrical quantification of ET-generated

vii

charges and to help engineer new PV architectures optimized for harnessing the full advantages of ET mechanisms. Within this context, the work presented in this dissertation aims to develop an experimental testing protocol that can be applied to different PV structures for quantifying ET contributions from electrical measurements. We fabricated bulk Si solar cells (SCs) as a test structure and utilized CdSe/ZnS NQDs for ET based sensitization. The NQD-bulk Si hybrid devices showed ~30% PV enhancement after NQD deposition. We measured external quantum efficiency (EQE) of these devices to quantify ET-generated charges. Reflectance measurements were also performed to decouple contributions of intrinsic optical effects (i.e., anti-reflection) from NQD mediated ET processes. Our analysis indicates that the contribution of ET-generated charges cannot be detected by EQE measurements. Instead, changes in the optical properties (i.e., anti-reflection property) due to the NQD layer are found to be the primary source of the photocurrent enhancement. Based on this finding, we propose to minimize bulk Si absorption by using an ultrathin (~300 nm) Si PV architecture which should enable measurements of ETgenerated charges. We describe an optimized process flow for fabricating such ultrathin Si devices. The devices fabricated by this method behave like photo-detectors and show enhanced sensitivity under 1 Sun AM1.5G illumination. The geometry and process flow of these devices make it possible to incorporate NQDs for sensitization. Overall, this dissertation provides a protocol for the quantification of ET-generated charges and documents an optimized process flow for the development of an ultrathin Si solar cells.

# TABLE OF CONTENTS

| ACKNOWLE    | DGMENTS                                                                         | v     |

|-------------|---------------------------------------------------------------------------------|-------|

| ABSTRACT.   |                                                                                 | vii   |

| LIST OF FIG | URES                                                                            | xi    |

| LIST OF TAE | BLES                                                                            | xviii |

| CHAPTER 1   | INTRODUCTION                                                                    | 1     |

| 1.1         | Motivation                                                                      | 1     |

| 1.2         | Concept of nanocrystal quantum dot (NQD)-Si hybrid photovoltaics                | 6     |

| 1.3         | Dissertation organization                                                       | 9     |

| CHAPTER 2   | THEORETICAL BACKGROUND AND LITERATURE REVIEW                                    | 11    |

| 2.1         | Energy transfer (ET) mechanism                                                  | 12    |

| 2.2         | Fundamentals of solar cells.                                                    | 19    |

| CHAPTER 3   | EXPERIMENTAL METHODS                                                            | 24    |

| 3.1         | Deposition techniques                                                           | 24    |

| 3.2         | Etching by plasma processes                                                     | 29    |

| 3.3         | Characterization techniques                                                     | 33    |

| 3.4         | Electrical measurements of the fabricated devices                               | 41    |

|             | PERFORMANCE EHANCEMENT OF BULK SILICON SOLAR CELL UNANOCRYSTALLINE QUANTUM DOTS |       |

| 4.1         | Preface                                                                         | 44    |

| 4.2         | Introduction                                                                    | 45    |

| 4.3         | Experimental methods                                                            | 48    |

| 4.4         | Results and Discussion                                                          | 51    |

| 4.5         | Conclusions                                                                     | 76    |

| CHAPTER 5   | DESIGN APPROACHES FOR ULTRATHIN SILICON SOLAR CELLS                             | 78    |

| 5.1         | Introduction                                                                    | 78    |

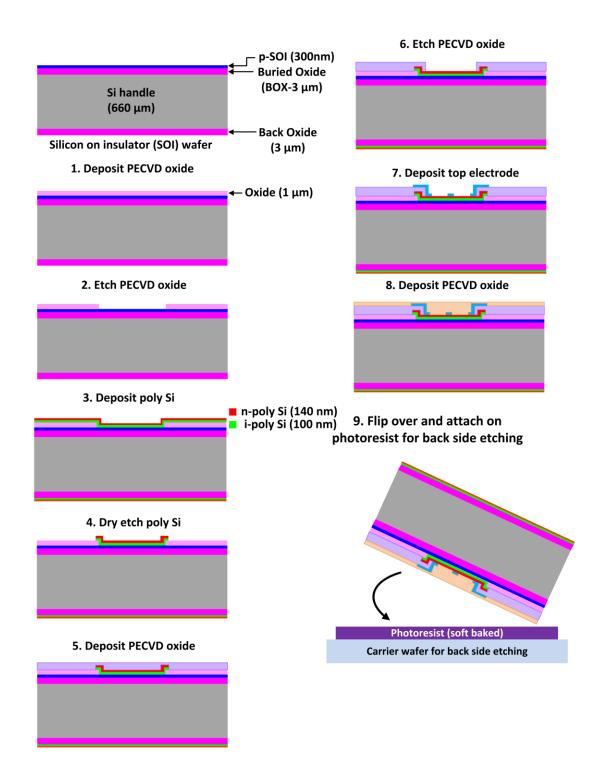

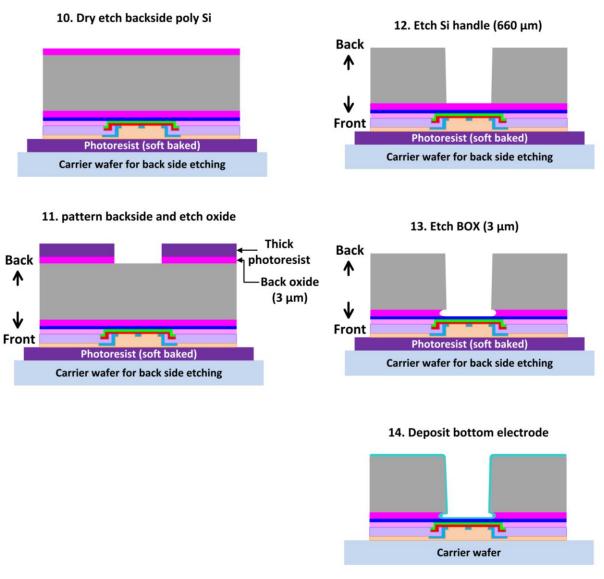

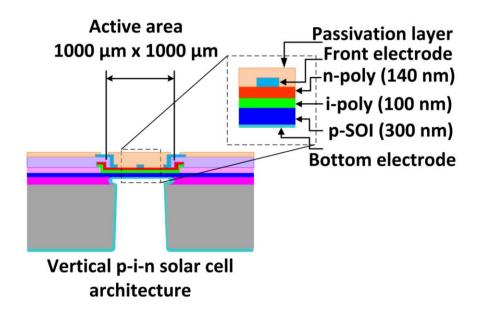

| 5.2         | Fabrication steps of ultrathin SOI devices                                      | 80    |

|       | 5.3    | Defects in the suspended SOI films | 88   |

|-------|--------|------------------------------------|------|

|       | 5.4    | Design considerations              | 90   |

|       | 5.5    | Electrical characterization.       | 101  |

|       | 5.6    | Conclusions                        | 104  |

| СНАР  | TER 6  | OUTLOOK AND FUTURE DIRECTIONS      | 106  |

| REFEI | RENCE  | S                                  | 109  |

| BIOGI | RAPHIO | CAL SKETCH                         | .120 |

| CURR  | ICULU  | M VITAE                            |      |

# LIST OF FIGURES

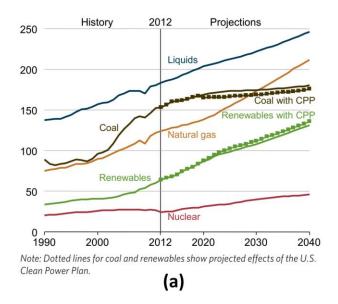

| Figure | 1.1 (a) Energy consumption (unit of quadrillion Btu) in world by energy source from 1990-2040.[1] (b) Annual percentage change of cumulative global electricity capacity by source.[5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

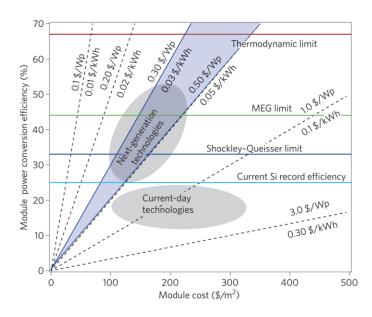

| Figure | 1.2. Relationship between power conversion efficiency, module costs per area and cost per peak watt (\$/W <sub>p</sub> ). Decreasing the module cost can facilitate use of lower efficiency cells but higher module cost can be tolerated if the module efficiency can be substantially increased.[8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

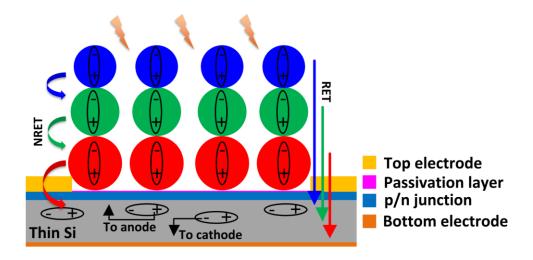

| Figure | 1.3. Schematic drawing showing the concept of ET based NQD-Si hybrid solar cell in a planar configuration. Size gradient NQD layers cover the solar spectrum. Absorbed energy is cascaded towards Si through different ET modes such as non-radiative energy transfer (NRET) and radiative energy transfer (RET).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

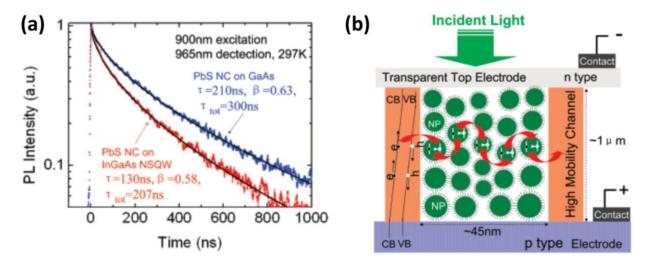

| Figure | 2.1. (a) Time-resolved PL of PbS NQDs on passviated GaAs (blue) and on passivated near surface quantum wells (red), excited at 900 nm (below GaAs bandgap) and detected at 965 nm (PbS PL peak). The decay of the TRPL curves are fitted using a stretched exponential function. (b) Schematic showing an architecture comprising NQD absorbers embedded in a vertical array of high-mobility channels that allow nonradiative transfer of excitons from the adjacent NQDs and simultaneously provide high-mobility transport.[16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

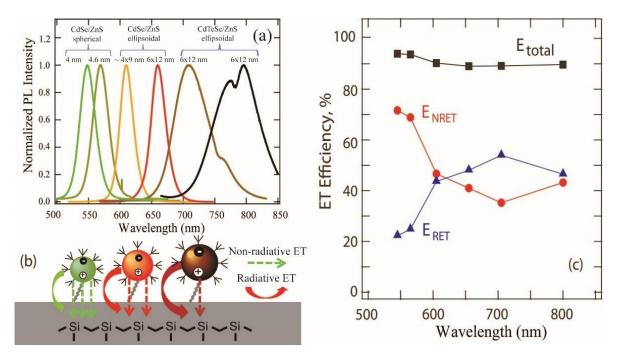

| Figure | 2.2. (a) PL emission spectra of different NQDs emitting from 545 to 800 nm as grafted on SiO <sub>2</sub> . NQDs on Si exhibit the same PL profile. (b) Schematics of energy transfer from NQDs emitting at different wavelength to Si substrate. (c) Total ET efficiency ( $E_{total}$ ) shown by black squares along with separate contributions $E_{NRET}$ from NRET (red circles) and $E_{RET}$ from RET (blue triangles).[23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

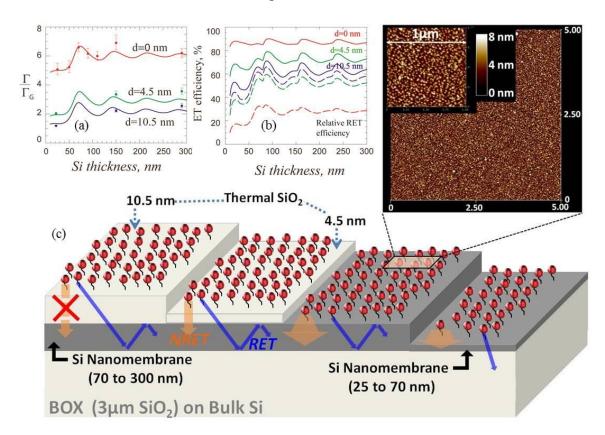

| Figure | 2.3. (a) Relative acceleration of the NQD exciton decay with respect to the reference glass sample as a function of the thickness, t, of the SiNM. The data points and theoretical curves are grouped by different values of the silicon oxide spacer thickness (d). The distance of the dipole emitter from the top surface is taken as $z = 4$ nm for the red theoretical curve and $z = 3.7$ nmfor the green and blue ones. The dielectric parameters of Si used for calculations are $\varepsilon' = 16.5$ and $\varepsilon'' = 0.32$ . Here the data points are shown with the reference $\tau_G = 22.8$ ns. (b) Efficiency of ET into Si as extracted from the color-coordinated theoretical curves in panel (a). The solid lines correspond to the total ET efficiency $[(\Gamma_{RET} + \Gamma_{NRET})/\Gamma]$ and the dashed lines show the relative efficiency of ET just via waveguide modes in the SiNM $(\Gamma_{RET}/\Gamma)$ . (c) Schematics of different NQD/SiNM structures used to extract the relative participation of various decay channels: schematically displayed are NRET and RET processes from NQDs into the underlying Si slab as well as into SiOs substrate (on the rightmost structure). The role of NRET is |

|        | strongly diminished with a thicker spacer (the leftmost structure), while the waveguide modes in Si are excited quite efficiently. (Top right) AFM images of NQDs attached via carboxy-terminated alkyl chains on an oxide-free SiNM surface. The 5x5 µm image emphasizes the homogeneity of the NQDs' monolayer attachment, while the 1x1 µm confirms the individuality of the NQDs to minimize interdot ET effects.[18] |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

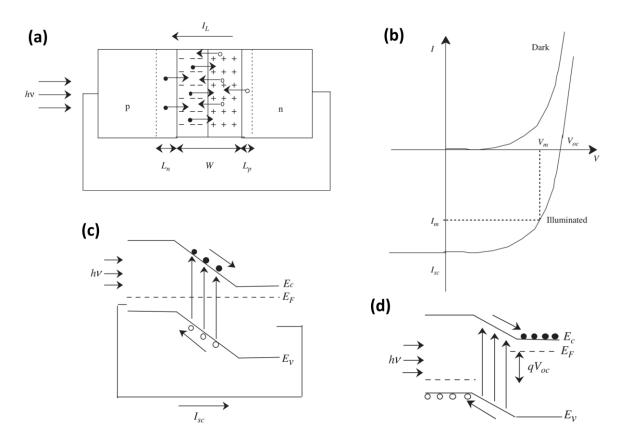

| Figure | 2.4. Schematic diagram (a) of a p-n junction under illumination, (b) the current-voltage characteristic of a p-n junction in the dark and under illumination, (c) a short-circuited current under illumination, and (d) open-circuited voltage.[39]20                                                                                                                                                                     |

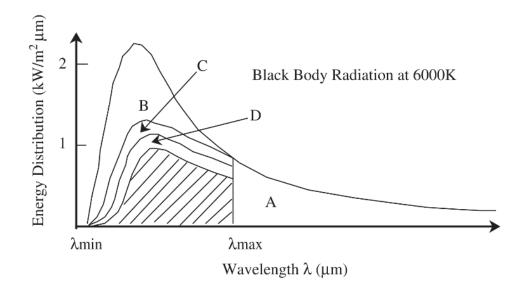

| Figure | 2.5. Schematic of energy losses in an ideal solar cell. 'A' is related to energy that is not absorbed by the semiconductor. 'B' deals with thermalization loss to the band edge, (i.e loss of excess energy after absorption). 'C' is loss associated with voltage and 'D' is loss associated with the fill factor.[39]                                                                                                   |

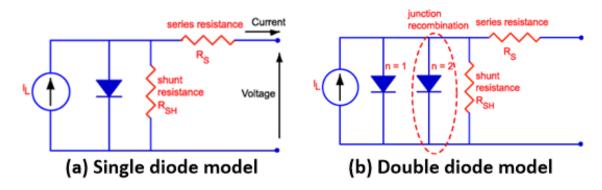

| Figure | 2.6. Equivalent circuit of the solar cell showing both series and shun resistant for (a) one and (b) two diode model.[40]                                                                                                                                                                                                                                                                                                 |

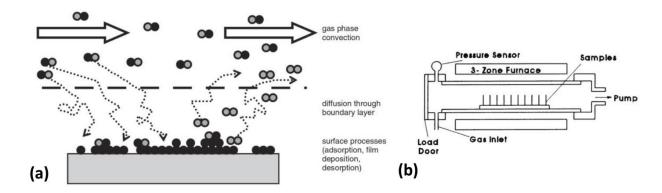

| Figure | 3.1. (a) Typical steps in a CVD process for film deposition of film.[41]. (b) schematic of a LPCVD chamber.[42]                                                                                                                                                                                                                                                                                                           |

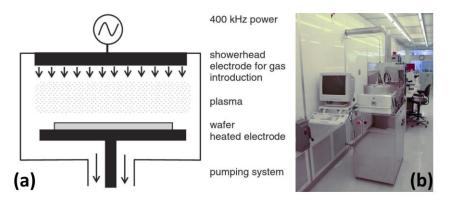

| Figure | 3.2. (a) Schematic of a simple parallel-plate diode PECVD reactor.[43]. (b) Image of the Plasma-Therm 790 PECVD in the UTD clean room                                                                                                                                                                                                                                                                                     |

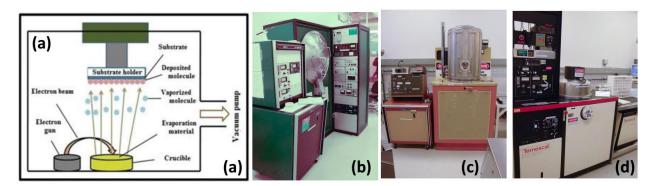

| Figure | 3.3. (a) Schematic of electron beam evaporation.[41]. Images of the (b) CHA-50 evaporator (planetary accessory for sidewall deposition), (c) Cryo e-beam evaporator (stage is stationary) and (d) Temescal e-beam evaporator (stage rotation available) in the UTD cleanroom.                                                                                                                                             |

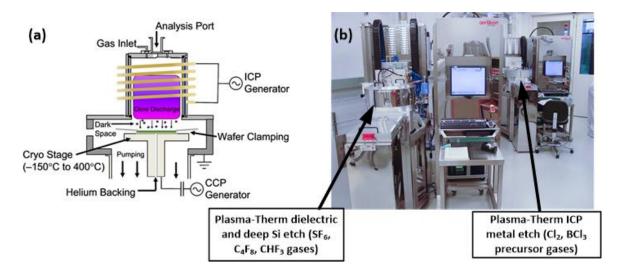

| Figure | 3.4. (a) Schematic of an ICP-RIE tool.[44]. (b) Image of the plasma processing tools used in the UTD cleanroom                                                                                                                                                                                                                                                                                                            |

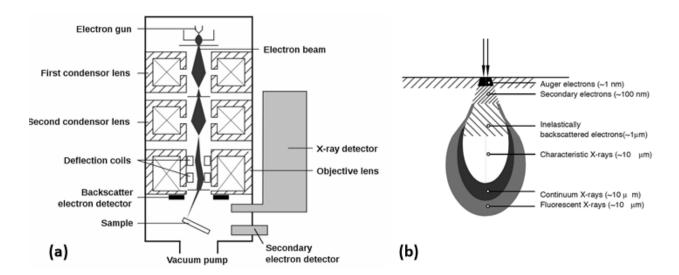

| Figure | 3.5. Schematics of (a) a scanning electron microscope.[43] and (b) interaction volume of electron and specimen atoms.[45]                                                                                                                                                                                                                                                                                                 |

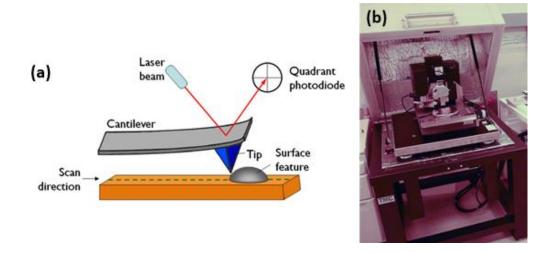

| Figure | 3.6. (a) Schematic of the working principle of atomic force microscope (AFM).[46] (b) Image of the Veeco Model 3100 AFM.                                                                                                                                                                                                                                                                                                  |

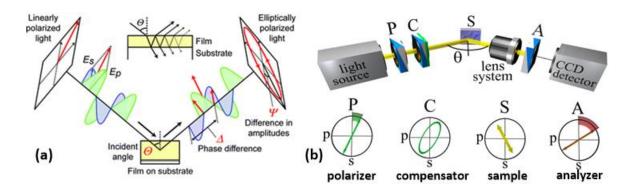

| Figure | 3.7. (a) Working principle of spectroscopic ellipsometry.[47] and (b) schematic of major parts of the ellipsometry tool.[48]                                                                                                                                                                                                                                                                                              |

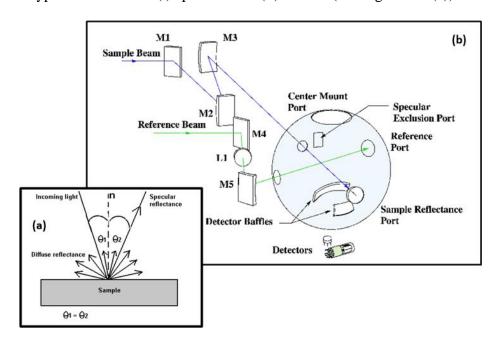

| Figure | 3.8. (a) Schematic showing specular and diffuse reflectance. (b) Schematic of ar integrating sphere (diffuse reflectance accessory (DRA)) used for Cary 5000 UV/VIS/NIR spectrometer.[50]                                                                                                                                                                                                                                 |

| Figure | 3.9. Veeco Dektak VIII Prolifometer at UTD cleanroom3                                                                                                                                                                                                                                                                                                                                                                                |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

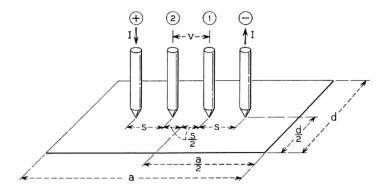

| Figure | 3.10. Schematic diagram of a four-point probe measurement.[51]                                                                                                                                                                                                                                                                                                                                                                       |

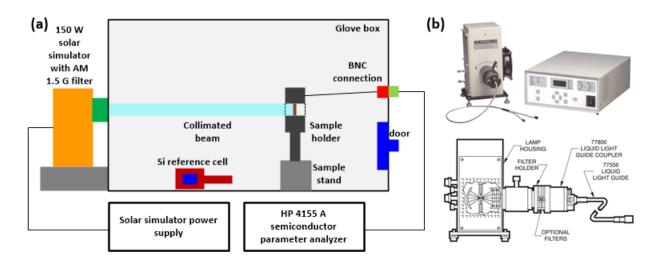

| Figure | 3.11. (a): Schematic of the solar cell measurement setup inside a glove box. (b) Newpor 9600 solar simulator with power source.[52]                                                                                                                                                                                                                                                                                                  |

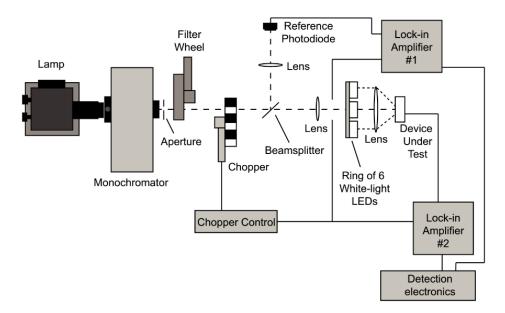

| Figure | 3.12. Schematic of a white light biased EQE system.[53]                                                                                                                                                                                                                                                                                                                                                                              |

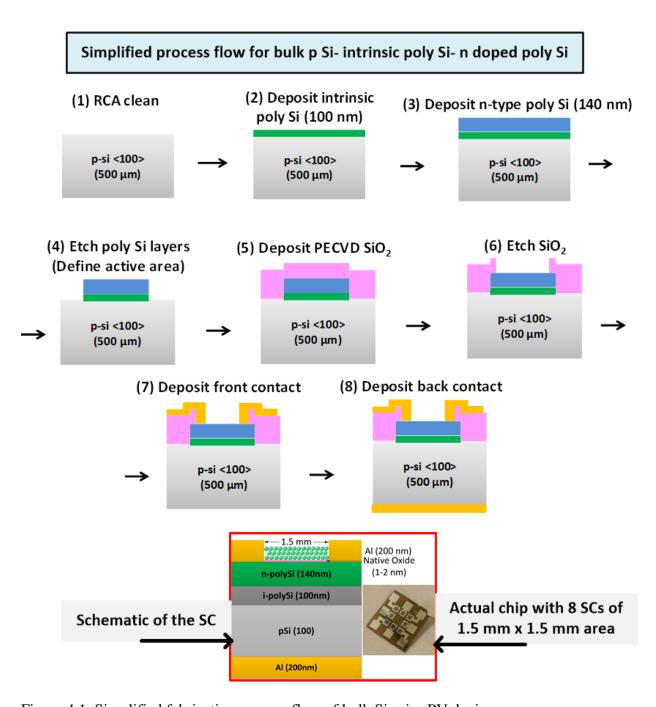

| Figure | 4.1. Simplified fabrication process flow of bulk Si p-i-n PV devices5                                                                                                                                                                                                                                                                                                                                                                |

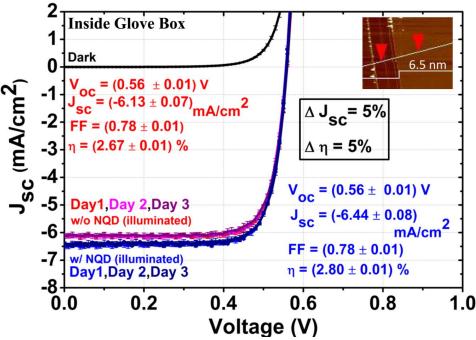

| Figure | 4.2. Temporal stability of the fabricated bulk p-type Si SC measured inside the glove box J-V curves of the device under dark and illuminated conditions for consecutive 3 days Inset: AFM image showing a ~6.5 nm thick NQD layer (~1 monolayer) deposited on the device. Black curves: dark measurement, Red and blue curves show the illuminate measurement without and with NQDs, respectively                                   |

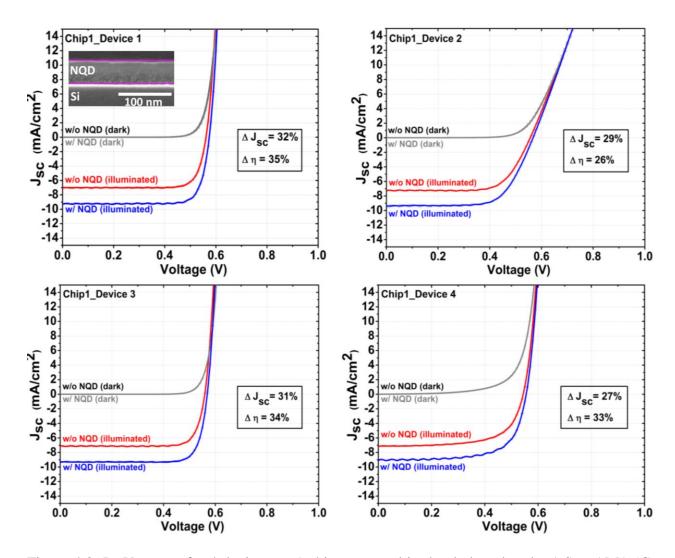

| Figure | 4.3. $J_{sc}$ -V curves for 4 devices on 1 chip measured in the dark and under 1 Sun AM1.50 illumination. The black and grey curves represent the dark behavior with and without NQDs. Red curves represent $J_{sc}$ -V characteristics for SCs without NQDs under illumination. Blue curves represent $J_{sc}$ -V characteristics for SCs with NQDs. Insert Shows SEM image of ~70 nm CdSe/ZnS NQD layer deposited by spin coating5 |

| Figure | 4.4. Thickness variation of poly Si deposited by LPCVD on a bulk p-type Si wafer. Th thickness of the deposited intrinsic and n-doped poly Si is 100 nm and 140 nm respectively.                                                                                                                                                                                                                                                     |

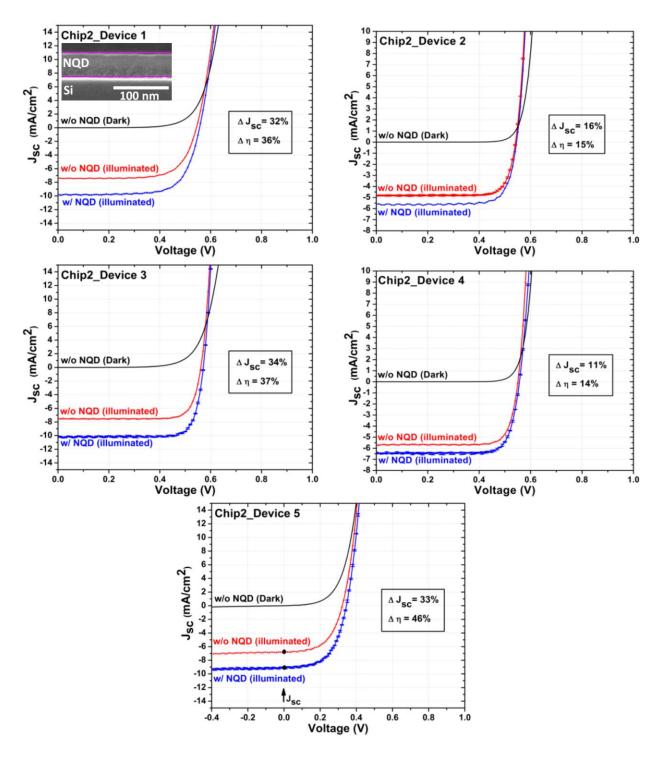

| Figure | 4.5. $J_{sc}$ -V curves for 5 devices on of Chip2 measured in the dark and under 1 Su AM1.5G illumination. The black curves represent dark $J_{sc}$ -V behavior of the SCs with and without NQDs. Red and blue curves are for SCs without and with NQDs under illumination. respectively Inset: SEM image of ~70 nm NQD (CdSe/ZnS) layer deposite by spin coating.                                                                   |

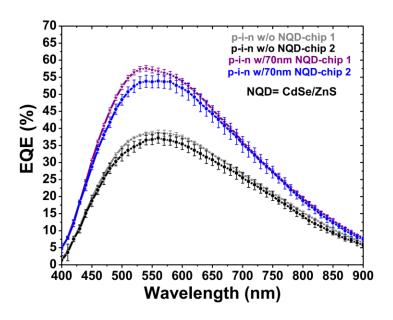

| Figure | 4.6. Comparison of the average EQE curves for chip1 and chip2. Grey and black curve are before NQD deposition. Purple and blue curves are after SCs after NQD deposition.5                                                                                                                                                                                                                                                           |

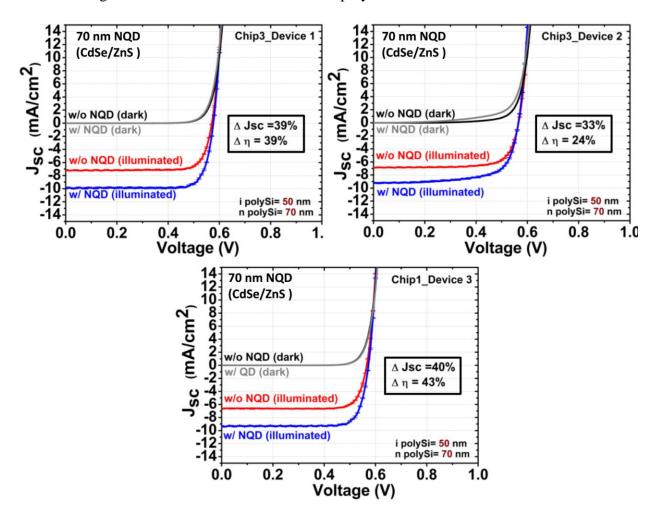

| Figure | 4.7. J <sub>sc</sub> -V curves for SCs with thinner poly Si layers (i(50nm)-n(70nm)) measured in th dark and under 1 Sun AM1.5G illumination. The black and grey curves represent the dar J <sub>sc</sub> -V behavior without and with NQDs, respectively. Red and blue curves represent J <sub>sc</sub> -C characteristics under illumination without and with NQDs, respective                                                     |

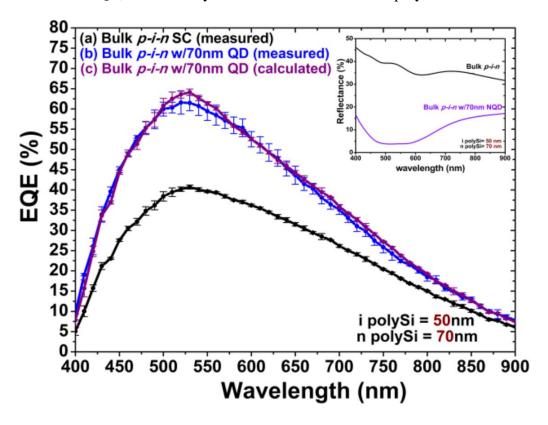

| Figure | 4.8. Comparison of EQE curves for chip2 (i(100nm) n(140nm)) and chip3 (i(50nm n(70nm)). Black and grey curves: EQE of the SCs before NQD deposition for chip2 and                                                                                                                                                                                                                                                                    |

| chip3, respectively. Blue and green curves: EQE of the SCs after NQD deposition (~70 nm of CdSe/ZnS) for chip2 and chip3, respectively                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

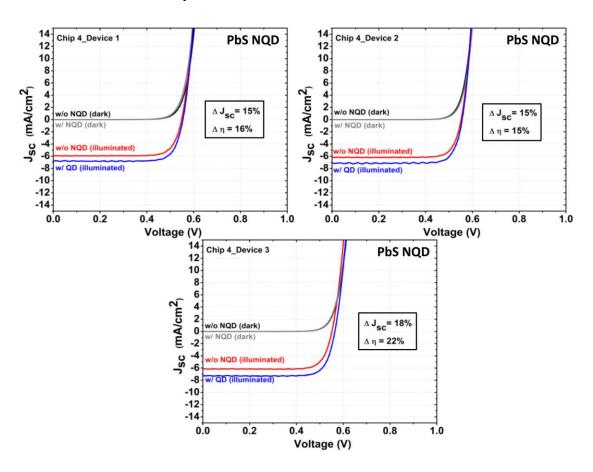

| Figure 4.9. J <sub>sc</sub> -V curves for hybrid NQD/Si p-i-n SCs with NIR emitting PbS NQDs. The black and grey curves represent dark behavior without and with PbS NQDs, respectively. Red and curves represent behavior under 1 Sun AM1.5G illumination without and with PbS NQDs, respectively. The SC had poly Si layer o with 100 nm of i- and 140 nm n-type Si.64 |

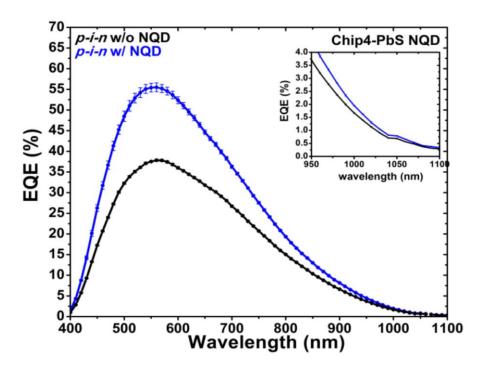

| Figure 4.10. Average EQE curves for p-i-n devices with PbS NQDs. Black curve: EQE of SCs without NQD. Blue curve: EQE of the SCs after deposition of PbS NQD using same spin coating condition. Inset: Zoomed EQE curves from 950-1100 nm. Thickness of i poly Si and n-doped poly Si is 100 nm and 140 nm, respectively                                                 |

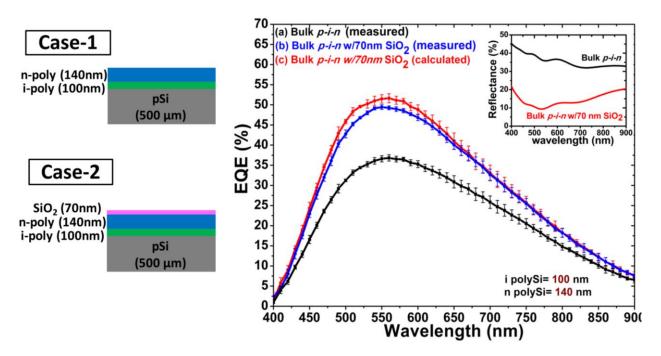

| Figure 4.11. Schematics of the two cases studied: SC without (Case 1) and with Case 2) 70 nm of SiO <sub>2</sub> . EQE curves of (a) bare bulk pSi-i(100nm)-n(140nm) poly Si SC, (b) with 70 nm of SiO <sub>2</sub> and (c) calculated by considering enhanced absorption as found from reflectivity measurements. Inset: reflectivity measurements case 1 and case 2    |

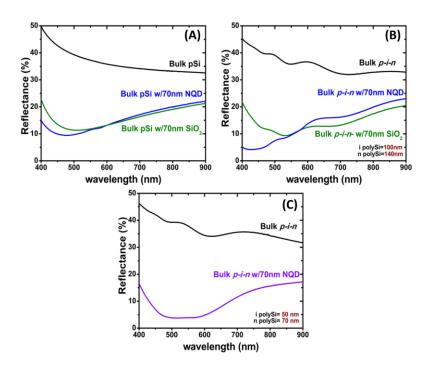

| Figure 4.12. Reflectance measurements (a) of bulk p-Si bare, with 70 nm NQDs and 70 nm oxide (b) of bulk p-i (100nm)-n (140nm) Si bare, with 70 nm NQDs and with 70 nm oxide and (c) bulk p-i (50nm)-n (70nm) Si bare and with 70 nm NQDs                                                                                                                                |

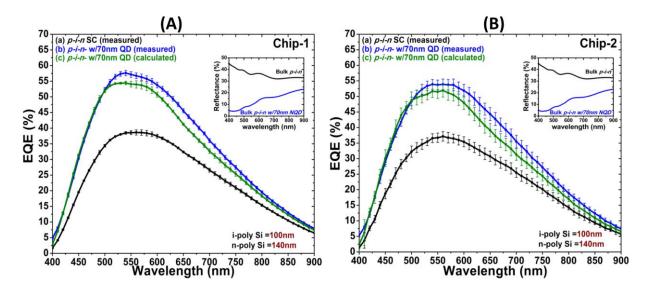

| Figure 4.13. Measured and calculated EQE curves for (A) Chip 1 and (B) chip 2 bulk pSi-i(100nm)-n(140nm) poly Si SCs. The black curve is for the bare device, while the blue and green are the measure and calculated curves respectively. Inset: (A) and (B) are reflectivity measurements for the devices with (blue) and without (black) NQDs69                       |

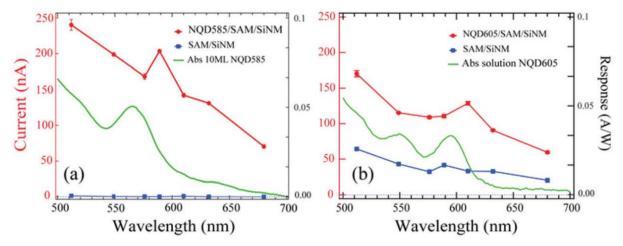

| Figure 4.14. Photocurrent as a function of excitation wavelength for SAM passivated ultrathin (~75 nm) SiNMs. The blue and red traces show the photocurrent before and after NQD deposition respectively. The green curve shows the solution absorbance of the NQDs. The graph on the left shows NQDs that peak at 585 nm while that on the right peaks at 605 nm.[89]   |

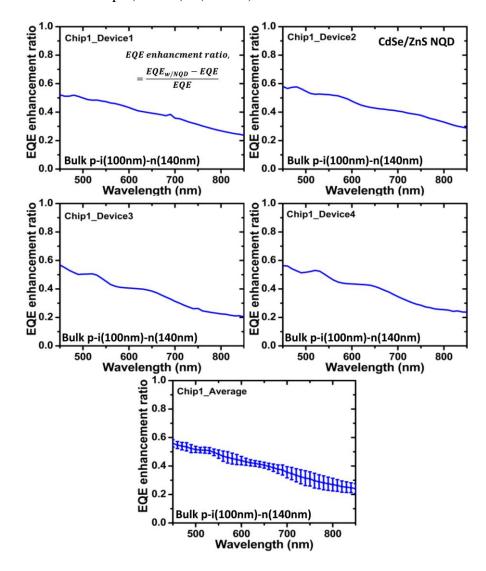

| Figure 4.15. Top four graphs show EQE enhancement for individual devices from Chip-1 (bulk pSi-i(100nm)-n(140nm) poly Si SC) after ~70 nm NQD deposition. Bottom graph shows the average behavior for all the devices                                                                                                                                                    |

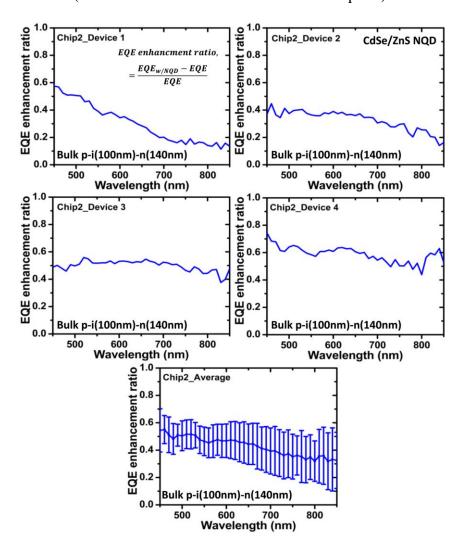

| Figure 4.16. Top four graphs show EQE enhancement for individual devices from Chip-2 (bulk pSi-i(100nm)-n(140nm) poly Si SC) after ~70 nm NQD deposition. Bottom graph shows the average EQE enhancement for all the devices                                                                                                                                             |

| Figure 4.17. Measured and calculated EQE curves for bulk pSi-i(50nm)-n(70nm) poly Si SCs (a) bare, (b) with 70 nm of CdSe/ZnS NQDs and (c) calculated from the reflectivity                                                                                                                                                                                              |

|        | measurements. Inset: reflectivity measurement for pSi-i(50nm)-n(70nm) poly Si without (black) and with 70 nm of NQDs                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

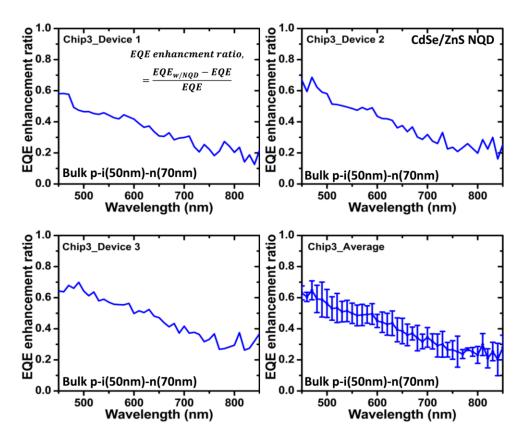

| Figure | 4.18. First three graphs show individual EQE enhancement for 3 devices from Chip-3 (bulk pSi-i(50nm)-n(70nm) poly Si SC) after 70 nm CdSe/ZnS NQD deposition. Last graph shows the average EQE enhancement for all the devices                                                                                                                                                                                                                                                                                        |

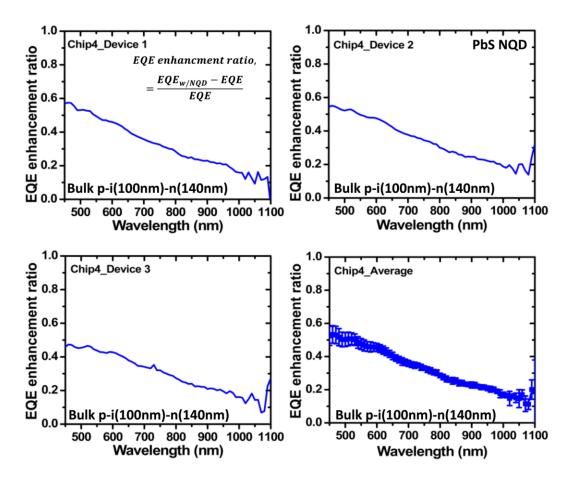

| Figure | 4.19. First three graphs show individual EQE enhancement for 3 devices from Chip-4 (bulk pSi-i(100nm)-n(140nm) poly Si SC) after ~ PbS NQD deposition. Last graph shows the average EQE enhancement for all the devices                                                                                                                                                                                                                                                                                               |

| Figure | 5.1. Simplified processing steps for the fabrication of a n ultrathin p-i-n Si SC based or 300 nm SOI.                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure | 5.2. Schematic of the free standing SOI based Si p-i-n SC after all fabrication steps are complete                                                                                                                                                                                                                                                                                                                                                                                                                    |

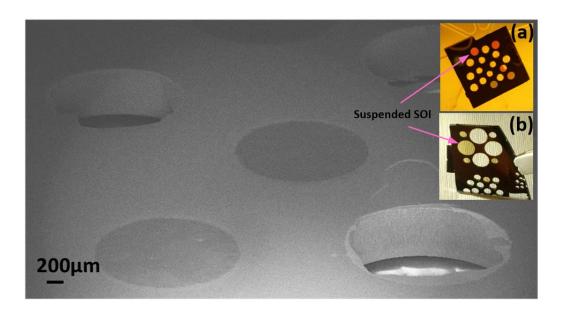

| Figure | 5.3. SEM image showing a free-standing SOI (without top and bottom metal electrodes) suspended over a 1.5 mm diameter etch hole. The inset (a and b) show chips with several etch holes with a diameter of 1.5 and 5 mm, respectively. Most of the suspended SOI films are destroyed after the full processing cycle due to induced mechanical and structural stress.                                                                                                                                                 |

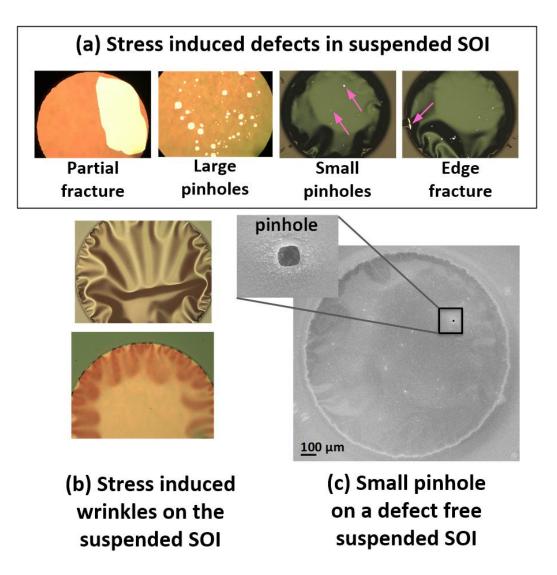

| Figure | 5.4. Stress induced defects in free standing SOI films suspended over a 1.5 mm diameter etch hole. (a) Optical images showing different defects observed after the process completion. (b) Optical images of wrinkled SOI films due to stress either over the entire film or at the edges (c) SEM image showing small pinholes in an otherwise defect free suspended SOI. The size of the pinhole is $\sim 3~\mu m$ .                                                                                                 |

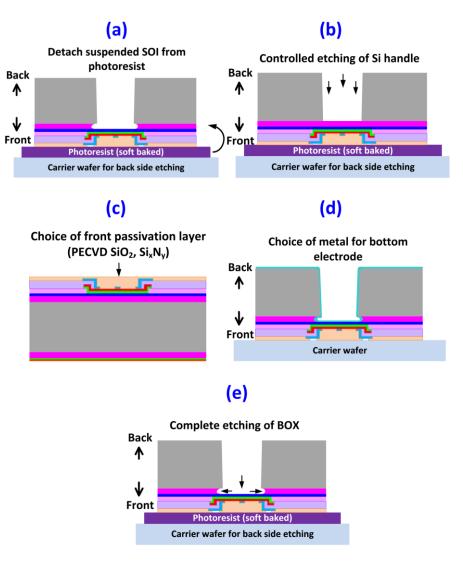

| Figure | 5.5. Schematic showing five major roadblocks encountered during the design of suspended SOI based Si SC. These include (a) stress reduction during detachment of the suspended SOI films from the photoresist, b) controlled etching of the Si handle (660 µm) to reduce stress, (c) selection of front passivation layer to prevent etching the from of the SOI film, (d) bottom electrode metal selection to reduce thermally induced stress and (e) removal of BOX (3 µm) layer for electrical contact at the back |

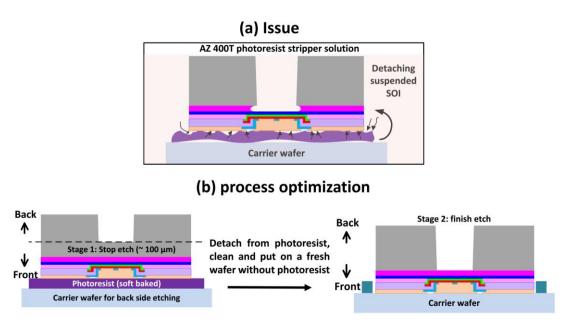

| Figure | 5.6. (a) Schematic showing the stress induced during photoresist stripping in AZ400T stripper solution. (b) Schematic showing a 2- step process that that overcomes this problem.                                                                                                                                                                                                                                                                                                                                     |

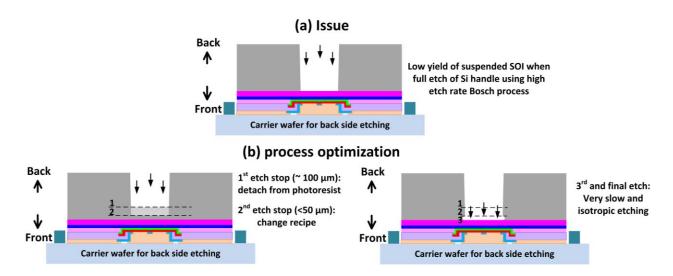

| Figure | 5.7. (a) Schematic showing the low yield of suspended SOI film when the Si handle is completely etched by the Bosch process. (b) Schematic showing the optimized multiple step etching process.                                                                                                                                                                                                                                                                                                                       |

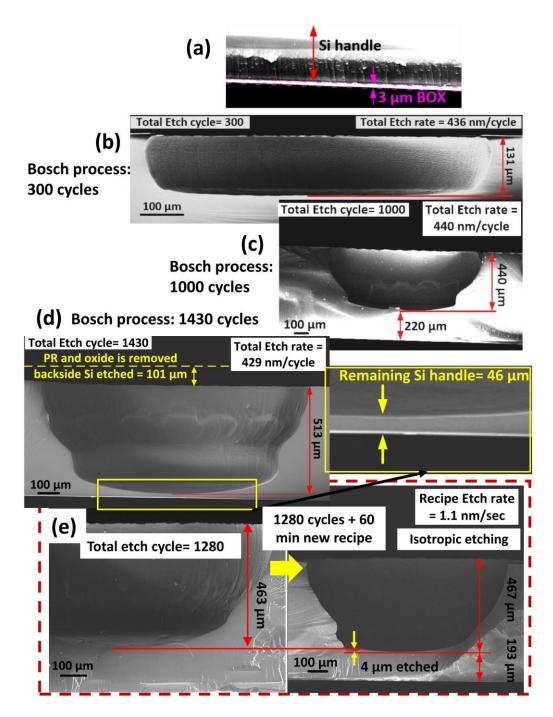

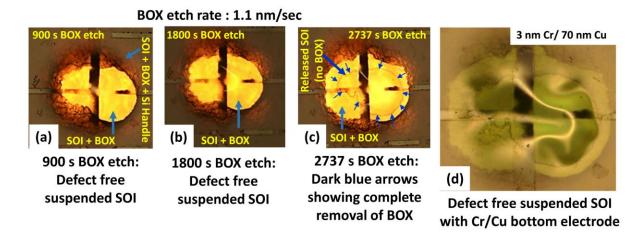

| rigure | Bosch process. SEM image of the SOI wafer with 3 µm BOX (a) before etching, (b) after 300 cycles when 131 µm Si has been etched, (c) after 1000 cycles when 440 µm has been etched, (d) and after 1430 cycles when 614 µm of Si has been etched and 46 µm of the Si handle remains, (e) etch rate of new oxide recipe determined as 1.1 nm/sec from the 4 µm Si etched after 60 mins of new recipe                                                                                                                            |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

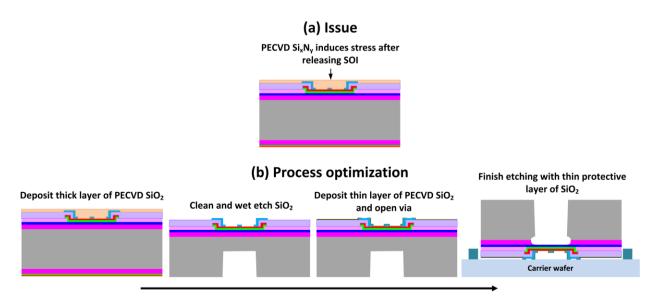

| Figure | 5.9. (a) Schematic showing $\sim 2~\mu m$ PECVD $Si_xN_y$ deposited over the suspended SOI film. (b) Schematic of the process optimization to overcome this problem. Here, $\sim 2~\mu m$ PECVD $SiO_2$ is used as a protective layer in the $1^{st}$ step. Then a thin ( $\sim 300$ - $500$ nm) $SiO_2$ layer is deposited on top as protective layer for the final etching stages                                                                                                                                           |

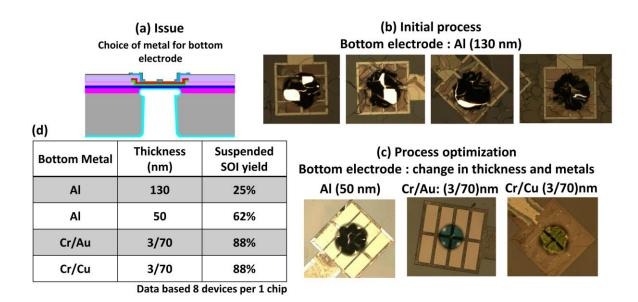

| Figure | 5.10. (a) Schematic showing the stress induced due to bottom electrode. (b) Optical images showing fractures in suspended SOI film after depositing thick (~ 130 nm) Al films. (c) Optical images showing suspended SOI devices electrodes comprised of thinner Al (50 nm), Cr/Au and Cr/Cu. (d) Table of the mechanical and structural yield of the suspended SOI devices with different metals and thicknesses                                                                                                              |

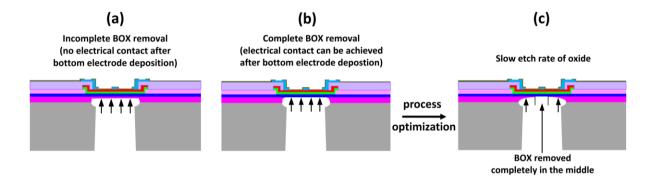

| Figure | 5.11. (a) Schematic showing how incomplete removal of the BOX (3 µm) layer prevents an electrical connection after bottom electrode deposition. (b) Complete removal of the BOX is necessary to achieve an electrical connection. (c) Using a slow and isotropic etch recipe allows complete removal of the BOX layer from the middle of the device99                                                                                                                                                                         |

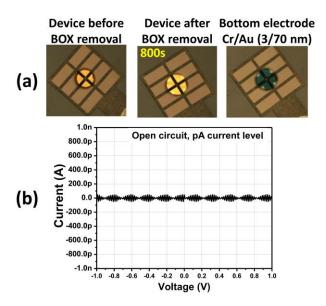

| Figure | 5.12. (a) Optical images (illuminated from back) showing suspended SOI devices before BOX removal, after 800 s etching and after deposition of the Cr/Au back electrode. (b) I-V curve of the above device. The open circuit device behavior indicates presence of an insulating layer in between SOI and bottom electrode                                                                                                                                                                                                    |

| Figure | 5.13. Series of optical images (illuminated from back) showing the evolution of BOX etching after (a) 900 s, (b) 1800s, (c) 2737 s and (d) after Cr/Cu deposition. The etch rate is ~1.1 nm/s. The image in (c) shows that BOX is completely removed from the middle (indicated by dark blue arrows)                                                                                                                                                                                                                          |

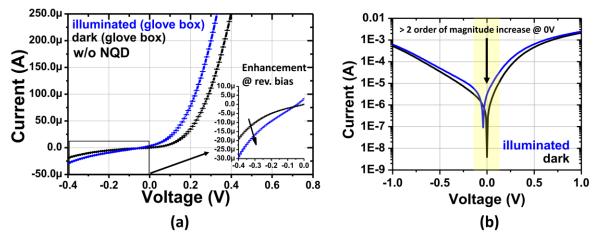

| Figure | 5.14. Electrical measurements of the suspended SOI device after removal of BOX and deposition of a bottom Cr/Cu electrode as shown in Figure 5.13. (a) I-V characteristic of the device in dark (black curve) and under 1 Sun AM1.5G illumination (blue curve). The inset shows an enhanced photo-response in the reverse bias condition. (b) I-V characteristic of the device plotted in a semi-log graph. The blue curve (under illumination) shows >2 order of magnitude enhancement at 0 V compared to black curve (dark) |

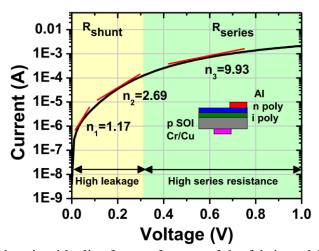

Figure 5.15. I-V graph showing ideality factors for one of the fabricated SOI devices. The device

shows significant deviation from high performing diodes (n<2). The low voltage region

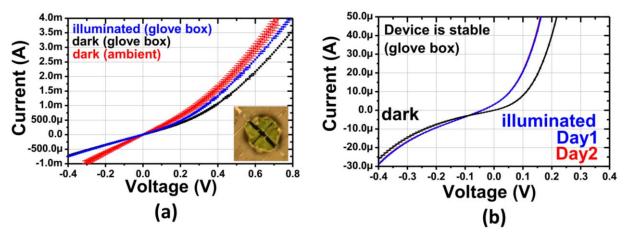

| Figure 5.16. Effect of the environment on the stability and repeatability of the suspe | ended SOI   |

|----------------------------------------------------------------------------------------|-------------|

| device characteristics. (a) I-V graph of the device measured in the dark is            | n ambient   |

| conditions (red) and in the glove box (black) as well as under illumination in         | the glove   |

| box blue). Inset: optical image of the measured device. (b) I-V graph of the           | the device  |

| measured for two days in the glove box. Black curve shows the dark beha                | vior. Blue  |

| (day1) and red (day2) curves show device behavior under illumination. The re           | ed curve is |

| hard to see as it falls under the blue curve                                           | 104         |

$(V<0.3\ V)$  is dominated by high leakage current. The high voltage region  $(V>0.3\ V)$  is dominated by high series resistance......103

# LIST OF TABLES

| Table 3.1. The advantages and disadvantages of using spectroscopic ellipsometry.[49]37                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.1. Summary of PV performance parameters for 4 devices on chip-1 measured under 1 sun AM1.5G illumination without (w/o) and with (w/) NQDs56                                                                                            |

| Table 4.2. Summary of PV performance parameters for 5 devices from chip2 measured under 1 sun AM1.5G illumination without (w/o) and with (w/) NQDs                                                                                             |

| Table 4.3. Summary of PV performance parameters for 3 devices from chip3 with thinner i-poly Si (50nm) and n-doped (70nm) poly Si layers as measured under 1 sun AM1.50 illumination without (w/o) and with (w/) NQD (CdSe/ZnS) NQD deposition |

| Table 4.4. Summary of PV performance parameters for SCs with i-poly Si (100nm) and n-doped (140nm) poly Si layers as measured under 1 sun AM1.5G illumination without (w/o) and with (w/) NQD (PbS) deposition.                                |

| Table 5.1. Percent of absorbed incoming photons at λ=550 nm for different thicknesses of Si and CdSe NQD.                                                                                                                                      |

| Table 5.2. Process parameters for the Bosch process (labeled 'DSE 100')94                                                                                                                                                                      |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation

Energy demand in the world is rapidly increasing. In recent times, the global demand of energy has increased several folds due to rapid technological advances. The U.S. Energy Information Administration (EIA) projects a 48% increase in global energy consumption by 2040 [1]. This increase in energy demand will be strongly driven by developing countries where economic growth and improvement in infrastructure will rapidly increase the consumption of energy. In fact, the EIA estimates a 71% rise in energy demand from 2012-2040 in developing countries compared to an 18% increase in developed countries for the same period [1]. In developed countries, technological advancement is a dominating force in our daily life and the energy cost associated with such upward progression cannot be overlooked. Modern society will need constant connectivity to electronic products and their associated services which will require abundant access to cheap energy. Within this context, renewable energy sources such as solar energy has the enormous potential to produce cheap energy.

Renewable energy sources are abundant, whereas fossil fuels are limited, expensive and not eco-friendly. This environmental factor is one of the chief reasons to utilize renewable energy sources such as wind, solar, hydro and geothermal energy. In fact, continues and heavy use of fossil fuel is causing climate change and increasing the occurrence and strength of natural disasters [2]. Substantial global capacity addition for the renewable energy sources has been observed in the 2015-16 period due to these reasons and the projection for the future is also very strong.

Solar energy is particularly important among all the renewable energy sources. It is the most abundant in nature. Solar energy is freely available for all the inhabitants of Earth and has zero greenhouse gas emissions, which is a major concern for the continued use of fossil fuels. The total radiant power of the sun is 3.8 x 10<sup>23</sup> kW and the Earth receives about 1.8 x 10<sup>14</sup> kW (i.e. solar irradiance is 1000 W/m² at the middle of a clear day) [2, 3]. The EIA estimates that US residential customers use on an average 30 kWh/day [2]. This personal daily energy consumption can be harnessed from an area of only 5 m² (or ~54 square foot) considering 6 hours of daily sunlight. Studies indicate that solar energy can sustainably satisfy the global demand for energy as the sun, an inexhaustible source of energy, will provide sustainable output over a very long period [2, 4].

The growth of renewable energy capacity has steadily increased (see the green curve labeled as renewables in Figure 1.1 (a)) as the global commitment to reducing the use of fossil fuels increased [5]. In 2015, the installed capacity of global solar photovoltaic (PV) increased by 28% from 2014 levels (see Figure 1.1 (b)) and this increase is highest among all the other sources of renewable energy as seen from Figure 1.1 (b) [5]. At the same time, there is a drive to increase PV efficiency. Researchers are actively evaluating different concepts and approaches to increase PV module efficiency in addition to cost reduction. In the foreseeable future, the PV industry will continue to see development in all sub-sectors such as photovoltaics (PVs), concentrating solar panels (CSP) and solar heaters [2]. It is an exciting time to explore innovative ideas with the aim to increase the uptake of PV.

|      | Hydropower | PV <sup>1</sup> | CSP <sup>2</sup> | Wind | Geothermal | Biomass        | All Renewables  |

|------|------------|-----------------|------------------|------|------------|----------------|-----------------|

| 2005 | 2%         | 38%             | 0%               | 23%  | 4%         | 13%            | 4%              |

| 2006 | 2%         | 32%             | 0%               | 25%  | 3%         | 7%             | 4%              |

| 2007 | 3%         | 5%              | 5%               | 27%  | 0%         | 6%             | 5%              |

| 2008 | 3%         | 71%             | 14%              | 29%  | 4%         | 4%             | 6%              |

| 2009 | 3%         | 62%             | 22%              | 31%  | 7%         | 15%            | 7%              |

| 2010 | 3%         | 90%             | 83%              | 25%  | 3%         | 13%            | 8%              |

| 2011 | 3%         | 78%             | 43%              | 20%  | 1%         | 9%             | 8%              |

| 2012 | 3%         | 41%             | 57%              | 19%  | 5%         | 12%            | 8%              |

| 2013 | 3%         |                 | 36%              | 13%  | 3%         | 6%             | 7%              |

| 2014 | 4%         |                 | 29%              | 16%  | 6%         | 6%             | 8.5%            |

| 2015 | 1%         | 28%             | 9%               | 17%  | 3%         | 14%            | 7.9%            |

|      |            |                 |                  |      |            |                |                 |

|      |            |                 |                  |      | - 8        | nnual decrease | annual increase |

Figure 1.1 (a) Energy consumption (unit of quadrillion Btu) in world by energy source from 1990-2040.[1] (b) Annual percentage change of cumulative global electricity capacity by source.[5]

Overall success for PV uptake depends on the cost (\$/kWh) to the consumer, which is not currently cheaper than conventional energy sources. However, over the last decade, the market has observed a significant reduction in PV prices [6, 7]. The cost is estimated by 'cost per peak watt ( $\$/W_p$ )' which encompasses both the module cost and costs related to installation [8].

Currently,  $\$/W_p$  is ~1 or ~0.10 \$/kWh, which is close to the average grid electricity cost in the US [8]. In fact, 20 states in US have achieved grid parity (i.e., comparable cost to grid electricity using conventional energy sources) [9]. However, achieving grid parity alone is not sufficient to replace the fossil fuels conventionally used for electricity production. Therefore, development of strong infrastructure is necessary to encourage widespread uptake of PV in addition to cost reduction.

In fact, PV related costs need to be reduced to at least half or one-third of the current rate (i.e., down to ~ 0.05 to 0.03 \$/kWh, Figure 1.2) for significant uptake of PV modules in the current energy production landscape [8]. Figure 1.2 effectively shows the relationship between module cost (\$/m²), power conversion efficiency (PCE, %) and production cost (\$/kWh). Within this context, current technologies suffer due to low efficiency and high cost of modules. A significant reduction in module cost can offset the efficiency demand and vice versa.

Figure 1.2. Relationship between power conversion efficiency, module costs per area and cost per peak watt ( $\$/W_p$ ). Decreasing the module cost can facilitate use of lower efficiency cells but higher module cost can be tolerated if the module efficiency can be substantially increased.[8]

Hence, the PV community is actively developing and implementing 'third generation' approaches [10, 11] targeted towards achieving PV modules that cost 0.03-0.05 \$/kWh. Historically, the 'first generation' of PV technology is based on single crystal Silicon (Si) wafers and this technology eventually matured and achieved a record efficiency of 25.6 % in a laboratory set-up [11]. Continued research and development is occurring to push the PCE towards the Shockley-Queisser limit for Si (33.5%) [2, 8, 10, 12]. It is well known that when any technology matures the overall cost is limited by the inherent materials cost [10]. A study on Si PVs for high volume production (500 MW/year) showed that 70% of the overall manufacturing cost is due to the material cost of Si [10]. Thus, the 'second generation' PVs based on thin film deposition techniques was developed.

Currently substantial activity is occurring for the design of 'third generation' approaches which rely on advanced thin film deposition techniques in combination with different innovative approaches [11, 13]. The aim of 'third generation' techniques is to reduce the overall PV cost and facilitate a widespread addition of PV capacity [8, 10, 11]. The 'third generation' approaches seek to achieve two main goals: (a) reduction of total cost by substantially decreasing materials cost and (b) increasing the efficiency of the PV modules beyond the Shockley-Quiesser limit in case of single junction devices [8, 11].

It is worth mentioning that PV modules based on single crystal Si still has ~90% of the total PV market share [14]. However, one of the major disadvantages of using Si PVs is the cost of manufacturing Si wafers with superior electronic properties [14]. Additionally, Si is an indirect band gap material (Band gap,  $E_g$ = 1.12 eV corresponding to an absorption cut-off at 1160 nm) which results in poor light absorption, specifically in the longer wavelength region.

Therefore, Si wafers with thickness of ~200 µm are necessary for complete light absorption, setting a severe lower limit for cost reduction [15]. It has been reported that the calculated inherent PCE of a Si PV module can reach 29.4% for an optimum Si thickness of 110 µm [14]. Therefore, materials cost will play a significant role even after achieving a PCE close to the Shockley-Quiesser limit. This constitutes a substantial roadblock for continued use of Si PV devices despite more than 40 years of strong manufacturing development. The implementation of a 'third generation' approach is therefore mandatory. The next section describes an approach that takes advantage of the electronic properties of Si and its mature manufacturing processes and adds a photonic element to address the photon absorption component of the devices, thus circumventing the issue associated with inherent material cost.

## 1.2 Concept of nanocrystal quantum dot (NQD)-Si hybrid photovoltaics

A widely applied alternative approach to reduce cost (\$/kWh) has been the utilization of advancements in thin film deposition techniques. Amorphous Si (a-Si) has been widely studied within this context. However, thin films of a-Si have been limited to a PCE of 10% despite cheap and low energy deposition techniques [11]. Band gap engineering has been widely investigated as a 'third generation' approach to increase the band gap of crystalline Si by embedding quantum wells (QWs) or quantum dots (QDs) of Si inside a Si-based dielectric such as oxides, nitrides or carbides [11]. This approach has resulted in the fabrication tandem cell with the QWs or QDs as the top cell and a thin film of crystalline Si as the bottom cell [11]. These reported techniques capitalize on the advances in thin film Si processing.

However, another equally innovative 'third generation' approach is based on separating PV functionalities into two different components (1) a photonic element for light absorption and

(2) a crystalline, semiconductor element for charge generation and collection. Nanocrystal quantum dots (NQDs) are used as the photonic element (i.e., absorber material) and Si thin films are used as the charge generation-collection material. The generation of charges in the Si thin film is achieved through excitonic energy transfer (ET) mechanisms. This is in contrast with conventional PV devices which are based on charge transfer (CT) mechanism. ET is inherently different from CT which uses the same material for both absorption and carrier transportation. In ET based devices, effective sensitization results in carrier generation due to the efficient electromagnetic interaction between the NQDs and Si. This unique approach harnesses the tunable absorption property of NQDs (particularly in the near-infrared region) and maintains the superior carrier generation-transportation property of the Si [16, 17]. Overall, the approach provides a pathway to overcome the severe lower limit of thickness that results from weak absorption in Si at longer wavelengths. Therefore, ET based sensitization of thin film crystalline Si can significantly reduce materials cost.

This dissertation is focused on this concept of ET based sensitization of Si by NQD for solar cell applications. In 2009, Lu and Madhukar [17] proposed the idea of separating optical and electrical functionalities for the application in a solar cell. The basic design principle of an ET based NQD-Si hybrid system is shown in Figure 1.3. Here, 'coupling' of the NQDs and Si via Near-field electromagnetic interaction is key to combine the clearly separated functionalities inside a PV device. NQDs absorb incident solar light and an excited electron-hole pair (exciton) is created, which is bound inside NQD by Coulombic attraction. This bound electron-hole pair (exciton) can transfer energy to the underlying high-mobility Si channel where carriers are generated and collected. The absorbed energy is transferred to Si by near-field electromagnetic

interaction between NQD and Si. There are two modes of energy transfer, namely non-radiative energy transfer (NRET) and radiative energy transfer (RET) [18]. So, optimization of these two modes is crucial for energy management from NQD towards Si. The ET modes are discussed in chapter 2. However, ET based NQD- Si hybrid PV devices relax the strict demands needed for producing efficient charge separation in the conventional devices such as homojunction and heterojunction PVs as well as organic PVs.

Figure 1.3. Schematic drawing showing the concept of ET based NQD-Si hybrid solar cell in a planar configuration. Size gradient NQD layers cover the solar spectrum. Absorbed energy is cascaded towards Si through different ET modes such as non-radiative energy transfer (NRET) and radiative energy transfer (RET).

ET based NQD-Si hybrid PVs has the potential to significantly reduced Si thickness requirements from  $\sim 200~\mu m$ . In fact, optimization of ET from different sizes of NQDs can potentially reduce Si thickness to  $<1~\mu m$ . Thereby materials cost can be reduced substantially. Also, the PV modules can be flexible with the development of ultrathin devices. Within this context, it is essential to fully understand the effectiveness of ET mechanisms inside an industrially relevant PV device architecture. Systematic study and correct quantification of ET-generated carriers will help to rationally design different PV structures. Then, the devices can be

optimally engineered for maximum carrier generation in Si. Furthermore, understating the hybrid system from charge generation perspective can help to incorporate new absorber materials and innovative nanostructured geometries. This dissertation addresses the core issue of finding the electrical viability of ET-generated carrier contribution inside a working PV system. Overall, the studies test different PV architectures to provide a systematic route for electrical characterization.

# 1.3 Dissertation organization

This dissertation has six chapters and is organized in the following way to provide a coherent flow facilitating logical progression of the study.

- Chapter 1 describes the importance and relevance of renewable energy, particularly solar energy, in the context of the recent energy landscape. This introduction lays the foundation and motivation behind the undertaken study. The scope of solar energy in terms of economic impact is also discussed. Later, the concept of energy transfer (ET) based nanocrystal quantum dot (NQD) sensitization of Si is briefly explained.

- Chapter 2 provides theoretical background with comprehensive literature review. This chapter provides important references relevant to this study which is essential for a detailed understanding of the project. Also, the working principle of a solar cell and the extraction of basic parameters from the I-V graph is briefly discussed.

- Chapter 3 outlines the experimental methods used in this work. Different deposition techniques such as low pressure chemical vapor deposition (LPCVD), plasma enhanced chemical vapor deposition (PECVD) and electron-beam evaporation are discussed.

Plasma processing for etching, and characterization methods (scanning electron microscope, atomic force microscopy, spectroscopic ellipsometry, reflectance measurements, profilometery, four-point probe measurements) are briefly discussed. Additionally, the electrical characterization of solar cells via current-voltage (I-V) and external quantum efficiency (EQE) measurements are described.

- Chapter 4 presents the results for the NQD sensitization of bulk Si solar cells via ET. This chapter is central to the development of chapter 5. The method for quantifying ET-generated carriers is described in this chapter. Bulk Si solar cells sensitized by CdSe/ZnS NQDs are used as test PV system to understand the origin of PV enhancement after NQD deposition.

- Chapter 5 discusses the design approach for fabricating ultrathin (300 nm) Si solar cells.

Mechanical and structural roadblocks for fabricating such a fragile structure are identified and subsequently optimized to improve yield. Once fabricated, the solar cells are characterized electrically. Overall, the chapter provides detailed steps for the fabrication of ultrathin Si PV devices with the possibility of incorporating NQDs in the finished structure.

- Chapter 6 summarizes the outcomes and provides future direction to circumvent problems faced during this dissertation. This chapter proposes different approaches that can be investigated to improve the processing of ultrathin Si solar cells and provides guidelines for incorporating NQDs into the structures.

#### **CHAPTER 2**

#### THEORETICAL BACKGROUND AND LITERATURE REVIEW

Contents related to energy transfer mechanisms to Si of this chapter have been adapted with permission from Weina Peng, Sara M. Rupich, Natis Shafiq, Yuri N. Gartstein, Anton V. Malko and Yves J. Chabal, *Silicon surface modification for emergent photovoltaic applications based on energy transfer*, Chemical Reviews, 115 (23), Copyright 2015 American Chemical Society [19]. I acknowledge the major contribution from all the other authors and re-use some of the paragraphs as a co-author. Sections and sub-sections 2.1, 2.1.1, 2.1.2 were taken fully from the paper with minor modifications such as correcting the figure numbers as per the organization of the dissertation. Readers are encouraged to study the theoretical consideration from this review article which is relevant for understanding the theoretical framework of the energy transfer mechanism to Si substrates. The paper also discusses photocurrent measurements and different deposition techniques for NQDs. Readers are suggested to consult the paper for detailed information.

After providing the background on ET, section 2.2 briefly introduces the working principle of a solar cell (SC) and the important parameters. This work uses SCs as a test structure for NQD sensitization. Thus, a brief overview is provided in this section and introduces (with appropriate references) the working principles of SCs. Readers are encouraged to consider references provided therein to study further.

### 2.1 Energy transfer (ET) mechanism

The main focus of this section is on the mechanisms of ET into Si from neighboring photoexcited quantum emitters such as colloidal NQDs. We distinguish non-radiative ET (NRET) and radiative ET (RET) [20] as qualitatively different contributions to the overall ET enabled by near-field electromagnetic interactions [18, 21-23]. Dexter [24] was probably the first to explicitly suggest the idea of external NRET sensitization of inorganic semiconductors for PV applications. The NRET mechanism is akin to the familiar Förster ET (with the usual acronym FRET) enabled by dipole-dipole interaction between neighboring molecular species and depending on the spectral overlap of the energy donor emission and energy acceptor absorption spectra [25-27]. The NRET process can be thought of as direct excitation [28] of the electronhole pairs in a semiconductor by the electric field of the decaying emitter excitons. While the NRET mechanism is more frequently discussed in the literature for ET-hybrids [16, 17, 29-33], the potential significance of RET should not be overlooked as its relative contributions can vary depending on both the distance between the emitter and acceptor and on the spectral range considered [18, 23]. In the RET process, the emitter's exciton preferentially decays into photonic modes that can propagate only within the energy-accepting semiconductor, that is waveguide modes in spatially-confined semiconductor layers and wires [34]. These propagating modes would eventually be absorbed to produce electron-hole pairs contributing to the electric current. The effective conversion of the incoming solar plane-wave photons, via re-emission from a relaxed localized exciton, into waveguide modes may be compared to the effect from scattering processes achievable with metallic and dielectric structures judiciously patterned to increase the incident light absorption in thin semiconductor layers [35, 36].

# 2.1.1 Determination of NRET efficiencies from nanocrystal quantum dots to semiconductor Substrates

The field of ET between molecular absorbers or semiconductor NQDs and various semiconductor surfaces for the purpose of photovoltaic light harvesting has seen something of resurgence in the past few years. Particularly, GaAs and silicon surfaces have been employed in order to improve efficiencies of the existing technologically important solar cells, where GaAs-based structures pertain to very high-efficiency (and possibly multi-junction) cells while Si structures are thought to become more efficient in the thin film geometries. Clear illustrations of the viability of the energy transfer-based concepts first started to emerge in experimental studies of NQDs on GaAs substrates, in which the NRET efficiency was predicted to be substantial thanks to the large absorption coefficient of GaAs arising from its direct band gap transitions.

The efficiencies of ET can be measured via time- and spectrally- resolved PL spectroscopy. This technique is a valuable tool that can be used to monitor the presence and dynamical behavior of correlated electrons and holes in semiconductor media and is extensively described in a number of books [37, 38]. During the ET process, the emission of the donor molecule or NQD is quenched while the emission of the acceptor molecule is enhanced. The degree of the quenching/enhancement provides a quantitative measure of the ET efficiency. However, this ratiometric appoach is not always reliable. A more precise approach is to monitor changes in the PL dynamics of a donor in the presence of an acceptor.

NRET from near-infrared active PbS NQDs emitting at ~ 965 nm to buried InGaAs quantum wells was shown by Lu *et al.* [16]. Quantum wells made from short-period superlattices were buried about 3 nm below the sulfur-passivated GaAs surface. A drop-cast layer of NQDs

was deposited on the top of the structure, with (approximately 8 nm separating the monolayer and quantum wells. To eliminate charge carrier feeding by electron-hole pairs generated in the substrate, the excitation wavelength was set to 910 nm. The authors observed about a 35% reduction in the NQD PL intensity as compared to the reference substrate without buried quantum wells. Additionally, the average PL decay time decreased from 298 ns on GaAs to 208 ns on the buried well structure as seen in Figure 2.1. Based on these measurements, the authors estimated a non-radiative transfer decay time of ~690 ns compared with the radiative decay time of 960 ns for the PbS NQDs. That corresponds to ~30% non-radiative transfer efficiency to the quantum wells from these NQDs. Another important achievement was a demonstration of NRET-induced photocurrent in GaAs patterned quantum wells sensitized with CdSe/ZnS NQDs [33].

By comparison of the PL decay times, the authors estimated the efficiency of NRET from NQDs to the proximal semiconductor surface to be 79%. Additionally, photocurrent measurements revealed a six-fold enhancement for the patterned hybrid devices when compared to the reference *p-i-n* structure. From the data, the authors concluded that approximately 89% of the exciton energy was transferred into the quantum wells via NRET from the proximal NQDs. They also noted that such hybrid configurations are not limited to using NQDs as energy donors, but should also be applicable to other strongly absorbing, solution-based materials.

Figure 2.1. (a) Time-resolved PL of PbS NQDs on passviated GaAs (blue) and on passivated near surface quantum wells (red), excited at 900 nm (below GaAs bandgap) and detected at 965 nm (PbS PL peak). The decay of the TRPL curves are fitted using a stretched exponential function. (b) Schematic showing an architecture comprising NQD absorbers embedded in a vertical array of high-mobility channels that allow nonradiative transfer of excitons from the adjacent NQDs and simultaneously provide high-mobility transport.[16]

The studies mentioned above were based on NQDs that were drop-cast onto semiconductor surfaces. In such situations, unprepared interfaces might have a substantial number of surface trapping sites that will facilitate exciton dissociation and subsequent charge trapping. This is especially important when time-resolved photoluminescence (TRPL) dynamics are recorded as a method of choice to register NRET signatures – faster dynamics of the emitting donor (NQD or molecule) species indicate an energy transfer channel. However, any other non-radiative channels such as interface charge trapping would similarly affect dynamics, thus hindering NRET effects. Further, drop casting does not allow for uniform layer deposition, thus providing for a multitude of the donor-acceptor distances, complicating interpretation of the PL lifetimes. Recently, several publications have achieved controllable positioning of monolayers of NQDs on Si surfaces, thus allowing for a quantitative determination of the elemental transfer rates. Nguyen et al. [21] discussed NRET from a monolayer of CdSe/ZnS NQDs controllably

grafted on a SAM-passivated Si surface. TRPL measurements revealed a progressive shortening of the PL lifetime of the donor NQDs as the separation from the acceptor Si surface decreased with ~1/d³ dependence, confirming its dipole-dipole origin. The calculated NRET efficiency at 565 nm reached 65% with an interaction distance of about 4.4 nm. Extension of NRET to the near-infrared wavelength range was accomplished in Nimmo *et al.* [23], where a monolayer of CdSe or CdTeSe NQDs emitting between 545-800 nm was similarly grafted on thw Si surface. There, efficiency of NRET was found to decrease from ~70% to <50%, mostly owning to lower absorption of Si at longer wavelengths, as seen in Figure 2.2.

Figure 2.2. (a) PL emission spectra of different NQDs emitting from 545 to 800 nm as grafted on  $SiO_2$ . NQDs on Si exhibit the same PL profile. (b) Schematics of energy transfer from NQDs emitting at different wavelength to Si substrate. (c) Total ET efficiency ( $E_{total}$ ) shown by black squares along with separate contributions  $E_{NRET}$  from NRET (red circles) and  $E_{RET}$  from RET (blue triangles).[23]

We would like to note that precise measurements of NRET rates were possible due to the fact that NQDs were grafted within a monolayer on the substrate, thus avoiding complications in the PL lifetime signatures that arise from a distribution of distances and associated NRET rates. Later on, another study of NRET was performed by Andreakou *et al.* [31] who drop casted PbS NQDs emitting at ~ 900 nm and obtained transfer efficiency estimated at 44%.

# 2.1.2 Radiative energy transfer to Si substrates

In addition to purely electrostatic dipole-dipole interaction that constitutes the NRET process, RET was experimentally demonstrated to be operative and very efficient across a wide wavelength range. This process involves the coupling of the donors' emission into the waveguide modes of the high-refractive-index semiconductor substrate. Nguyen et al. [18] used a monolayer of CdSe/ZnS NQDs grafted on thin Si nanomembranes (SiNM) of different thickness t = 25-300nm and varied the distance to Si as shown in Figure 2.3 (c). The PL lifetimes were observed to exhibit oscillating behavior as a function of the SiNM thickness as a result of the PL coupling to various waveguide modes (Figure 2.3 (a), (b)). The maximum RET coupling efficiency was observed for a SiNM thickness of 75 nm that corresponds to the half wavelength of the donor emission (vacuum emission wavelength  $\lambda_0$ =565 nm) within the Si material. Overall, the ET efficiency to the SiNM was found to be around 90%, for the minimum NQD-to-Si separation (d=4.4 nm), whereas the NRET efficiency was 58% and the RET 29%. The relative effects of these contributions were reversed at larger separation distances, due to the much larger effective length of the RET interaction ( $d\sim0.1\lambda_0$ ). At d=12.6 m, the RET and NRET efficiencies were 52% and 21%, respectively, while at d=18.6 nm, the RET efficiency was 57.5% and the NRET efficiency was only 5.5%. These results clearly indicate that 1) RET coupling is a major, longdistance mechanism contributing to the overall ET and 2) the total ET to very thin SiNMs can be as effective as into bulk Si, but not at the expense of the latter.